FPGA设计入门简述.docx

《FPGA设计入门简述.docx》由会员分享,可在线阅读,更多相关《FPGA设计入门简述.docx(11页珍藏版)》请在冰豆网上搜索。

FPGA设计入门简述

FPGA设计入门简述

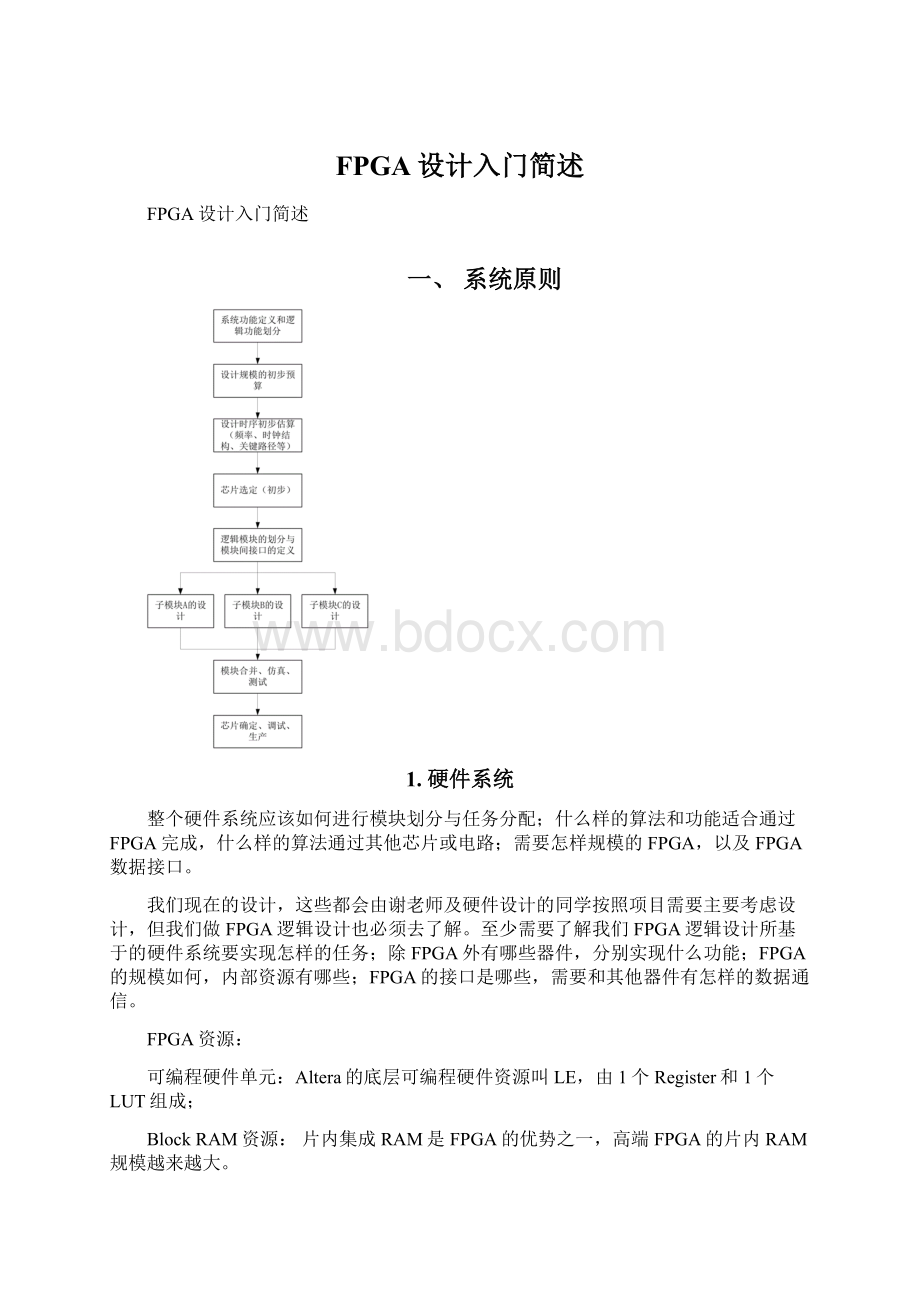

一、系统原则

1.硬件系统

整个硬件系统应该如何进行模块划分与任务分配;什么样的算法和功能适合通过FPGA完成,什么样的算法通过其他芯片或电路;需要怎样规模的FPGA,以及FPGA数据接口。

我们现在的设计,这些都会由谢老师及硬件设计的同学按照项目需要主要考虑设计,但我们做FPGA逻辑设计也必须去了解。

至少需要了解我们FPGA逻辑设计所基于的硬件系统要实现怎样的任务;除FPGA外有哪些器件,分别实现什么功能;FPGA的规模如何,内部资源有哪些;FPGA的接口是哪些,需要和其他器件有怎样的数据通信。

FPGA资源:

可编程硬件单元:

Altera的底层可编程硬件资源叫LE,由1个Register和1个LUT组成;

BlockRAM资源:

片内集成RAM是FPGA的优势之一,高端FPGA的片内RAM规模越来越大。

布线资源:

布线资源用以连接不同的硬件单元,根据用途不同,布线资源的工艺、速度、驱动能力都不同。

可配置IO单元:

了解器件可以支持的IO标准;

时钟资源:

DLL、PLL;

(片上处理器等硬核、高速串行收发器。

)

2.FPGA设计的宏观安排

模块化设计是系统原则的一个很好的体现,它不仅仅是一种设计工具,它更是一种设计思路、设计方法,它是由顶向下、模块划分、分工协作设计思路的集中体现。

结构层次化编码

结构层次化编码是模块化设计思想的一种体现。

结构层次化编码可以提高代码的可读性,易于模块划分,易于分工协作,易于设计仿真测试激励。

✧结构的层次不要太深,一般为3到5层即可。

✧顶层模块最好仅仅包含对所有模块的组织和调用,而不应该完成比较复杂的逻辑功能。

较为合理的顶层模块由输入输出管脚声明、模块的调用与实例化、全局时钟资源、全局置位/复位、三态缓冲和一些简单的组合逻辑等构成。

✧子某块之间可以有接口,但不能有子模块间跨层次的接口。

✧子模块的合理划分非常重要,应该综合考虑子模块的功能、结构、时序、复杂度等多方面因素。

模块划分的技巧

✧对每个同步时序设计的子模块输出使用寄存器。

✧将相关的逻辑和可以复用的逻辑划分在同一模块内(呼应系统原则)。

✧将不同优化目标的逻辑分开。

(speed/area)

✧将存储逻辑独立划分成模块。

二、面积和速度的互换与平衡

“面积”(area)指设计所消耗FPGA的逻辑资源的数量,可以用消耗的寄存器(Registor)和查找表(LUT)来衡量。

“速度”(speed)指设计在芯片上稳定运行所能达到的最高频率。

面积和速度是设计质量评价的指标。

互换:

一个设计如果时序余量较大,所能跑得频率远远高于设计要求,那么就能通过功能模块服用减少整个设计消耗的芯片面积,这就是用速度优势换取面积节约;反之,如果一个设计的时序要求很高,普通方法达不到设计频率,那么一般可以通过将数据流串并转换,并行复制多个操作模块,对整个设计采取“乒乓操作”和“串并转换”的思想进行运作,在芯片输出模块再对数据进行“并串变换”,从宏观上看芯片满足了处理速度的要求,相当于用面积消耗换取速度提高。

平衡:

面积和速度是一对对立统一的矛盾体,我们需要平衡好二者的关系。

可以是在面积一定的情况下,使设计的时序余量更大,频率跑得更高;或者是满足一定的时序要求,占用最小的芯片面积。

举例:

“乒乓操作”

乒乓操作最大的特点是,通过“输入数据选择单元”按节拍、相互配合的切换,将经过缓冲的数据流没有时间停顿的送到“数据流运算处理模块”,被运算与处理。

常常运用于流水线式算法,完成数据的无缝缓冲与处理。

通过运用乒乓操作,用低速模块处理高速数据流(以面积换取速度)。

假设A端输入数据流的速率为100Mb/s,乒乓操作的缓冲周期是10ms。

在第一个缓冲周期10ms内,通过“输入数据选择单元”,从B1到达RAM1。

B1的数据速率也是100Mb/s,在10ms内,RAM1写入1Mb数据。

同理在第二个10ms,数据流被切换到RAM2,端口B2的数据速率也是100Mb/s,RAM2在第二个10ms被写入1MB的数据。

在第三个缓冲周期,RAM1可以获得20ms的时间用于读取数据并送到“数据与数理模块1”。

端口C1的数据流可以是50Mb/s,即数据预处理模块的吞吐能力也可以仅仅要求为50Mb/s。

通过乒乓操作实现低速模块处理高速数据的实质是:

通过缓存单元,实现了数据流的串并转换,并行使用多个处理模块,是面积与速度互换的一个体现。

串并转换

串并转换的实现方法多种多样,根据数据的排序和数量的要求,可以选用寄存器、RAM等实现。

流水线操作

流水线设计的一个关键在于:

整个设计时序的合理安排、前后级接口间数据流速的匹配。

每个操作步骤的划分必须合理,要统筹考虑各个操作步骤间的数据流量。

如果前几操作时间恰好等于后继操作的时间,前级输出直接汇入后级的输入。

如果前级操作时间小于后级的操作时间,则需要对前级的输出数据适当缓存,才能汇入后级,还必须注意数据速率的匹配,防止后级数据的一处。

如果前级操作时间大于后级的操作时间,则必须通过逻辑复制、串并转换等手段将数据分流,或者在前级对数据采用存储、后处理方式,否则会造成与后级的处理节拍不匹配。

流水线处理方式之所以频率比较高,是因为复制了处理模块,它是面积换取速度思想的有一种体现。

三、硬件原则

FPGA设计采用硬件描述语言(HDL)与软件语言有本质的区别,硬件描述语言的本质在于对硬件的描述,所以我们在设计的时候要考虑不同的描述综合之后硬件电路的区别。

For循环语句

For循环会被综合其展开为所有变量情况的执行语句,每个变量独立占用资源,每条执行语句不能有效地服用硬件逻辑资源,造成浪费。

推荐方式:

先搞清楚设计的时序要求,做一个reg型计数器,在每个时钟沿累加,并在每个时钟沿判断计数器情况,做相应的处理,能够复用的操作尽量使用复用。

即使所有操作不能服用,也采用case语句展开处理。

for(i=1;i<16;i++)

DoSomething();

reg[3:

0]counter;

always@(posedgeclk)

if(syn_rst)

counter<=0;

else

counter<=counter+1;

always@(posdgeclk)

begin

case(counter)

4’b0000:

4’b0001:

……

Default:

end

Case和ifelse的优先级

一般来说case语句是“平行”的结构,所有的case的条件和执行都没有“优先级”。

而“if…else”大多数情况是有优先级。

而建立优先级(优先级树)会消耗大量的组合逻辑,如果能够使用case语句的地方,推荐使用case替换if…else结构。

阻塞赋值和非阻塞赋值

阻塞赋值“=”:

在这个语句没有执行完之前,后面的语句是不执行的。

非阻塞赋值“<=”:

所有的语句可以并发执行,而前面的值是否执行完毕不会影响后面的语句。

always@(a,b)

begin

b=a;

c=b;

end

always@(posedgeclk)

begin

b<=a;

c<=b;

end

RAM等存储单元的使用

与RAM等存储单元相关的资源有三类:

BlockRAM、LUT、Register,这三种资源都可以被综合实现为RAM等存储单元。

1.使用RAM等存储单元时,应该首选BlockRAM;

2.弄清FPGA的硬件结构,合理使用BlockRAM;

3.分析BlockRAM容量,高效使用BlockRAM。

比如Stratix/StratixGX等系列FPGA中有一种叫TriMatrixMemory的BlockRAM构架,在芯片中内嵌了三种不同大小的RAM块,分别是:

M512(512Bits)、M4k(4kBits)、M-RAM(512kBits),三种BlockRAM有不同的构架,等效到每kBit的端口数量也不同。

DDR的使用与验证

DDRSDRAM全称为DoubleDataRateSDRAM,中文名为“双倍数据流SDRAM”。

DDR读操作时序图

DDR芯片接口定义

DDR的容量、位宽、逻辑BANK

L-Bank存储阵列示意图

DDR的突发长度

突发(Burst)是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输所涉及到存储单元(列)的数量就是突发长度(BurstLengths,简称BL)。

读/写操作,都是一次对一个存储单元进行寻址,如果要连续读/写就还要对当前存储单元的下一个单元进行寻址,也就是要不断的发送列地址与读/写命令(行地址不变,所以不用再对行寻址)。

虽然由于读/写延迟相同可以让数据的传输在I/O端是连续的,但它占用了大量的内存控制资源,在数据进行连续传输时无法输入新的命令,效率很低(早期的FPE/EDO内存就是以这种方式进行连续的数据传输)。

为此,人们开发了突发传输技术,只要指定起始列地址与突发长度,内存就会依次地自动对后面相应数量的存储单元进行读/写操作而不再需要控制器连续地提供列地址。

这样,除了第一笔数据的传输需要若干个周期(主要是之前的延迟,一般的是tRCD+CL)外,其后每个数据只需一个周期的即可获得。

非突发连续读取模式:

不采用突发传输而是依次单独寻址,此时可等效于BL=1。

虽然可以让数据是连续的传输,但每次都要发送列地址与命令信息,控制资源占用极大

突发连续读取模式:

只要指定起始列地址与突发长度,寻址与数据的读取自动进行,而只要控制好两段突发读取命令的间隔周期(与BL相同)即可做到连续的突发传输

数据掩码

在讲述读/写操作时,我们谈到了突发长度。

如果BL=4,那么也就是说一次就传送4×64bit的数据。

但是,如果其中的第二笔数据是不需要的,怎么办?

还都传输吗?

为了屏蔽不需要的数据,人们采用了数据掩码(DataI/OMask,简称DQM)技术。

通过DQM,内存可以控制I/O端口取消哪些输出或输入的数据。

这里需要强调的是,在读取时,被屏蔽的数据仍然会从存储体传出,只是在“掩码逻辑单元”处被屏蔽。

DQM由北桥控制,为了精确屏蔽一个P-Bank位宽中的每个字节,每个DIMM有8个DQM信号线,每个信号针对一个字节。

这样,对于4bit位宽芯片,两个芯片共用一个DQM信号线,对于8bit位宽芯片,一个芯片占用一个DQM信号,而对于16bit位宽芯片,则需要两个DQM引脚。

SDRAM官方规定,在读取时DQM发出两个时钟周期后生效,而在写入时,DQM与写入命令一样是立即成效。

读取时数据掩码操作,DQM在两个周期后生效,突发周期的第二笔数据被取消

写入时数据掩码操作,DQM立即生效,突发周期的第二笔数据被取消

四、同步设计原则

异步电路:

电路的核心逻辑用组合逻辑电路实现;电路的主要信号,输出信号等并不依赖于任何一个时钟性信号;最大的缺点是容易产生毛刺。

同步时序:

电路的核心逻辑用各种各样的触发器实现;电路的主要信号,输出信号等都是由某个时钟沿驱动触发器产生出来的;同步时序电路可以很好地避免毛刺。

同步时序电路的时钟产生

为了获得高驱动能、低抖动时延、稳定的占空比的时钟信号,一般使用FPGA内部的专用时钟资源产生同步时序电路的主工作时钟。

专用时钟资源主要指两部分:

一部分是布线资源,包括全局时钟不限资源,和长线资源等;另一部分是FPGA内部的DLL或者PLL。

输入信号的同步

同步时序电路要求对输入信号进行同步化,同步化的主要作用是使本级时钟的处理沿获得相对于数据的最长有效处理时间,从而获得更长的时间余量。

✧输入输出的延时不可测,或者有可能变动

✧数据是有固定格式安排的,很多重要信息在数据的起始位置

✧上级数据和本级时钟是异步的,也就是说上级芯片或模块和本级芯片或模块的时钟是异步时钟域的

✧设计数据接口同步时添加约束

✧模块输出信号同步

举例:

serdes(altgx的使用)

加扰->打包->发送接收->同步检测->解包->解扰

Serdes简介:

串行收发器SERDES(SERializer&DESerializer)顾名思义,由两部分构成:

发送端是串行发送单元SERializer,用高速时钟调制编码数据流;接收端为串行接收单元DESerializer,其中要作用是从数据流中恢复出时钟信号,并解调还原数据。

对比并行数据传输和串行数据传输:

并行数据传输:

多根线占用板面积;

每根线之间有干扰;

每根线需要自己的匹配电路。

串行数据传输:

更少的走线占用板面积减少;

信号线的干扰降到最小;

相对于并行传输只用了一小部分的匹配电路;

没有相位差问题。