毕业设计外文翻译89C51单片机.docx

《毕业设计外文翻译89C51单片机.docx》由会员分享,可在线阅读,更多相关《毕业设计外文翻译89C51单片机.docx(9页珍藏版)》请在冰豆网上搜索。

毕业设计外文翻译89C51单片机

毕业设计外文翻译--89C51单片机

TheDescriptionofAT89S51

1GeneralDescription

TheAT89S51isalow-power,high-performanceCMOS8-bitmicrocontrollerwith4KbytesofIn-SystemProgrammableFlashmemory.ThedeviceismanufacturedusingAtmel’shigh-densitynonvolatilememorytechnologyandiscompatiblewiththeindustry-standard80C51instructionsetandpinout.Theon-chipFlashallowstheprogrammemorytobereprogrammedin-systemorbyaconventionalnonvolatilememoryprogrammer.Bycombiningaversatile8-bitCPUwithIn-SystemProgrammableFlashonamonolithicchip,theAtmelAT89S51isapowerfulmicrocontrollerwhichprovidesahighly-flexibleandcost-effectivesolutiontomanyembeddedcontrolapplications.

TheAT89S51providesthefollowingstandardfeatures:

4KbytesofFlash,128bytesofRAM,32I/Olines,Watchdogtimer,twodatapointers,two16-bittimer/counters,afive-vectortwo-levelinterruptarchitecture,afullduplexserialport,on-chiposcillator,andclockcircuitry.Inaddition,theAT89S51isdesignedwithstaticlogicforoperationdowntozerofrequencyandsupportstwosoftwareselectablepowersavingmodes.

TheIdleModestopstheCPUwhileallowingtheRAM,timer/counters,serialport,andinterruptsystemtocontinuefunctioning.ThePower-downmodesavestheRAMcontentsbutfreezestheoscillator,disablingallotherchipfunctionsuntilthenextexternalinterruptorhardwarereset.

2Ports

Port0isan8-bitopendrainbi-directionalI/Oport.Asanoutputport,eachpincansinkeightTTLinputs.When1sarewrittentoport0pins,thepinscanbeusedashigh-impedanceinputs.Port0canalsobeconfiguredtobethemultiplexedlow-orderaddress/databusduringaccessestoexternalprogramanddatamemory.Inthismode,P0hasinternalpull-ups.Port0alsoreceivesthecodebytesduringFlashprogrammingandoutputsthecodebytesduringprogramverification.Externalpull-upsarerequiredduringprogramverification.

Port1isan8-bitbi-directionalI/Oportwithinternalpull-ups.ThePort1outputbufferscansink/sourcefourTTLinputs.When1sarewrittentoPort1pins,theyarepulledhighbytheinternalpull-upsandcanbeusedasinputs.Asinputs,Port1pinsthatareexternallybeingpulledlowwillsourcecurrent(IIL)becauseoftheinternalpull-ups.

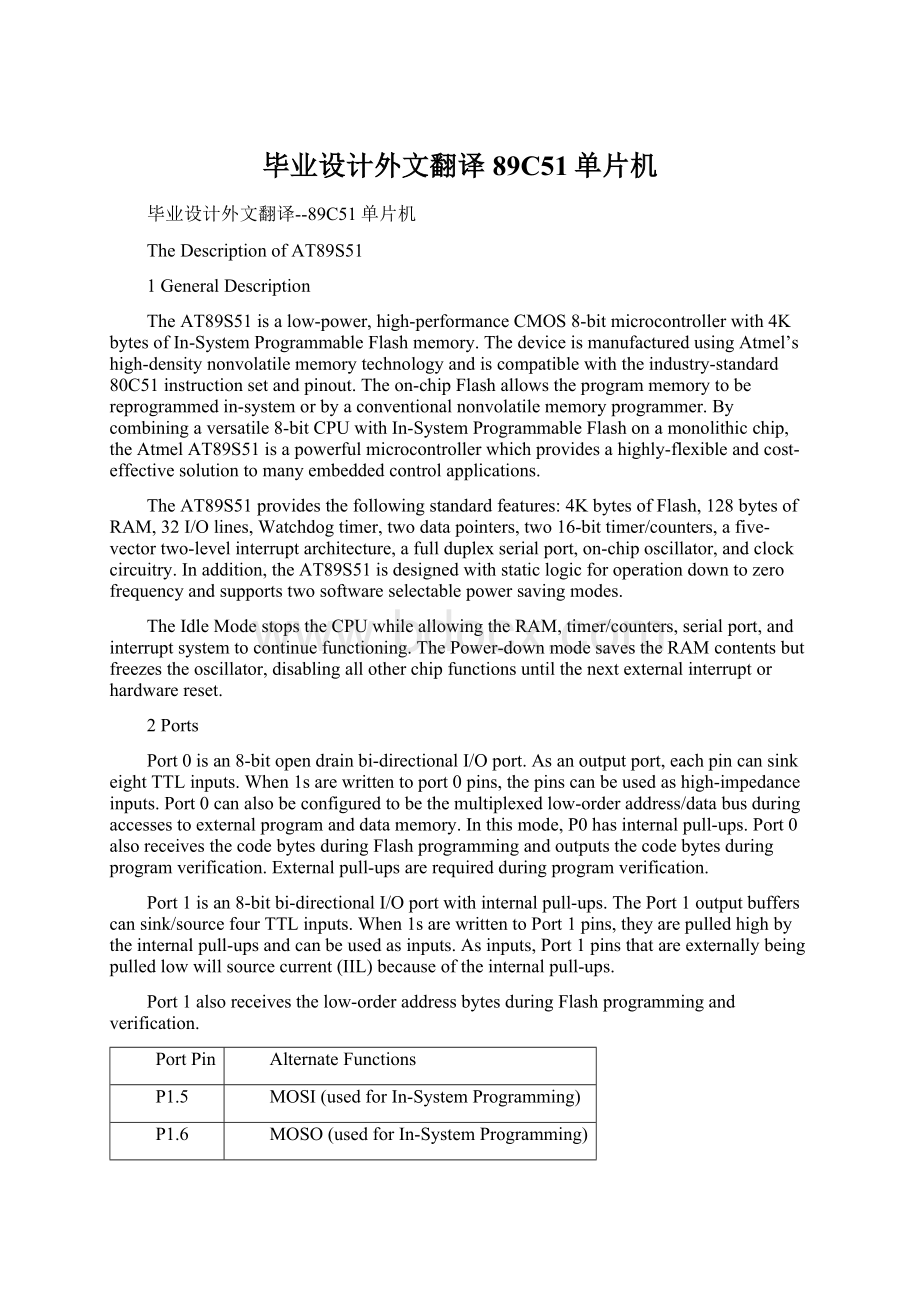

Port1alsoreceivesthelow-orderaddressbytesduringFlashprogrammingandverification.

PortPin

AlternateFunctions

P1.5

MOSI(usedforIn-SystemProgramming)

P1.6

MOSO(usedforIn-SystemProgramming)

P1.7

SCK(usedforIn-SystemProgramming)

Port2isan8-bitbi-directionalI/Oportwithinternalpull-ups.ThePort2outputbufferscansink/sourcefourTTLinputs.When1sarewrittentoPort2pins,theyarepulledhighbytheinternalpull-upsandcanbeusedasinputs.Asinputs,Port2pinsthatareexternallybeingpulledlowwillsourcecurrent(IIL)becauseoftheinternalpull-ups.Port2emitsthehigh-orderaddressbyteduringfetchesfromexternalprogrammemoryandduringaccessestoexternaldatamemorythatuse16-bitaddresses(MOVX@DPTR).Inthisapplication,Port2usesstronginternalpull-upswhenemitting1s.Duringaccessestoexternaldatamemorythatuse8-bitaddresses(MOVX@RI),Port2emitsthecontentsoftheP2SpecialFunctionRegister.Port2alsoreceivesthehigh-orderaddressbitsandsomecontrolsignalsduringFlashprogrammingandverification.

Port3isan8-bitbi-directionalI/Oportwithinternalpull-ups.ThePort3outputbufferscansink/sourcefourTTLinputs.When1sarewrittentoPort3pins,theyarepulledhighbytheinternalpull-upsandcanbeusedasinputs.Asinputs,Port3pinsthatareexternallybeingpulledlowwillsourcecurrent(IIL)becauseofthepull-ups.Port3receivessomecontrolsignalsforFlashprogrammingandverification.Port3alsoservesthefunctionsofvariousspecialfeaturesoftheAT89S51,asshowninthefollowingtable.

PortPin

AlternateFunctions

P3.0

RXD(serialinputport)

P3.1

TXD(serialoutputport)

P3.2

INT0(externalinterrupt0)

P3.3

INT1(externalinterrupt1)

P3.4

T0(timer0externalinput)

P3.5

T1(timer1externalinput)

P3.6

WR(externaldatamemorywritestrobe)

P3.7

RD(externaldatamemoryreadstrobe)

3MemoryOrganization

MCS-51deviceshaveaseparateaddressspaceforProgramandDataMemory.Upto64KbyteseachofexternalProgramandDataMemorycanbeaddressed.

3.1ProgramMemory

IftheEApinisconnectedtoGND,allprogramfetchesaredirectedtoexternalmemory.OntheAT89S51,ifEAisconnectedtoVCC,programfetchestoaddresses0000HthroughFFFHaredirectedtointernalmemoryandfetchestoaddresses1000HthroughFFFFHaredirectedtoexternalmemory.

3.2DataMemory

TheAT89S51implements128bytesofon-chipRAM.The128bytesareaccessibleviadirectandindirectaddressingmodes.Stackoperationsareexamplesofindirectaddressing,sothe128bytesofdataRAMareavailableasstackspace.

4WatchdogTimer(One-timeEnabledwithReset-out)

TheWDTisintendedasarecoverymethodinsituationswheretheCPUmaybesubjectedtosoftwareupsets.TheWDTconsistsofa14-bitcounterandtheWatchdogTimerReset(WDTRST)SFR.TheWDTisdefaultedtodisablefromexitingreset.ToenabletheWDT,ausermustwrite01EHand0E1HinsequencetotheWDTRSTregister(SFRlocation0A6H).WhentheWDTisenabled,itwillincrementeverymachinecyclewhiletheoscillatorisrunning.TheWDTtimeoutperiodisdependentontheexternalclockfrequency.ThereisnowaytodisabletheWDTexceptthroughreset(eitherhardwareresetorWDToverflowreset).WhenWDToverflows,itwilldriveanoutputRESETHIGHpulseattheRSTpin.

4.1UsingtheWDT

ToenabletheWDT,ausermustwrite01EHand0E1HinsequencetotheWDTRSTregister(SFRlocation0A6H).WhentheWDTisenabled,theuserneedstoserviceitbywriting01EHand0E1HtoWDTRSTtoavoidaWDToverflow.The14-bitcounteroverflowswhenitreaches16383(3FFFH),andthiswillresetthedevice.WhentheWDTisenabled,itwillincrementeverymachinecyclewhiletheoscillatorisrunning.ThismeanstheusermustresettheWDTatleastevery16383machinecycles.ToresettheWDTtheusermustwrite01EHand0E1HtoWDTRST.WDTRSTisawrite-onlyregister.TheWDTcountercannotbereadorwritten.WhenWDToverflows,itwillgenerateanoutputRESETpulseattheRSTpin.TheRESETpulsedurationis98xTOSC,whereTOSC=1/FOSC.TomakethebestuseoftheWDT,itshouldbeservicedinthosesectionsofcodethatwillperiodicallybeexecutedwithinthetimerequiredtopreventaWDTreset.

4.2WDTDURINGPower-downandIdle

InPower-downmodetheoscillatorstops,whichmeanstheWDTalsostops.WhileinPower-downmode,theuserdoesnotneedtoservicetheWDT.TherearetwomethodsofexitingPower-downmode:

byahardwareresetorviaalevel-activatedexternalinterrupt,whichisenabledpriortoenteringPower-downmode.WhenPower-downisexitedwithhardwarereset,servicingtheWDTshouldoccurasitnormallydoeswhenevertheAT89S51isreset.ExitingPower-downwithaninterruptissignificantlydifferent.Theinterruptisheldlowlongenoughfortheoscillatortostabilize.Whentheinterruptisbroughthigh,theinterruptisserviced.TopreventtheWDTfromresettingthedevicewhiletheinterruptpinisheldlow,theWDTisnotstarteduntiltheinterruptispulledhigh.ItissuggestedthattheWDTberesetduringtheinterruptservicefortheinterruptusedtoexitPower-downmode.ToensurethattheWDTdoesnotoverflowwithinafewstatesofexitingPower-down,itisbesttoresettheWDTjustbeforeenteringPower-downmode.BeforegoingintotheIDLEmode,theWDIDLEbitinSFRAUXRisusedtodeterminewhethertheWDTcontinuestocountifenabled.TheWDTkeepscountingduringIDLE(WDIDLEbit=0)asthedefaultstate.TopreventtheWDTfromresettingtheAT89S51whileinIDLEmode,theusershouldalwayssetupatimerthatwillperiodicallyexitIDLE,servicetheWDT,andreenterIDLEmode.

WithWDIDLEbitenabled,theWDTwillstoptocountinIDLEmodeandresumesthecountuponexitfromIDLE.

5.Interrupts

TheAT89S51hasatotaloffiveinterruptvectors:

twoexternalinterrupts(INT0andINT1),twotimerinterrupts(Timers0and1),andtheserialportinterrupt.TheseinterruptsareallshowninFigure6-1.EachoftheseinterruptsourcescanbeindividuallyenabledordisabledbysettingorclearingabitinSpecialFunctionRegisterIE.IEalsocontainsaglobaldisablebit,EA,whichdisablesallinterruptsatonce.

6OscillatorCharacteristics

XTAL1andXTAL2aretheinputandoutput,respectively,ofaninvertingamplifierthatcanbeconfiguredforuseasanon-chiposcillator,asshowninFigure7-1.Eitheraquartzcrystalorceramicresonatormaybeused.Todrivethedevicefromanexternalclocksource,XTAL2shouldbeleftunconnectedwhileXTAL1isdriven,asshowninFigure7-2.Therearenorequirementsonthedutycycleoftheexternalclocksignal,sincetheinputtotheinternalclockingcircuitryisthroughadivide-by-twoflip-flop,butminimumandmaximumvoltagehighandlowtimespecificationsmustbeobserved.

7IdleMode

Inidlemode,theCPUputsitselftosleepwhilealltheon-chipperipheralsremainactive.Themodeisinvokedbysoftware.Thecontentoftheon-chipRAMandallthespecialfunctionregistersremainunchangedduringthismode.Theidlemodecanbeterminatedbyanyenabledinterruptorbyahardwarereset.

Notethatwhenidlemodeisterminatedbyahardwarereset,thedevicenormallyresumespro-gramexecutionfromwhereitleftoff,uptotwomachinecyclesbeforetheinternalresetalgorithmtakescontrol.On-chiphardwareinhibitsaccesstointe