集成电路基础试验cadence反相器设计.docx

《集成电路基础试验cadence反相器设计.docx》由会员分享,可在线阅读,更多相关《集成电路基础试验cadence反相器设计.docx(8页珍藏版)》请在冰豆网上搜索。

集成电路基础试验cadence反相器设计

题目:

反相器分析与设计

姓名:

白进宝

学院:

微电子与固体电子学院

学号:

0523

签名:

/諛二

教师签名:

摘要

CMOS指互补金属氧化物(PMOS管和NMOS管)共同构成的互补型MOS集成电路制造丄艺,它的特点是低功耗。

山于CMOS中一对MOS组成的门电路在瞬间看,要么PMOS导通,要么NMOS导通,要么都截至,比线性的三极管(BJT)效率要高得多,因此功耗很低。

本次设计的是反相器,通过电路搭建前仿真,实现其功能。

然后进行版图设计,提取寄生参数后进项后仿真。

关键词:

CMOS、反相器、低功耗、集成电路版图

1、技术指标要求

:

100um:

:

大于1GHz

:

功耗与电源电压、工作速度、负载等诸多因素有关。

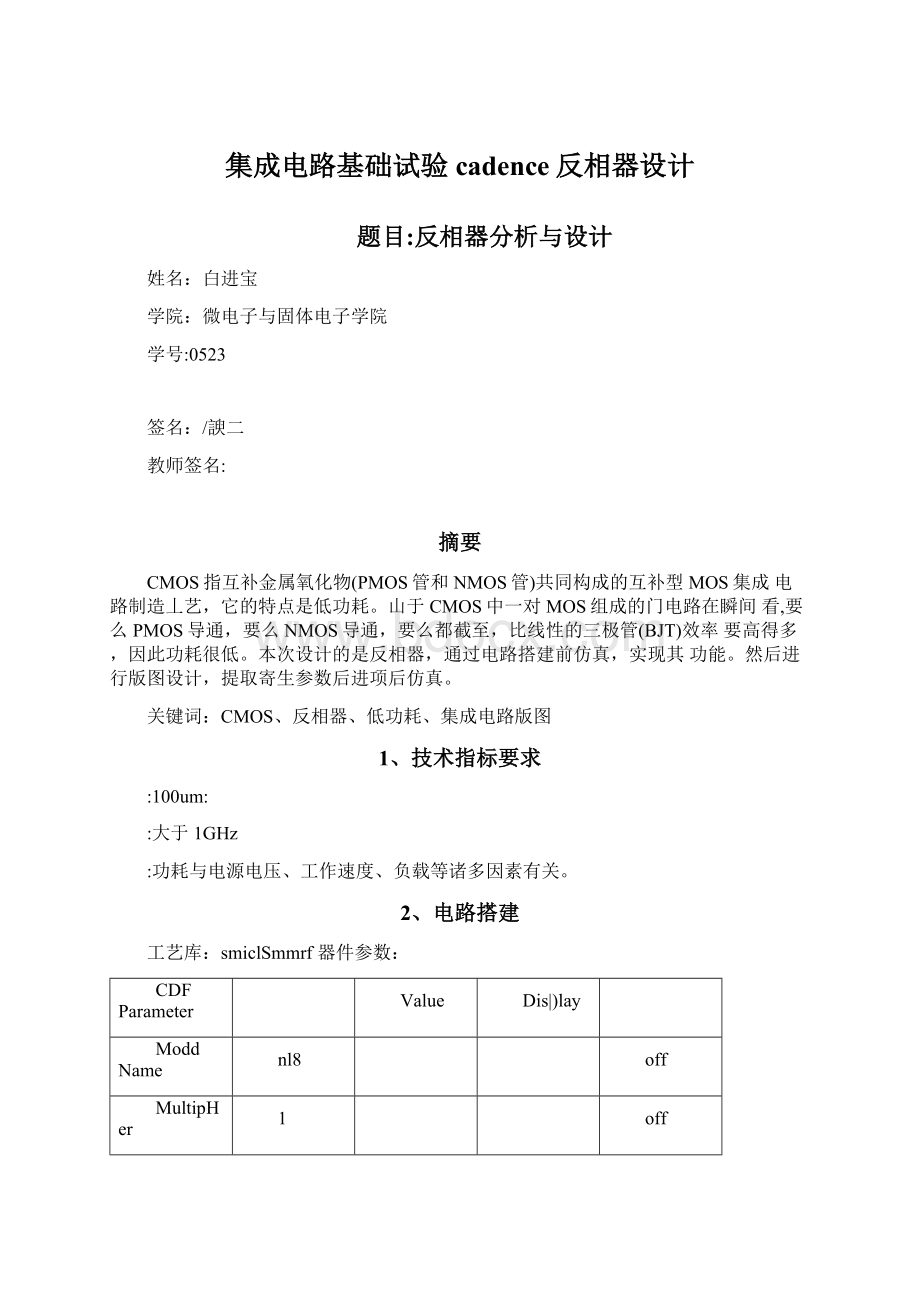

2、电路搭建

工艺库:

smiclSmmrf器件参数:

CDFParameter

Value

Dis|)lay

ModdName

nl8

off

MultipHer

1

off

180nK

off;

TotalVAdth

220nM.

o仃-

FingerWidth

220nii.

Off_i|

Fingers

on

Threshold

220n耳

off

CDFParameter

Vahie

Display

ModolName

pl8

Multiplier

1

LetiflW

lSOnB

TotalWidth

880nK

RngerV/ldUi

220n«

fingers

I

Hircshoki

220n«

设置NMOS与PMOS宽长比。

电路结构:

vdc=_)in

p18P比

-'I•l_w=880i|

n18

l:

180n

mil

II

NMIyrrn18rrw:

220nI0-^l:

180nTm:

1

p18PM

>、w=B80ii

OUT

18・

1:

180口

m:

1

NM2"rd刘・v^:

220n

0-Jl:

180n

m:

1

500

0

-50.0

.5

10

20

dC(V)

200-

150

如图,电路结构。

有两级反相器组成,第二级为负载,因为在实际电路中电路都是带载的。

250

an)Ok

00

50.0-1

-LOOH

-L50H

-2OOH

-25O-F

0.0

分别作NMOS和PMOS的直流输出特性曲线,NMOS的阈值电圧大约为左右,PMOS的阈值电压大约为左右。

3、仿真

(i)进行直流传输特性仿真分析

图一电源电压为5V,图二电源电压为2V。

可以看到图二的特性比图一好,这是山于降低的电压,从而使特性变好。

继续降低电源电压为IV后,特性更好。

但是当降到200mV时,特性反而变差。

这是山于当电压降到接近于阈值电压或更低时,管子无法导通,性能变差。

(2)瞬态特性分析

O

1£f

将时间轴拉长,可以看到当输出反向时,存在一个过冲现象,这是山于栅漏电容造成。

(3)工作频率分析

上图为反相器没有带负载的情况下测岀的下降时间,下图为带一个反相器测出的下降时间。

从而我们可以得出电路的扇出越多,性能越差,所以在数字电路中,我们尽量将扇岀控制在4以内。

更多的扇出将通过组合电路多级实现。

山图可得上升时间为,下降时间为。

工作频率=1/(2Xmax(上升时间,下降时间))=17GHz

(4)功耗分析

如以上两幅图,分别在电源电压5V和2V的情况下动态电流分析。

5V时电流峰值为1mA左右,2V时电流峰值为300uA左右。

4、版图

版图设计是将模拟优化后的电路转化成一系列儿何图形,这些儿何图形包含了集成电路尺寸大小、各层拓扑定义等有关元件的物理信息。

5、后仿真

以上两幅图为后仿真的交流仿真图。

山图可得上升时间为,下降时间为。

工作频率=1/(2Xmax(上升时间,下降时间))显然画出版图提取寄生参数后性能变差,工作频率变小。

左图为前仿真的直流输出特性曲线,右图为后仿真的直流输出特性曲线,通过对比可以看出,两者区别不大。

6.对比技术指标完成情况

(1)工作速度。

前仿真的速度为17GNz,后仿真的速度为6GHz,设计指标为IGNzo

(2)面积。

版图的面积为200un)S设计指标为1OOum2,与设计指标有一定差距。

(3)功耗。

降低电源电压可以降低功耗,通过以上仿真可以看出电压由3V变为2V后动态电流也急剧下降。

减小输入信号的上升下降时间也可以降低功耗。

7、总结

本次设计大反相器部分指标达到了设计要求,部分没有达到设计要求。

(1)在直流传输特性分析中减小电压能一定程度上提高性能。

但是当降到200mV时,特性反而变差。

这是山于当电压降到接近于阈值电压或更低时,管子

无法导通,性能变差C

(2)在进行动态仿真时,当输出反向时,存在一个过冲现象,这是由于栅漏电容造成,是山于器件本身的寄生参数造成的。

在降低电压的同时这个过冲现象就会越来越明显。

(3)进行直流传输特性仿真分析时,降低电压从而使特性变好。

继续降低电源电压为IV后,特性更好。

但是当降到200mV时,特性反而变差。

从NMOS和PMOS的直流输出特性曲线看出NMOS的阈值电压大约为左右,PMOS的阈值电压大约为左右。

当电压降到接近于阈值电压或更低时,管子无法导通,性能变差。

(4)电路的扇出越多,性能越差,所以在数字电路中,我们尽量将扇出控制在4以内。

更多的扇出将通过组合电路多级实现。