从CPU内部一级二级三级缓存存储器容量变化来看存储器技术发展.docx

《从CPU内部一级二级三级缓存存储器容量变化来看存储器技术发展.docx》由会员分享,可在线阅读,更多相关《从CPU内部一级二级三级缓存存储器容量变化来看存储器技术发展.docx(9页珍藏版)》请在冰豆网上搜索。

从CPU内部一级二级三级缓存存储器容量变化来看存储器技术发展

兰州大学信息科学与工程学院

从CPU内部一级二级三级缓存存储器容量变化来看存储器技术发展

黄来君

2012/5/6

从CPU内部一级二级三级缓存存储器容量变化来看存储器技术发展

目录:

1、简介

2、工作原理

3、各级缓存详解

4、技术发展

5、总结

一、简介

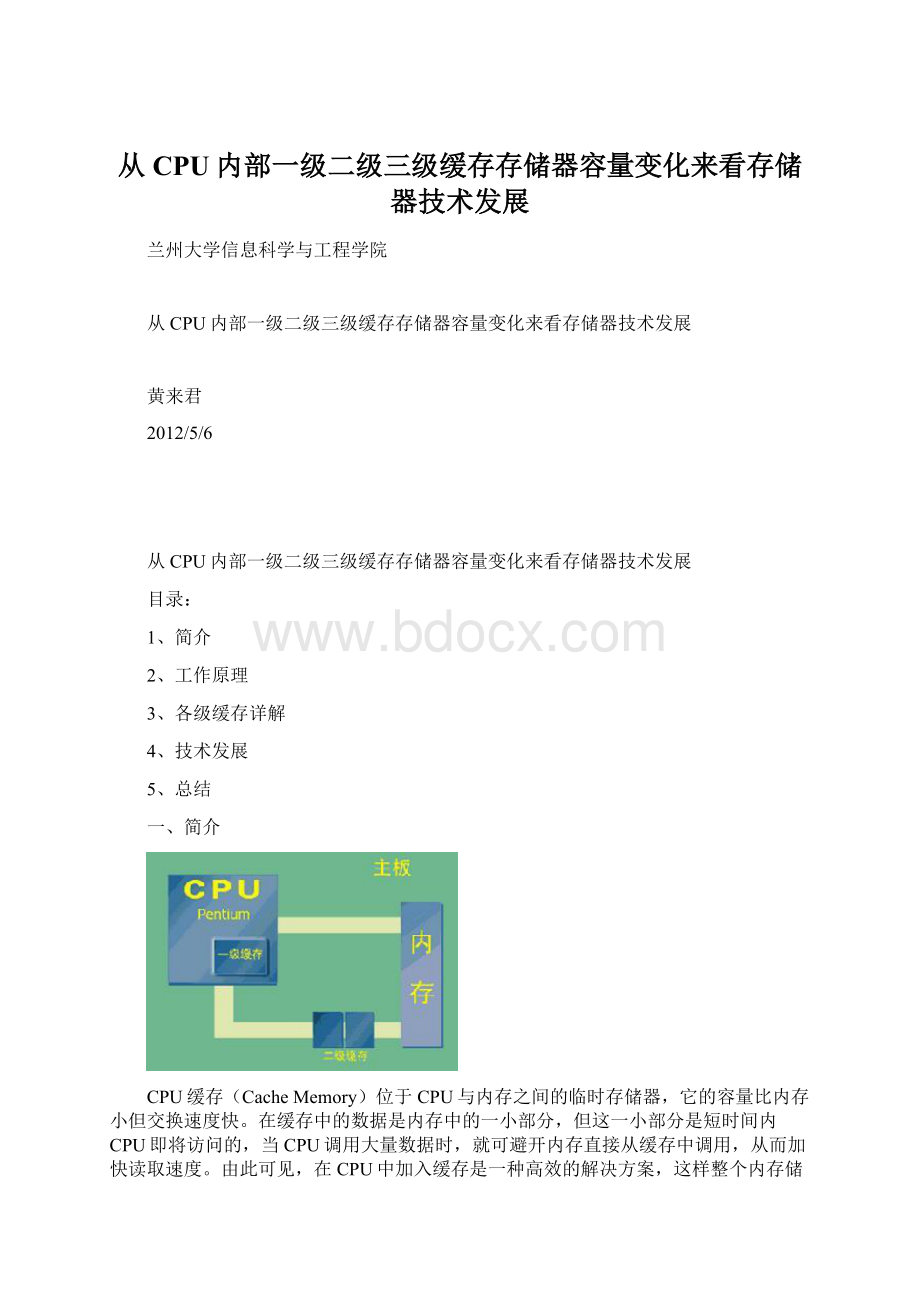

CPU缓存(CacheMemory)位于CPU与内存之间的临时存储器,它的容量比内存小但交换速度快。

在缓存中的数据是内存中的一小部分,但这一小部分是短时间内CPU即将访问的,当CPU调用大量数据时,就可避开内存直接从缓存中调用,从而加快读取速度。

由此可见,在CPU中加入缓存是一种高效的解决方案,这样整个内存储器(缓存+内存)就变成了既有缓存的高速度,又有内存的大容量的存储系统了。

缓存对CPU的性能影响很大,主要是因为CPU的带宽引起的。

缓存是为了解决CPU速度和内存速度的速度差异问题。

内存中被CPU访问最频繁的数据和指令被复制入CPU中的缓存,这样CPU就可以不经常到象“蜗牛”一样慢的内存中去取数据了,CPU只要到缓存中去取就行了,而缓存的速度要比内存快很多。

(图一)

二、工作原理

CPU缓存(CacheMemory)是位于CPU与内存之间的临时存储器,它的容量比内存小的多但是交换速度却比内存要快得多。

缓存的出现主要是为了解决CPU运算速度与内存读写速度不匹配的矛盾,因为CPU运算速度要比内存读写速度快很多,这样会使CPU花费很长时间等待数据到来或把数据写入内存。

在缓存中的数据是内存中的一小部分,但这一小部分是短时间内CPU即将访问的,当CPU调用大量数据时,就可避开内存直接从缓存中调用,从而加快读取速度。

由此可见,在CPU中加入缓存是一种高效的解决方案,这样整个内存储器(缓存+内存)就变成了既有缓存的高速度,又有内存的大容量的存储系统了。

缓存对CPU的性能影响很大,主要是因为CPU的数据交换顺序和CPU与缓存间的带宽引起的。

缓存的工作原理是当CPU要读取一个数据时,首先从缓存中查找,找到就立即读取并送给CPU处理;没有找到,就用相对慢的速度从内存中读取并送给CPU处理,同时把这个数据所在的数据块调入缓存中,可以使得以后对整块数据的读取都从缓存中进行,不必再调用内存。

正是这样的读取机制使CPU读取缓存的命中率非常高(大多数CPU可达90%左右),也就是说CPU下一次要读取的数据90%都在缓存中,只有大约10%需要从内存读取。

这大大节省了CPU直接读取内存的时间,也使CPU读取数据时基本无需等待。

总的来说,CPU读取数据的顺序是先缓存后内存。

缓存基本上都是采用SRAM存储器,SRAM是英文StaticRAM的缩写,它是一种具有静态存取功能的存储器,不需要刷新电路即能保存它内部存储的数据。

不像DRAM内存那样需要刷新电路,每隔一段时间,固定要对DRAM刷新充电一次,否则内部的数据即会消失,因此SRAM具有较高的性能,但是SRAM也有它的缺点,即它的集成度较低,相同容量的DRAM内存可以设计为较小的体积,但是SRAM却需要很大的体积,这也是不能将缓存容量做得太大的重要原因。

它的特点归纳如下:

优点是节能、速度快、不必配合内存刷新电路、可提高整体的工作效率,缺点是集成度低、相同的容量体积较大、而且价格较高,只能少量用于关键性系统以提高效率。

按照数据读取顺序和与CPU结合的紧密程度,CPU缓存可以分为一级缓存,二级缓存,部分高端CPU还具有三级缓存,每一级缓存中所储存的全部数据都是下一级缓存的一部分,这三种缓存的技术难度和制造成本是相对递减的,所以其容量也是相对递增的。

当CPU要读取一个数据时,首先从一级缓存中查找,没有找到再从二级缓存中查找,还是没有就从三级缓存或内存中查找。

一般来说,每级缓存的命中率大概都在80%左右,也就是说全部数据量的80%都可以在一级缓存中找到,只剩下20%的总数据量才需要从二级缓存、三级缓存或内存中读取,由此可见一级缓存是整个CPU缓存架构中最为重要的部分。

(图二)

三、各级缓存详解

<一>、一级缓存cache1

一级缓存(Level1Cache)简称L1Cache,位于CPU内核的旁边,是与CPU结合最为紧密的CPU缓存,也是历史上最早出现的CPU缓存。

由于一级缓存的技术难度和制造成本最高,提高容量所带来的技术难度增加和成本增加非常大,所带来的性能提升却不明显,性价比很低,而且现有的一级缓存的命中率已经很高,所以一级缓存是所有缓存中容量最小的,比二级缓存要小得多。

一级缓存可以分为一级数据缓存(DataCache,D-Cache)和一级指令缓存(InstructionCache,I-Cache)。

二者分别用来存放数据以及对执行这些数据的指令进行即时解码,而且两者可以同时被CPU访问,减少了争用Cache所造成的冲突,提高了处理器效能。

大多数CPU的一级数据缓存和一级指令缓存具有相同的容量,例如AMD的AthlonXP就具有64KB的一级数据缓存和64KB的一级指令缓存,其一级缓存就以64KB+64KB来表示,其余的CPU的一级缓存表示方法以此类推。

Intel的采用NetBurst架构的CPU(最典型的就是Pentium4)的一级缓存有点特殊,使用了新增加的一种一级追踪缓存(ExecutionTraceCache,T-Cache或ETC)来替代一级指令缓存,容量为12KμOps,表示能存储12K条即12000条解码后的微指令。

一级追踪缓存与一级指令缓存的运行机制是不相同的,一级指令缓存只是对指令作即时的解码而并不会储存这些指令,而一级追踪缓存同样会将一些指令作解码,这些指令称为微指令(micro-ops),而这些微指令能储存在一级追踪缓存之内,无需每一次都作出解码的程序,因此一级追踪缓存能有效地增加在高工作频率下对指令的解码能力,而μOps就是micro-ops,也就是微型操作的意思。

它以很高的速度将μops提供给处理器核心。

IntelNetBurst微型架构使用执行跟踪缓存,将解码器从执行循环中分离出来。

这个跟踪缓存以很高的带宽将uops提供给核心,从本质上适于充分利用软件中的指令级并行机制。

Intel并没有公布一级追踪缓存的实际容量,只知道一级追踪缓存能储存12000条微指令(micro-ops)。

所以,不能简单地用微指令的数目来比较指令缓存的大小。

实际上,单核心的NetBurst架构CPU使用8Kμops的缓存已经基本上够用了,多出的4kμops可以大大提高缓存命中率。

而要使用超线程技术的话,12KμOps就会有些不够用,这就是为什么有时候Intel处理器在使用超线程技术时会导致性能下降的重要原因。

例如Northwood核心的一级缓存为8KB+12KμOps,就表示其一级数据缓存为8KB,一级追踪缓存为12KμOps;而Prescott核心的一级缓存为16KB+12KμOps,就表示其一级数据缓存为16KB,一级追踪缓存为12KμOps。

在这里12KμOps绝对不等于12KB,单位都不同,一个是μOps,一个是Byte(字节),而且二者的运行机制完全不同。

所以那些把Intel的CPU一级缓存简单相加,例如把Northwood核心说成是20KB一级缓存,把Prescott核心说成是28KB一级缓存,并且据此认为Intel处理器的一级缓存容量远远低于AMD处理器128KB的一级缓存容量的看法是完全错误的,二者不具有可比性。

在架构有一定区别的CPU对比中,很多缓存已经难以找到对应的东西,即使类似名称的缓存在设计思路和功能定义上也有区别了,此时不能用简单的算术加法来进行对比;而在架构极为近似的CPU对比中,分别对比各种功能缓存大小才有一定的意义。

(图三)

<二>、二级缓存

二级缓存(Level2cache),它是处理器内部的一些缓冲存储器,其作用跟内存一样。

上溯到上个世纪80年代,由于处理器的运行速度越来越快,慢慢地,处理器需要从内存中读取数据的速度需求就越来越高了。

然而内存的速度提升速度却很缓慢,而能高速读写数据的内存价格又非常高昂,不能大量采用。

从性能价格比的角度出发,英特尔等处理器设计生产公司想到一个办法,就是用少量的高速内存和大量的低速内存结合使用,共同为处理器提供数据。

这样就兼顾了性能和使用成本的最优。

而那些高速的内存因为是处于cpu和内存之间的位置,又是临时存放数据的地方,所以就叫做缓冲存储器了,简称“缓存”。

它的作用就像仓库中临时堆放货物的地方一样,货物从运输车辆上放下时临时堆放在缓存区中,然后再搬到内部存储区中长时间存放。

货物在这段区域中存放的时间很短,就是一个临时货场。

最初缓存只有一级,后来处理器速度又提升了,一级缓存不够用了,于是就添加了二级缓存。

二级缓存是比一级缓存速度更慢,容量更大的内存,主要就是做一级缓存和内存之间数据临时交换的地方用。

为了适应速度更快的处理器p4ee,已经出现了三级缓存了,它的容量更大,速度相对二级缓存也要慢一些,但是比内存可快多了。

缓存的出现使得cpu处理器的运行效率得到了大幅度的提升,这个区域中存放的都是cpu频繁要使用的数据,所以缓存越大处理器效率就越高,同时由于缓存的物理结构比内存复杂很多,所以其成本也很高。

大量使用二级缓存带来的结果是处理器运行效率的提升和成本价格的大幅度不等比提升。

举个例子,服务器上用的至强处理器和普通的p4处理器其内核基本上是一样的,就是二级缓存不同。

至强的二级缓存是2mb~16mb,p4的二级缓存是512kb,于是最便宜的至强也比最贵的p4贵,原因就在二级缓存不同。

即l2cache。

由于l1级高速缓存容量的限制,为了再次提高cpu的运算速度,在cpu外部放置一高速存储器,即二级缓存。

工作主频比较灵活,可与cpu同频,也可不同。

cpu在读取数据时,先在l1中寻找,再从l2寻找,然后是内存,在后是外存储器。

所以l2对系统的影响也不容忽视。

最早先的cpu缓存是个整体的,而且容量很低,英特尔公司从pentium时代开始把缓存进行了分类。

当时集成在cpu内核中的缓存已不足以满足cpu的需求,而制造工艺上的限制又不能大幅度提高缓存的容量。

因此出现了集成在与cpu同一块电路板上或主板上的缓存,此时就把cpu内核集成的缓存称为一级缓存,而外部的称为二级缓存。

一级缓存中还分数据缓存(datacache,d-cache)和指令缓存(instructioncache,i-cache)。

二者分别用来存放数据和执行这些数据的指令,而且两者可以同时被cpu访问,减少了争用cache所造成的冲突,提高了处理器效能。

英特尔公司在推出pentium4处理器时,用新增的一种一级追踪缓存替代指令缓存,容量为12kμops,表示能存储12k条微指令。

随着cpu制造工艺的发展,二级缓存也能轻易的集成在cpu内核中,容量也在逐年提升。

再用集成在cpu内部与否来定义一、二级缓存,已不确切。

而且随着二级缓存被集成入cpu内核中,以往二级缓存与cpu大差距分频的情况也被改变,此时其以相同于主频的速度工作,可以为cpu提供更高的传输速度。

二级缓存分类:

(一)插在主板上的二级缓存

(图四)

(二)整合在CPU上的二级缓存

(图五)

(三)“胶水”式的二级缓存

(图六)

(四)整合进CPU内部的二级缓存

<三>、三级缓存

L3Cache(三级缓存),分为两种,早期的是外置,现在的都是内置的。

而它的实际作用即是,L3缓存的应用可以进一步降低内存延迟,同时提升大数据量计算时处理器的性能。

降低内存延迟和提升大数据量计算能力对游戏都很有帮助。

而在服务器领域增加L3缓存在性能方面仍然有显著的提升。

比方具有较大L3缓存的配置利用物理内存会更有效,故它比较慢的磁盘I/O子系统可以处理更多的数据请求。

具有较大L3缓存的处理器提供更有效的文件系统缓存行为及较短消息和处理器队列长度。

其实最早的L3缓存被应用在AMD发布的K6-III处理器上,当时的L3缓存受限于制造工艺,并没有被集成进芯片内部,而是集成在主板上。

在只能够和系统总线频率同步的L3缓存同主内存其实差不了多少。

后来使用L3缓存的是英特尔为服务器市场所推出的Itanium处理器。

接着就是P4EE和至强MP。

Intel还打算推出一款9MBL3缓存的Itanium2处理器,和以后24MBL3缓存的双核心Itanium2处理器。

但基本上L3缓存对处理器的性能提高显得不是很重要,比方配备1MBL3缓存的XeonMP处理器却仍然不是Opteron的对手,由此可见前端总线的增加,要比缓存增加带来更有效的性能提升。

例:

Corei7Die示意图

(图七)

四、技术发展

最早先的CPU缓存是个整体的,而且容量很低,英特尔公司从Pentium时代开始把缓存进行了分类。

当时集成在CPU内核中的缓存已不足以满足CPU的需求,而制造工艺上的限制又不能大幅度提高缓存的容量。

因此出现了集成在与CPU同一块电路板上或主板上的缓存,此时就把CPU内核集成的缓存称为一级缓存,而外部的称为二级缓存。

一级缓存中还分数据缓存(DataCache,D-Cache)和指令缓存(InstructionCache,I-Cache)。

二者分别用来存放数据和执行这些数据的指令,而且两者可以同时被CPU访问,减少了争用Cache所造成的冲突,提高了处理器效能。

英特尔公司在推出Pentium4处理器时,用新增的一种一级追踪缓存替代指令缓存,容量为12KμOps,表示能存储12K条微指令。

随着CPU制造工艺的发展,二级缓存也能轻易的集成在CPU内核中,容量也在逐年提升。

现在再用集成在CPU内部与否来定义一、二级缓存,已不确切。

而且随着二级缓存被集成入CPU内核中,以往二级缓存与CPU大差距分频的情况也被改变,此时其以相同于主频的速度工作,可以为CPU提供更高的传输速度。

二级缓存是CPU性能表现的关键之一,在CPU核心不变化的情况下,增加二级缓存容量能使性能大幅度提高。

而同一核心的CPU高低端之分往往也是在二级缓存上有差异,由此可见二级缓存对于CPU的重要性。

CPU在缓存中找到有用的数据被称为命中,当缓存中没有CPU所需的数据时(这时称为未命中),CPU才访问内存。

从理论上讲,在一颗拥有二级缓存的CPU中,读取一级缓存的命中率为80%。

也就是说CPU一级缓存中找到的有用数据占数据总量的80%,剩下的20%从二级缓存中读取。

由于不能准确预测将要执行的数据,读取二级缓存的命中率也在80%左右(从二级缓存读到有用的数据占总数据的16%)。

那么还有的数据就不得不从内存调用,但这已经是一个相当小的比例了。

目前的较高端的CPU中,还会带有三级缓存,它是为读取二级缓存后未命中的数据设计的—种缓存,在拥有三级缓存的CPU中,只有约5%的数据需要从内存中调用,这进一步提高了CPU的效率。

为了保证CPU访问时有较高的命中率,缓存中的内容应该按一定的算法替换。

一种较常用的算法是“最近最少使用算法”(LRU算法),它是将最近一段时间内最少被访问过的行淘汰出局。

因此需要为每行设置一个计数器,LRU算法是把命中行的计数器清零,其他各行计数器加1。

当需要替换时淘汰行计数器计数值最大的数据行出局。

这是一种高效、科学的算法,其计数器清零过程可以把一些频繁调用后再不需要的数据淘汰出缓存,提高缓存的利用率。

CPU产品中,一级缓存的容量基本在4KB到64KB之间,二级缓存的容量则分为128KB、256KB、512KB、1MB、2MB、4MB等。

一级缓存容量各产品之间相差不大,而二级缓存容量则是提高CPU性能的关键。

二级缓存容量的提升是由CPU制造工艺所决定的,容量增大必然导致CPU内部晶体管数的增加,要在有限的CPU面积上集成更大的缓存,对制造工艺的要求也就越高。

五、总结

CPU缓存(CacheMemory)位于CPU与内存之间的临时存储器,它的容量比内存小但交换速度快。

在缓存中的数据是内存中的一小部分,但这一小部分是短时间内CPU即将访问的,当CPU调用大量数据时,就可避开内存直接从缓存中调用,从而加快读取速度。

由此可见,在CPU中加入缓存是一种高效的解决方案,这样整个内存储器(缓存+内存)就变成了既有缓存的高速度,又有内存的大容量的存储系统了。