EDA计数器答案.docx

《EDA计数器答案.docx》由会员分享,可在线阅读,更多相关《EDA计数器答案.docx(12页珍藏版)》请在冰豆网上搜索。

EDA计数器答案

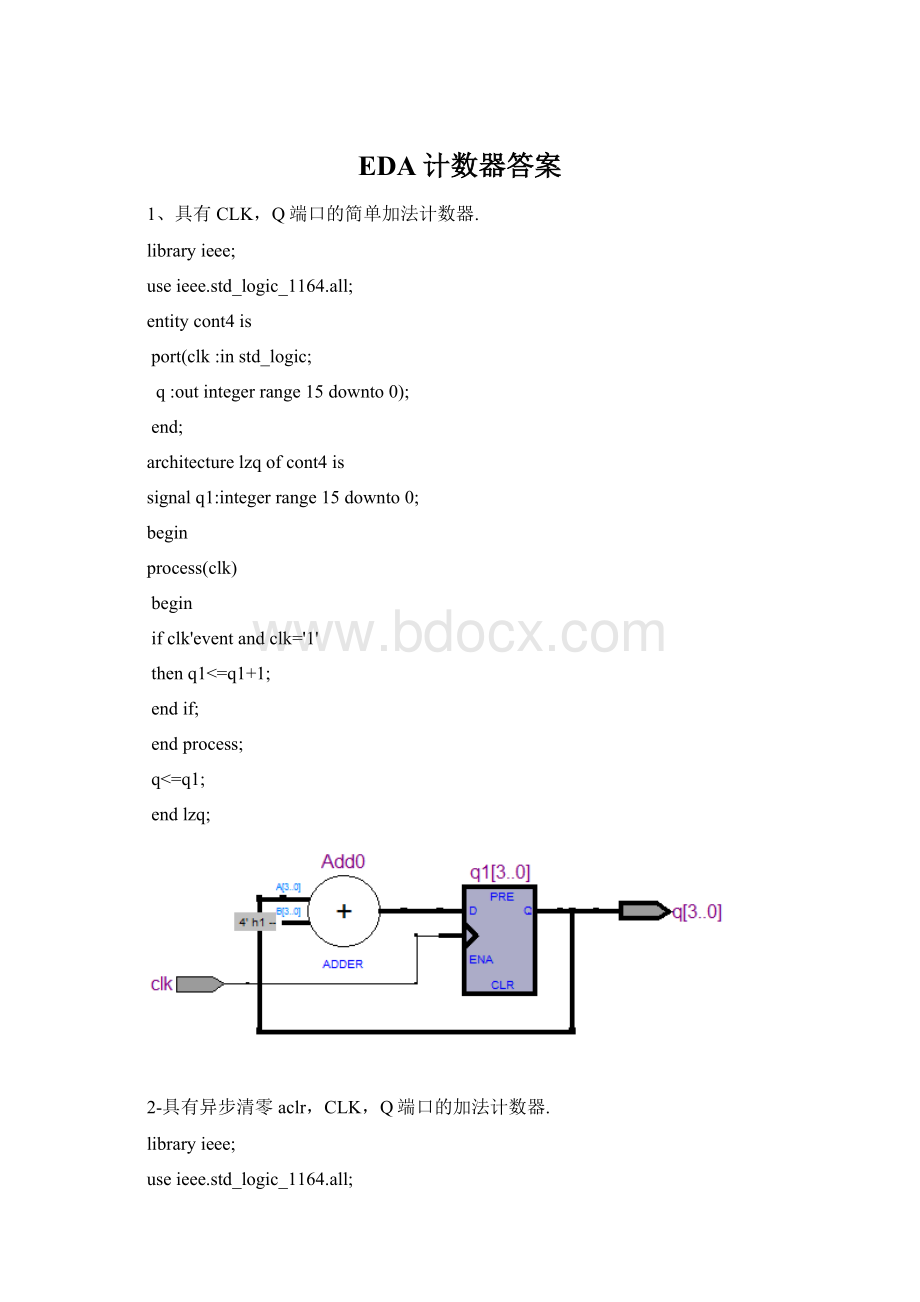

1、具有CLK,Q端口的简单加法计数器.

libraryieee;

useieee.std_logic_1164.all;

entitycont4is

port(clk:

instd_logic;

q:

outintegerrange15downto0);

end;

architecturelzqofcont4is

signalq1:

integerrange15downto0;

begin

process(clk)

begin

ifclk'eventandclk='1'

thenq1<=q1+1;

endif;

endprocess;

q<=q1;

endlzq;

2-具有异步清零aclr,CLK,Q端口的加法计数器.

libraryieee;

useieee.std_logic_1164.all;

entitycont4is

port(clk:

instd_logic;

aclr:

instd_logic;

q:

outintegerrange15downto0);

end;

architecturelzqofcont4is

signalq1:

integerrange15downto0;

begin

process(aclr,clk)

begin

ifaclr='1'

thenq1<=0;

elseifclk'eventandclk='1'

thenq1<=q1+1;

endif;

endif;

endprocess;

q<=q1;

endlzq;

3-具有同步清零sclr,CLK,Q端口的加法计数器.

libraryieee;

useieee.std_logic_1164.all;

entitycont4is

port(sclr:

instd_logic;

clk:

instd_logic;

q:

outintegerrange15downto0);

end;

architecturelzqofcont4is

signalq1:

integerrange15downto0;

begin

process(sclr,clk)

begin

ifclk'eventandclk='1'

thenifsclr='1'

thenq1<=0;

elseq1<=q1+1;

endif;

endif;

endprocess;

q<=q1;

endlzq;

4.具有异步置位apre,CLK,Q端口的加法计数器.

libraryieee;

useieee.std_logic_1164.all;

entitycont4is

port(apre:

instd_logic;

clk:

instd_logic;

q:

outintegerrange15downto0);

end;

architecturelzqofcont4is

signalq1:

integerrange15downto0;

begin

process(clk,apre)

begin

ifapre='1'

thenq1<=15;

elseifclk'eventandclk='1'

thenq1<=q1+1;

endif;

endif;

endprocess;

q<=q1;

endlzq;

5.具有同步置位spre,CLK,Q端口的加法计数器.

libraryieee;

useieee.std_logic_1164.all;

entitycont4is

port(spre:

std_logic;

clk:

instd_logic;

q:

outintegerrange15downto0);

end;

architecturelzqofcont4is

signalq1:

integerrange15downto0;

begin

process(spre,clk)

begin

ifclk'eventandclk='1'

thenifspre='1'

thenq1<=15;

elseq1<=q1+1;

endif;

endif;

endprocess;

q<=q1;

endlzq;

6.具有异步清零aclr,异步置位apre,CLK.

libraryieee;

useieee.std_logic_1164.all;

entitycont4is

port(clk:

instd_logic;

aclr:

instd_logic;

apre:

instd_logic;

q:

outintegerrange15downto0);

end;

architecturelzqofcont4is

signalq1:

integerrange15downto0;

begin

process(aclr,clk,apre)

begin

ifaclr='1'

thenq1<=0;

elseifapre='1'

thenq1<=15;

elseifclk'eventandclk='1'

thenq1<=q1+1;

endif;

endif;

endif;

endprocess;

q<=q1;

endlzq;

7.具有同步使能ENB,CLK,Q端口的加法计数器.

libraryieee;

useieee.std_logic_1164.all;

entitycont4is

port(enb:

instd_logic;

clk:

instd_logic;

q:

outintegerrange15downto0);

end;

architecturelzqofcont4is

signalq1:

integerrange15downto0;

begin

process(enb,clk)

begin

ifclk'eventandclk='1'

thenifenb='1'

thenq1<=q1+1;

endif;

endif;

endprocess;

q<=q1;

endlzq;

8.具有异步清零aclr,异步置位apre,同步使能ENB,CLK,Q端口的加法计数器.

libraryieee;

useieee.std_logic_1164.all;

entitycont4is

port(aclr:

instd_logic;

apre:

instd_logic;

enb:

instd_logic;

clk:

instd_logic;

q:

outintegerrange15downto0);

end;

architecturelzqofcont4is

signalq1:

integerrange15downto0;

begin

process(aclr,apre,clk)

begin

ifaclr='1'

thenq1<=0;

elseifapre='1'

thenq1<=15;

elseifclk'eventandclk='1'

thenifenb='1'

thenq1<=q1+1;

endif;

endif;

endif;

endif;

endprocess;

q<=q1;

endlzq;

9.具有同步装载load,数据输入D,CLK,Q端口的加法计数器.

libraryieee;

useieee.std_logic_1164.all;

entitycont4is

port(load:

instd_logic;

d:

inintegerrange15downto0;

clk:

instd_logic;

q:

outintegerrange15downto0);

end;

architecturelzqofcont4is

signalq1:

integerrange15downto0;

begin

process(clk)

begin

ifclk'eventandclk='1'

thenifload='1'

thenq1<=d;

elseq1<=q1+1;

endif;

endif;

endprocess;

q<=q1;

endlzq;

10.具有异步装载load,数据输入D,CLK,Q端口的加法计数器.

libraryieee;

useieee.std_logic_1164.all;

entitycont4is

port(load:

instd_logic;

d:

inintegerrange15downto0;

clk:

instd_logic;

q:

outintegerrange15downto0);

end;

architecturelzqofcont4is

signalq1:

integerrange15downto0;

begin

process(clk,load,d)

begin

ifload='1'

thenq1<=d;

elseifclk'eventandclk='1'

thenq1<=q1+1;

endif;

endif;

endprocess;

q<=q1;

endlzq;

11.具有加法或减法工作模式选择端口mode,具有同步装载load,数据输入D,CLK,Q端口的计数器.

libraryieee;

useieee.std_logic_1164.all;

entitycont4is

port(mode:

instd_logic;

load:

instd_logic;

clk:

instd_logic;

d:

inintegerrange15downto0;

q:

outintegerrange15downto0);

end;

architecturelzqofcont4is

signalq1:

integerrange15downto0;

begin

process(load,clk,d,mode)

begin

ifclk'eventandclk='1'

thenifload='1'

thenq1<=d;

elseifmode='1'

thenq1<=q1+1;

elseq1<=q1+15;

endif;

endif;

endif;

endprocess;

q<=q1;

endlzq;