VHDL数字系统设计复习材料.docx

《VHDL数字系统设计复习材料.docx》由会员分享,可在线阅读,更多相关《VHDL数字系统设计复习材料.docx(21页珍藏版)》请在冰豆网上搜索。

VHDL数字系统设计复习材料

●

考试题型

一、填空题(每空1分,共10分)

二、单项选择题(每小题2分,共20分)

三、分析题(3小题,共40分)

四、程序设计题(3题,共30分)

各章主要知识要点

第2章VHDL简介

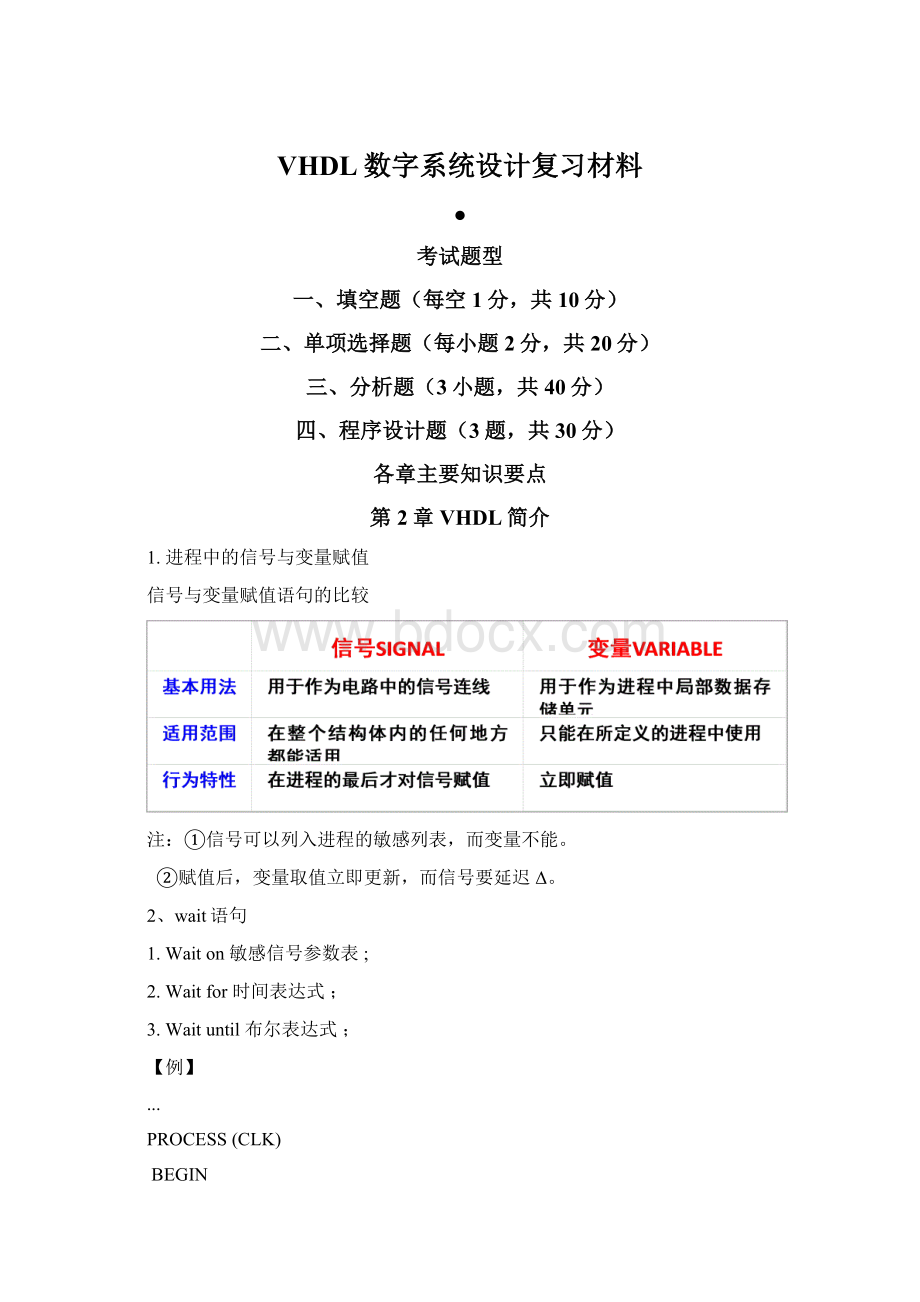

1.进程中的信号与变量赋值

信号与变量赋值语句的比较

注:

①信号可以列入进程的敏感列表,而变量不能。

②赋值后,变量取值立即更新,而信号要延迟Δ。

2、wait语句

1.Waiton敏感信号参数表;

2.Waitfor时间表达式;

3.Waituntil布尔表达式;

【例】

...

PROCESS(CLK)

BEGIN

IFCLK='1'

THENQ<=D;--利用进程的启动特性

ENDIF;

ENDPROCESS;

【例】

...

PROCESS

BEGIN

waituntilCLK='1';--利用wait语句

Q<=D;

ENDPROCESS;

【例】

...

PROCESS

BEGIN

waitonCLK;--利用wait语句

Q<=D;

ENDPROCESS;

3、惯性延迟和传输延迟的时序图

一、惯性延迟

◆AFTER语句表示惯性延迟。

◆理想的惯性延迟T:

把输入信号延迟T时间,还对任何宽度小于T的脉冲进行拦截。

◆格式:

信号名2<=[reject延时1]信号名1after延时2;

B<=AAFTER20ns;

C<=REJECT5nsAAFTER20ns;

二、传输延迟

◆传输延迟T:

只是把输入信号延迟T时间。

◆格式:

信号名2<=transport信号名1after延时;

【例1】

B<=AAFTER20ns;

B<=TRANSPORTAAFTER20ns;

【例2】图2.23(P56)上课补充的例子

Z1<=transportxafter10ns;

Z2<=xafter10ns;

Z3<=reject4nsxafter10ns;

[例3]下面的VHDL代码中,信号A、B、C、D均为整数,且初值赋为0。

若在10ns时D从0变为1,则A、B、C发生变化的时间和取值分别为

process(D)

begin

A<=1after5ns;

B<=A+1;

C<=Bafter10ns;

endprocess;

A在15ns时变为1,B在(10+△)ns时变为1,C在20ns时变为0

三、仿真延迟

⏹在VHDL语句中,如果没有指明延迟类型和延迟量,VHDL仿真器和综合器将自动为系统中的信号赋值配置一足够小而又能满足逻辑排序的延迟量,这个延迟量就称为仿真延迟(△延迟或δ延迟)。

⏹仿真延迟的引入由EDA工具自动完成。

⏹一个仿真周期产生一个仿真延迟。

⏹仿真命令:

force信号名V1t1,V2t2,…

【例】forceA00,12,03,19,016

当执行下列并发语句时,根据A,试画出描述B、C和D的时序图。

D<=transportAafter5ns;

B<=Aafter5ns;

C<=reject2nsAafter5ns;

第3章VHDL语言的高级议题

1、过程和函数的特点

子程序

◆VHDL中的子程序有两种类型:

过程和函数。

◆子程序可以在程序包、结构体和进程中定义,只有定义后才能被调用。

子程序内部的语句都是顺序语句。

◆子程序调用时,过程能返回多个变量,而函数只能返回一个变量。

◆函数的参数都是输入参数,而过程的参数有输入、输出和双向参数。

◆函数有顺序函数和并行函数,过程有顺序过程和并行过程。

其中,顺序函数、顺序过程存在于进程或另一个子程序中;并行函数、并行过程存在于进程或另一个子程序外。

2、属性语句

一、信号属性语句

◆利用信号的属性来获取信号的行为信息和功能信息。

1、返回单一值的信号属性(P298:

表8.2)

(1)s’EVENT

(2)s’ACTIVE

(3)s’LAST_EVENT

(4)s’LAST_VALUE

(5)s’LAST_ACTIVE

2、生成信号的信号属性(P299:

表8.3)

(1)s’DELAYED[(time)]

(2)s’STABLE[(time)]

(3)s’QUIET[(time)]

(4)s’TRANSACTION

二、数组属性语句(P300:

表8.4)

A’LEFT(N)A’RIGHT(N)

A’HIGH(N)A’LOW(N)

A’RANGE(N)A’REVERSE_RANGE(N)

A’LENGTH(N)

三、数据类型属性语句

(1)T’POS(X)返回输入X的位置序号

(2)T’VAL(X)返回输入位置序号X的值

(3)T’SUCC(X)返回输入X的下一个值

(4)T’PRED(X)返回输入X的前一个值

(5)T’LEFTOF(X)返回输入X左边的值

(6)T’RIGHTOF(X)返回输入X右边的值

3、生成语句的特点

◆生成语句是一种循环语句,具有复制电路的功能。

◆当设计一个由多个相同单元模块组成的电路时,可利用生成语句复制一组完全相同的并行组件或设计单元电路结构,避免多段相同结构的重复书写,以简化设计。

一、FOR循环模式

[生成标号:

]FOR循环变量IN取值范围GENERATE

[BEGIN]

并行语句

ENDGENERATE[生成标号];

【例】

...

FA0:

FullAdderportmap(A(0),B(0),c(0),c

(1),s(0));

FA1:

FullAdderportmap(A

(1),B

(1),c

(1),c

(2),s

(1));

FA2:

FullAdderportmap(A

(2),B

(2),c

(2),c(3),s

(2));

FA3:

FullAdderportmap(A(3),B(3),c(3),c(4),s(3));

...

→

...

FullAdd4:

foriin0to3generate

Begin

FAX:

FullAdderportmap(A(i),B(i),c(i),c(i+1),s(i));

EndgenerateFullAdd4;

...

二、IF模式

[生成标号:

]IF条件GENERATE

[BEGIN]

并行语句

ENDGENERATE[生成标号];

【例】

...

genLS:

ifLshiftgenerate

shifter<=Q(N-1downto1)&shiftin;

EndgenerategenLS;

genRS:

ifnotLshiftgenerate

shifter<=shiftin&Q(Ndownto2);

EndgenerategenRS;

...

第5章SM图与微程序

1.数字系统的设计:

1,数据单元包含保存运算数据和运算结果的数据寄存器,也包括完成数据运算的组合逻辑。

2.控制单元用来产生状态信号序列,以决定何时进行何种数据运算。

3.几乎所有的大型数字系统都包含某些状态概念,即系统的输出由输入的以前值和当前值决定。

4同步时序系统有两种通用的模型:

Mealy机和Moore机(都称为状态机)。

5.状态图:

用圆圈把各个状态圈起来,在圆圈上用圆弧表示转换条件。

与状态图相比,状态机流程图(SM图或ASM图)具有的优点:

(1)观察SM图会比观察等价的状态图更容易理解数字系统的执行过程;

(2)SM图可以直接同硬件实现联系起来。

SM图和软件流程图相似,但是它包含隐含的时序信息。

SM图表示物理硬件,因此图内所有的转移必须形成封闭的路径。

关于SM图的说明:

(1)状态框:

状态恰好在一个时钟周期内完成。

其输出信号列表在时钟周期内保持所示的值,在下一时钟周期复位为默认值。

(2)判断框:

必须与一个状态框关联,所以判断在状态的其他动作的同一时钟周期内确定。

(3)条件输出框:

必须紧随一个判断框,因此其输出信号与所属的状态框的输出信号在同一时钟周期内被置位。

2、SM图中隐含的时序信息

状态框的输出与条件输出的区别:

SM模块:

仅含有一个状态框,多个判断框以及与状态相关的条件输出框。

(1)一个SM模块仅含有一个输入通路,一个或多个输出通路;

(2)贯空一个SM模块,从入口到出口的路径称为一条链路;

(3)对于输入变量的每一个有效组合,只能有一个输出通路;

(4)在一个SM模块里,不能有内部反馈。

3、二进制无符号数的乘法原理P160-163

libraryieee;

useieee.numeric_bit.all;

entitymy_mult(

clk,st:

inbit;

mplier,mcand:

inunsigned(3downto0)

done:

outbit);

endmy_mult;

architecturebehave1ofmy_multis

signalstate:

integerrange0to3;

signalACC:

unsigned(8downto0);

aliasM:

bitisACC(0);

BEGIN

process(clk)

begin

ifclk’eventandclk=’1’then

casestateis

when0=>

ifst='1'then

Acc(8downto4)<=“00000”;

Acc(3downto0)<=mplier;

state<=1;

endif;

when1|3|5|7=>--“add/shift”state

ifM='1'then

Acc(8downto4)<=‘0’&Acc(7downto4)+mcand;

state<=state+1;

else

Acc<=‘0’&Acc(8downto1);

state<=state+2;

endif;

when2|4|6|8=>--“shift”state

Acc<=‘0’&Acc(8downto1);

state<=state+1;

when9=>

state<=0;

endcase;

endif;

endprocess;

done<=’1’whenstate=9else‘0’;

endif;

ENDbehave1;

4、由SM图给出下一状态和输出表达式

硬线化技术:

根据SM图,写出控制器输出和下一状态的逻辑表达式,并用门电路和触发器实现状态机。

控制器输出和下一状态的逻辑表达式,可通过观察SM图的链路和状态赋值得到,然后再进行化简即可。

【例】二进制乘法器

解答:

用门电路和触发器实现

5、双地址微程序的实现

微程序:

用一个存储器来存储所有的控制信号、每个状态和每一输入条件下的下一状态信息。

仅通过对存储器中的内容“排队”就可以实现控制器,故基于微程序的控制器称为排序器,存储控制字的存储器称为控制存储器或微程序存储器。

典型硬件框图:

如下

实现步骤:

1、针对微程序的SM图变换:

(1)变换SM图为Moore机,去除SM图中所有的条件输出;

(2)每个状态只检测一个输入。

可通过增加状态数来实现。

2、检查变换后的SM图,去掉多余的状态(状态最小化)。

【例】二进制乘法器

6、单地址微程序的实现

◆典型硬件框图:

1)状态赋值条件:

默认的下一状态值为当前状态值加1。

2)可通过添加额外状态(称为X状态)或对一些检测的变量取补,来实现SM图。

第6章存储器设计范例

1、ROM设计

2、RAM设计

1、ROM设计

◆ROM中存储了一组预定义的数据。

◆对ROM,只能读而不能写。

◆设计ROM时,有两个要点:

(1)存储单元的数量

(2)数据宽度

◆16×8ROM的设计:

P216-217

Libraryieee;

Useieee.std_logic_unsigned.all;

Useieee.std_logic_1164.all;

Entityromis

Port(addr:

instd_logic_vector(3downto0);

en:

instd_logic;

data:

outstd_logic_vector(7downto0));

End;

Architectureoneofromis

Typememoryisarray(0to15)ofstd_logic_vector(7downto0);

Signaldata1:

memory:

=(“”;“”;“”;“”;“”;“”;“”;“”;“”;“”;“”;“”;“”;“”;“”;“”);

Signaladdr1:

integerrange0to15;

Begin

Addr1<=conv_integer(addr);

Process(en,addr1,addr,data1)

Begin

Ifen=‘1’then

data<=data1(addr1);

Else

data<=(others=>’Z’);

Endif;

Endprocess;

End;

2、RAM设计

◆对RAM,可以读也可以写。

◆读时:

从RAM的某个单元中读出数据,给数据输出端口。

◆写时:

将数据写入端口的数据,写入RAM的某个单元。

◆32×8RAM的设计:

P218-219

读、写由片选信号CS控制。

◆2m×nRAM的设计:

读、写由时钟信号CLK控制

LIBRARYieee;

USEieee.std_logic_1164.all;

USEieee.std_logic_unsigned.all;

ENTITYsramIS

GENERIC(m:

integer:

=10;

n:

integer:

=8);

PORT(addr:

instd_logic_vector(m-1downto0);

wr,clk:

instd_logic;

datain:

instd_logic_vector(n-1downto0);

dataout:

outstd_logic_vector(n-1downto0));

ENDsram;

ARCHITECTUREbehvOFsramIS

TYPEmemoryISarray(0to2**m-1)ofstd_logic_vector(n-1downto0);--定义存储空间

SIGNALdata1:

memory;--RAM中数据的定义

SIGNALaddr1:

integerrange0to2**m-1;--RAM的单元地址

BEGIN

addr1<=conv_integer(addr);

PROCESS(clk,wr,addr1,data1,datain)--写操作进程

BEGIN

IFrising_edge(clk)andwr=‘0’THEN

data1(addr1)<=datain;

ENDIF;

ENDPROCESS;

PROCESS(clk,wr,addr1,data1)--读操作进程

BEGIN

IFrising_edge(clk)andwr=‘1’THEN

dataout<=dada1(addr1);

ELSE

dataout<=(OTHERS=>’z’);

ENDIF;

ENDPROCESS;

ENDbehv;

第7章可参数化宏模块及IP核的使用

1、Altera提供的宏功能模块和LPM函数分类

Altera为用户提供三类IP:

(1)基本宏功能(Megafunctions):

包括两类:

Altera专有的宏功能,以ALT开头进行标注,

②LPM(LibraryofParameterrizedModules)参数可设置模块库。

(2)MegaCore(宏功能核)

(3)AMPP(AlteraMegafunctionPartnersProgram)程序

第8章硬件测试与可测试性设计

1、组合逻辑电路的陷入故障测试

◆两个常见的故障:

短路和开路。

◆故障模拟:

陷0故障、陷1故障(陷入故障)。

◆陷入故障的测试:

(1)与门

(a)陷0故障测试(b)陷1故障测试

◆陷入故障的测试:

(2)或门

(a)陷0故障测试(b)陷1故障测试

上课的例子

第9章数字系统设计实例

1、模60,模12,模100的BCD码计数器的设计

模100计数器模块的VHDL代码

LibraryIEEE;

UseIEEE.numeric_bit.all;

EntityCTR_99is

Port(clk,inc,reset:

inbit;

dout:

outunsigned(7downto0);

t99:

outbit);

endCTR_99;

architecturecount99ofCTR_99is

signaldig1,dig0:

unsigned(3downto0);

begin

process(clk)

begin

ifclk’eventandclk=’1’then

ifreset=’1’thendig0<=”0000”;dig1<=”0000”;

else

ifinc=1’then

ifdig0=9thendig0<=”0000”;

ifdig1=9thendig1<=”0000”;

elsedig1<=dig+1;

endif;

elsedig0<=dig0+1;

endif;

endif;

endif;

endif;

endprocess;

t99<=’1’when(dig1=9anddig0=9)else‘0’;

dout<=dig1&dig0;

endcont99;

--------------------------------------------------------------------------------

模60计数器模块的VHDL代码

LibraryIEEE;

UseIEEE.numeric_bit.all;

EntityCTR_59is

Port(clk,inc,reset:

inbit;

dout:

outunsigned(7downto0);

t59:

outbit);

endCTR_59;

architecturecount59ofCTR_59is

signaldig1,dig0:

unsigned(3downto0);

begin

process(clk)

begin

ifclk’eventandclk=’1’then

ifreset=’1’thendig0<=”0000”;dig1<=”0000”;

else

ifinc=1’then

ifdig0=9thendig0<=”0000”;

ifdig1=5thendig1<=”0000”;

elsedig1<=dig+1;

endif;

elsedig0<=dig0+1;

endif;

endif;

endif;

endif;

endprocess;

t59<=’1’when(dig1=5anddig0=9)else‘0’;

dout<=dig1&dig0;

endcont99;

--------------------------------------------------------------------------------

模12计数器模块的VHDL代码

LibraryIEEE;

UseIEEE.numeric_bit.all;

EntityCTR_12is

Port(clk,inc,reset:

inbit;

dout:

outunsigned(7downto0);

t12:

outbit);

endCTR_12;

architecturecount12ofCTR_12is

signaldig1,dig0:

unsigned(3downto0);

begin

process(clk)

begin

ifclk’eventandclk=’1’then

ifreset=’1’thendig0<=”0000”;dig1<=”0000”;

else

ifinc=1’then

ifdig1=1anddig0=2thendig1<=”0000”;dig0<=”0000”;

else

ifdig0=9thendig0<=”0000”;dig1<=”0001”;

elsedig0<=dig0+1;

endif;

endif;

endif;

endif;

endif;

endprocess;

t12<=’1’when(dig1=1anddig0=2)else‘0’;

dout<=dig1&dig0;

endcont12;