基于FPGA进行VGA控制器设置实现显示器条纹显示.docx

《基于FPGA进行VGA控制器设置实现显示器条纹显示.docx》由会员分享,可在线阅读,更多相关《基于FPGA进行VGA控制器设置实现显示器条纹显示.docx(18页珍藏版)》请在冰豆网上搜索。

基于FPGA进行VGA控制器设置实现显示器条纹显示

实验目的与要求:

VGA控制器设计实现显示器条纹显示

要求:

通过FPGA板的VGA接口在显示器上显示一幅640*480由六条不同颜色的条纹组成的

图像。

实验内容:

VGA简介

VGA彩色显示器,彩色是由R、G、B(红、绿、蓝)三基色组成,CRT用逐行扫描方式实现图像显示,由VGA控制模块产生的水平同步信号(HS)和垂直同步信号(VS)控制阴极射线枪产生的电子束,打在涂有荧光粉的荧光屏上,产生R、G、B三基色,合成一个彩色像素。

扫描从屏幕的左上方开始,由左至右,由上到下,逐行进行扫描,每扫完一行,电子束回到屏幕下一行的起始位置,在回扫期间,CRT对电子束进行消隐,每行结束是用行同步信号HS进行行同步;扫描完所有行,再由场同步信号VS进行场同步,并使扫描回到屏幕的左上方,同时进行场消隐,预备下一场的扫描。

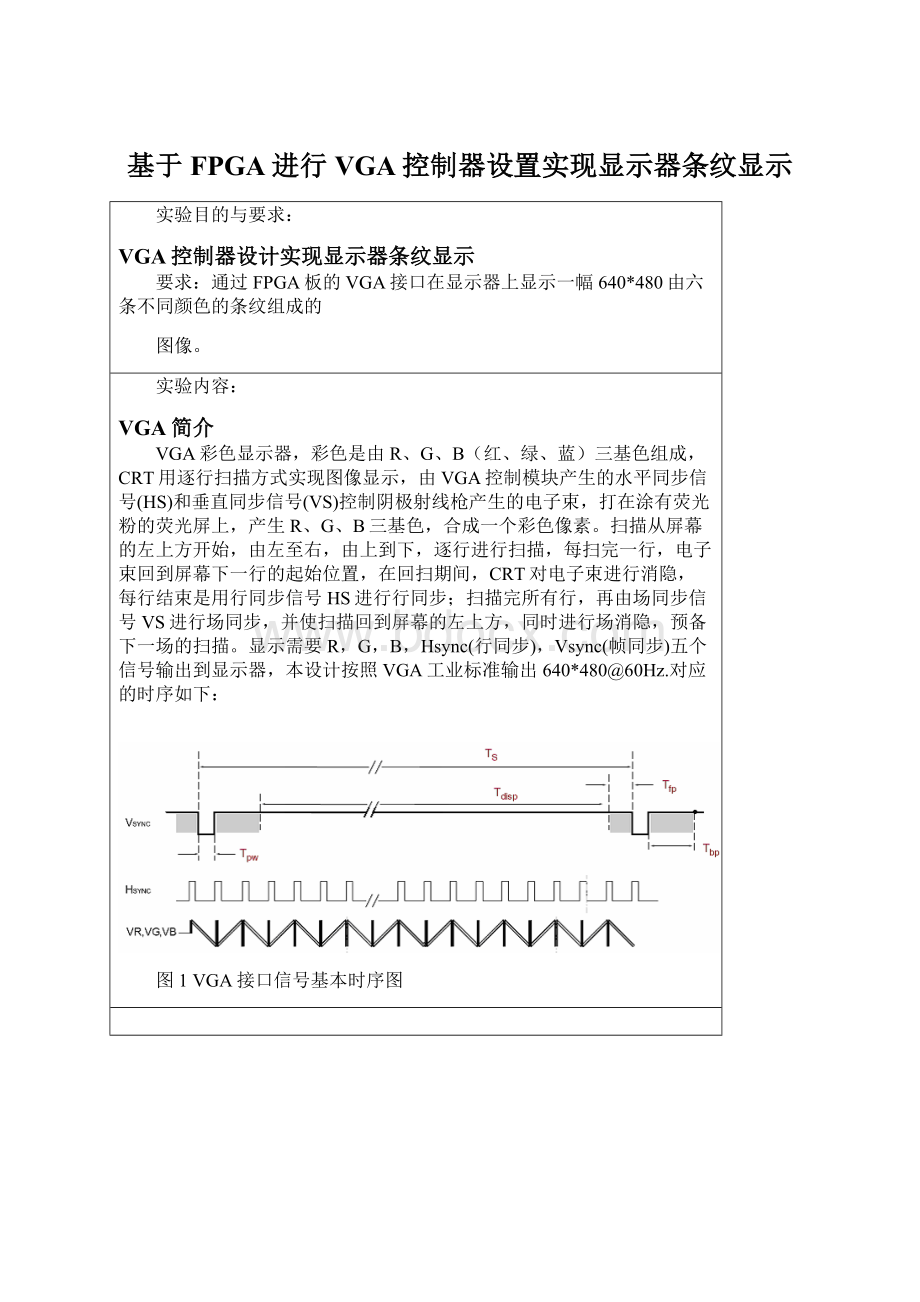

显示需要R,G,B,Hsync(行同步),Vsync(帧同步)五个信号输出到显示器,本设计按照VGA工业标准输出640*480@60Hz.对应的时序如下:

图1VGA接口信号基本时序图

图2FPGA板上的VGA接口

图3VGA(640*480@60Hz)时序图

VGA显示的设计模块为:

说明:

设计中FPGA板的VGA接口将R,G,B分别设为定义为2位,3位,3位,例如显示红色RGB可以输出为11000000,绿色输出为00111000,蓝色输出为00000111.

表125MHz640*480@60Hz模式下VGA的时序

规格说明

1.像素时钟配置为25Mhz。

2.编写代码时,需要用到的常数参考表一。

3.输出到显示器上的条纹为从上到下依次为RGBRGB(640*80)。

4.本实验使用FPGA板:

Sparant3EXC3S500E(建project时,需要选择板的型号)。

实验方法、步骤:

1、基本设计思想如下图所示:

分为这四个模块,产生Hsync(行同步),Vsync(帧同步)以及RGB色彩的输出。

2、具体设计VHDL代码

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

entitymainis

port(clk,rst:

instd_logic;

Vsync,Hsync:

outstd_logic;

data:

outstd_logic_vector(7downto0)

);

endmain;

architectureBehavioralofmainis

componentdcnis---------DCM分频模块,输出25M时钟

port(CLKIN_IN:

instd_logic;

RST_IN:

instd_logic;

CLKFX_OUT:

outstd_logic;----输出时钟

CLKIN_IBUFG_OUT:

outstd_logic;

LOCKED_OUT:

outstd_logic);

endcomponent;

signaldiv_25m,Nrst:

std_logic;

signalVsys_20b:

std_logic_vector(19downto0);

signalHsys_10b:

std_logic_vector(9downto0);

signaldata_Vsend,data_Hsend:

std_logic;

signalScan_16b:

std_logic_vector(15downto0);

signalScan_clc:

std_logic;

signaldata_sel:

std_logic_vector(1downto0);

begin

div:

dcnportmap(clk,Nrst,div_25m,open,open);---分频模块

Nrst<=notrst;

process(div_25m,rst)

begin

ifrst='0'then

Vsys_20b<="00000000000000000000";

elsifdiv_25m'eventanddiv_25m='1'then

Vsys_20b<=Vsys_20b+1;

ifVsys_20b=416799then

Vsys_20b<="00000000000000000000";

endif;

endif;

endprocess;

process(div_25m,rst,Vsys_20b)

begin

ifrst='0'then

Vsync<='1';data_Vsend<='0';

elsifdiv_25m'eventanddiv_25m='1'then

ifVsys_20b<8000then

Vsync<='1';data_Vsend<='0';

elsifVsys_20b>=8000andVsys_20b<9600then

Vsync<='0';data_Vsend<='0';

elsifVsys_20b>=9600andVsys_20b<32800then--128*255+160=32800

Vsync<='1';data_Vsend<='0';

elsifVsys_20b>=32800andVsys_20b<416800then

Vsync<='1';data_Vsend<='1';

endif;

endif;

endprocess;

process(div_25m,rst)

begin

ifrst='0'then

Hsys_10b<="0000000000";

elsifdiv_25m'eventanddiv_25m='1'then

Hsys_10b<=Hsys_10b+1;

ifHsys_10b=799then

Hsys_10b<="0000000000";

endif;

endif;

endprocess;

process(div_25m,rst,Hsys_10b)

begin

ifrst='0'then

Hsync<='1';data_Hsend<='0';

elsifdiv_25m'eventanddiv_25m='1'then

ifHsys_10b<16then

Hsync<='1';data_Hsend<='0';

elsifHsys_10b>=16andHsys_10b<112then

Hsync<='0';data_Hsend<='0';

elsifHsys_10b>=112andHsys_10b<160then

Hsync<='1';data_Hsend<='0';

elsifHsys_10b>=160andHsys_10b<800then

Hsync<='1';data_Hsend<='1';

endif;

endif;

endprocess;

process(div_25m,rst,data_Vsend)

begin

ifrst='0'then--

Scan_16b<="0000000000000000";Scan_clc<='0';

elsifdiv_25m'eventanddiv_25m='1'then---

Scan_clc<='0';

ifdata_Vsend='1'then

Scan_16b<=Scan_16b+1;

ifScan_16b=63999then

Scan_16b<="0000000000000000";

Scan_clc<='1';

endif;

endif;

endif;

endprocess;

process(rst,div_25m,Scan_clc,data_sel,data_Vsend)

begin

ifrst='0'then

data_sel<="00";

elsifdiv_25m'eventanddiv_25m='1'then

ifScan_clc='1'then

data_sel<=data_sel+1;

endif;

ifdata_sel="11"then

data_sel<="00";

endif;

endif;

endprocess;

process(rst,div_25m,data_Vsend,data_Hsend)

begin

ifrst='0'then

data<="00000000";

elsifdiv_25m'eventanddiv_25m='1'then

ifdata_Vsend='1'anddata_Hsend='1'then--

casedata_selis

when"00"=>data<="11000000";

when"01"=>data<="00111000";

when"10"=>data<="00000111";

whenothers=>data<="00000000";

endcase;

else

data<="00000000";

endif;

endif;

endprocess;

endBehavioral;

UCF管脚定义:

NET"clk"LOC="P183";

NETclkIOSTANDARD=LVCMOS33;

NET"rst"LOC="P142";#

NET"rst"PULLUP;

NET"rst"IOSTANDARD=LVCMOS33;

NET"data(0)"LOC="P74";#

NET"data

(1)"LOC="P75";#

NET"data

(2)"LOC="P76";#

NET"data(3)"LOC="P77";#

NET"data(4)"LOC="P78";#

NET"data(5)"LOC="P82";#

NET"data(6)"LOC="P83";#

NET"data(7)"LOC="P89";#

NET"Vsync"LOC="P68";#

NET"Hsync"LOC="P69";#

DCM设置:

综合结果:

综合分析:

仿真波形

实际测试:

实验结论:

本实验设计达到了实验要求,产生了预期效果,通过本实验,进一步了解了如何设计FPGA外部设备的驱动时钟,对计数器的设计有了更深一步的认识。

进一步熟悉了FPGA涉及的过程以及方法

指导教师批阅意见:

成绩评定:

指导教师签字:

年月日

备注:

注:

1、报告内的项目或内容设置,可根据实际情况加以调整和补充。

2、教师批改学生实验报告时间应在学生提交实验报告时间后10日内。

..