逻辑设计实验.docx

《逻辑设计实验.docx》由会员分享,可在线阅读,更多相关《逻辑设计实验.docx(73页珍藏版)》请在冰豆网上搜索。

逻辑设计实验

实验一ISE工具的使用流程--拨码开关控制LED实验

1.1实验目的

1.学会ISE的基本开发流程和常用功能的使用,本实验直接使用新建一个拨码开关控制led实验来作为设计文件,通过ise综合、映射、布局布线后,生成FPGA位流配置文件,通过JTAG口对开发板上FPGA进行配置。

2学会最基本拨码开关和led工作原理。

1.2实验原理

1.实验开发板的拨码开关向上拨动时处于低电平,向下处于高电平,用此来控制LED灯。

2.LED灯的的一端已经接高电平,另一端接FPGA的IO口,因此当IO输出低电平是便可点亮LED灯,否则LED为暗。

3.按键默认为高电平,按键按下时接地为低电平来检测按键的按下的复位信号。

1.3实验步骤

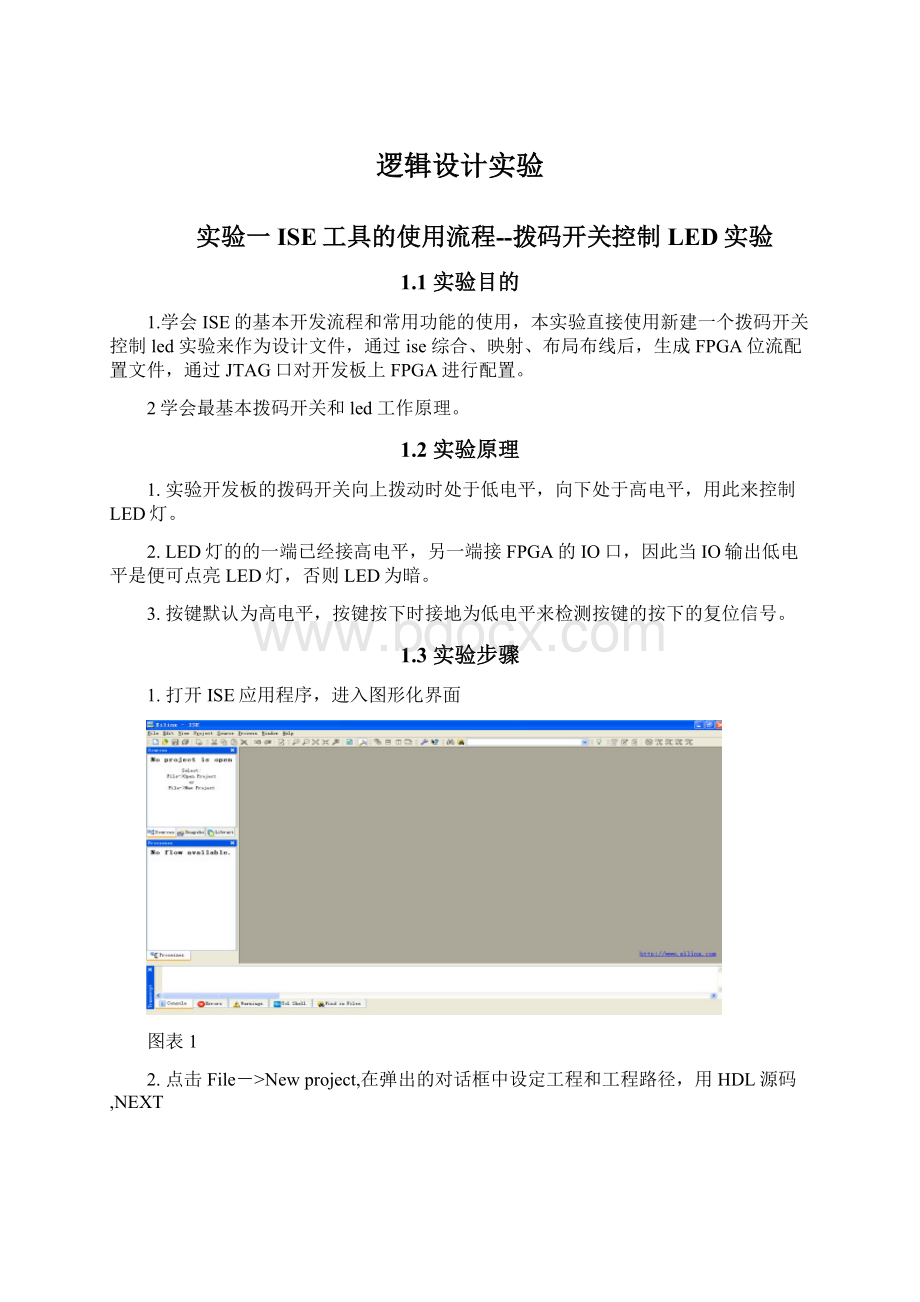

1.打开ISE应用程序,进入图形化界面

图表1

2.点击File->Newproject,在弹出的对话框中设定工程和工程路径,用HDL源码,NEXT

图表2

3.选定器件和封装,点击NEXT.

图表3

4.在工程中创建源文件,选择NewSource.,选中VerilogModule,输入源文件名称

图表4

5.可在弹出的对话框中输入信号的输入输出定义,也可暂时不定义

图表5

6.点击下一步,点击finish,然后自动回到creatanewsource对话框,点击下一步,再击下一步,然后点击finish。

图表6

6.点击设计的源文件,然后整个界面如图所示

图表7

7.将鼠标置于输入输出的下方,点击工具栏中的

,然后进入各子目录选择如下,这是一个快捷操作模板。

右键useinfile,可在源文件中看到已经添加相应的模板,然后修改一些端口、添加内容完善整个工程设计。

图表8

8.写源文件的代码如下

modulekey_led(clk,key,reset_n,led);

inputclk;

inputkey;

inputreset_n;

outputled;

regled;

//UsageofasynchronousresetsmaynegativelyimpactFPGAresources

//andtiming.IngeneralfasterandsmallerFPGAdesignswill

//resultfromnotusingasynchronousresets.Pleasereferto

//theSynthesisandSimulationDesignGuideformoreinformation.

always@(posedgeclkornegedgereset_n)

if(!

reset_n)begin

led<=1;

end

elsebegin

if(key==0)

led<=0;

else

led<=1;

end

endmodule

可用designUtilities点击createschematicsymbol下观看所生成的原理图来分析电路的性能。

9.添加约束文件,sourcefor选择在synthesis….,选中源文件,右键newsource,选择如图所示,输入文件名,点击next,然后finish.可以看到已经添加到工程中。

图表9

10.添加测试文件,在sourcefor选择在behavioral….,newsource,然后选择Verilogtestfixture,建立测试文件。

Next,选择关联key_led,点击完成

图表10

11.编写测试文件代码如下:

选中测试文件,在processes中的modelsimsimulator中的下拉菜单中双击simulate….这样就可以仿真了。

(注意在仿真之前要进行xilinxlibrary库的编辑,方法见附录1)

modulekey_led_tb_v;

//Inputs

regclk;

regkey;

regreset_n;

//Outputs

wireled;

//InstantiatetheUnitUnderTest(UUT)

key_leduut(

.clk(clk),

.key(key),

.reset_n(reset_n),

.led(led)

);

always#5clk=~clk;

initialbegin

//InitializeInputs

clk=0;

key=1;

reset_n=1;

//Wait100nsforglobalresettofinish

#100key=0;

#100reset_n=0;

#100reset_n=1;

#100key=1;

#100$stop;

//Addstimulushere

end

endmodule

图表11

12.管脚分配,回到sythesis…下,选中ucf文件,在process中双击打开assignpackage

Pins,按照管脚分配图进行相应配置,然后保存。

图表12

13.回到主界面选中HDL设计文件,双击generate…,然后修改到成功没有错误为止。

如下图所示

图表13

14.生成Bit文件,在generate….下拉菜单中,双击第二个,进行JTAG下载配置(先进行实验板上的下载硬件配置连接)。

然后会提示成功与否

图表14

15.进行开发板验证。

实验步骤结束

1.4实验结果分析

1.仿真如图所示

图表15

2.通过实验板验证可以看到,当讲拨码开关拨向ON时,灯亮,拨向OFF时暗,当不论在什么状态下,按下复位键则灯立即变暗,直至松手。

因此简单本设计符合设计预期的要求。

3.通过本实验,了解了最基本的硬件知识和建立一个工程,代码编写、综合、约束、分析、调试、下载观察等过程。

4.通过本次实验,进一步了解了FPGA工程使用的一个简单流程,在实验过程中需要认真做好每一个环节,配合实验说明书找到解决方法。

5.实验过程中遇到的问题和解决方法:

1)生成的bit文件后,下载实验现象没有变化:

可能保存的路径错了,导致屡试屡败

2)无法正常显示窗口:

修改桌面系统主题,该回经典xp等默认主题,这是由于EDK与操作系统的一些不兼容造成的。

3)综合错误:

修改成可综合代码。

4)有警告:

可稍微看一下警告的内容,但这是正常现象。

附录1:

xilinxlibrary编译方法两种(选其中一种):

(一)、在ISEProjectNavigator中编译仿真库

1、打开文件:

安装路径:

\Modeltech_6.2b,选中文件夹中的配置文件modelsim.ini,右击,将文件属性中的只读去掉,变成可写入的,接着用写字板程序打开;

2、在sources窗口中选择设计的目标器件xc3s500e-4pq208;在processes窗口中会出现designUtilties,选择CompileHDLSimulationLibraries项。

单击右键,在下拉菜单中选中Properties命令,打开对话框如图所示。

3、ProcessProperties按如图选择,单击ok按钮关闭对话框。

4、双击CompileHDLSimulationLibraries,程序会自动完成对库文件的编译。

5、观看是否在modelsim.ini文件中加入以下部份。

;VerilogSection

unisims_ver=库文件所在地址/unisims_ver

uni9000_ver=库文件所在地址/uni9000_ver

simprims_ver=库文件所在地址/simprims_ver

xilinxcorelib_ver=库文件所在地址/xilinxcorelib_ver

aim_ver=库文件所在地址/abel_ver/aim_ver

cpld_ver=库文件所在地址/cpld_ver

;VHDLSection

unisim=库文件所在地址/unisim

simprim=库文件所在地址/simprim

xilinxcorelib=库文件所在地址/xilinxcorelib

aim=库文件所在地址/abel/aim

pls=库文件所在地址/abel/pls

cpld=库文件所在地址/cpld

6、再将modelsim.ini设为只读即可

7、可采用modelsim进行仿真了。

(二)、另一种方法

1.在桌面上点击开始――运行――输入cmd,进入dos.

2.在dos下输入:

compxlib–smti_se–archall–lall–dir%xilinx%/lib–w

3.等编译完成后便可在安装目录下的lib中生成库,将生成的库加入modelsim中。

1)方法:

打开文件:

安装路径:

\Modeltech_6.2b,选中文件夹中的配置文件modelsim.ini,右击,将文件属性中的只读去掉,变成可写入的,接着用写字板程序打开;

2)在modelsim.ini中加入一下内容(库文件所在地址为->安装路径:

\Xilinx92i\lib,比如有的同学是装在D盘,那就是:

D:

\Xilinx92i\lib,这一步完成后将modelsim.ini再设为只读)

;VerilogSection

unisims_ver=库文件所在地址/unisims_ver

uni9000_ver=库文件所在地址/uni9000_ver

simprims_ver=库文件所在地址/simprims_ver

xilinxcorelib_ver=库文件所在地址/xilinxcorelib_ver

aim_ver=库文件所在地址/abel_ver/aim_ver

cpld_ver=库文件所在地址/cpld_ver

;VHDLSection

unisim=库文件所在地址/unisim

simprim=库文件所在地址/simprim

xilinxcorelib=库文件所在地址/xilinxcorelib

aim=库文件所在地址/abel/aim

pls=库文件所在地址/abel/pls

cpld=库文件所在地址/cpld

实验二用CoreGenerator生成DCM并进行仿真验证

2.1实验目的

学会用coregenerate生成dcm,并使用modelsim进行仿真。

2.2实验原理

1.DCM是数字时钟管理器,它在xilinx的FPGA的设计中应用广泛,dcm可以产生输入时钟的一倍频、二倍频,或M/D倍频等功能,也可以产生90、180、270度相移的时钟,例如FPGA输入时钟为66M,而我们的系统需要133M的时钟,则可以用到DCM二倍频。

2.编译库,将库文件加入modelsim中,然后可以进行联合仿真调试。

2.3实验步骤

1.在桌面上点击开始-》程序—》xilinxise10.1—ISE》accesseries—》Coregenerator,界面如下:

图表16

2.单击file->newproject,系统出现如下画面,然后选择工程路径和名字。

然后next,设置工程的基本参数:

part参数设置,generation参数,advanced,然后点击OK。

图表17

3.完成新建工程向导后,按顺序展开FPGAfeaturesanddesign-》clocking-》spartan_3e,可以看到DCM_SP,双击singleDCM_SP。

图表18

4.双击SingleDCM_SP后,进入dcm生成向导,设定名称为dcm_test.,点击ok后,进入下一界面进行如下图的配置。

图表19

5.下一步进入下图所示的界面,设定完成后点击next.

区域一:

DCM_SP的基本模型,根据实际情况在需要的输入输出上打勾;

区域二:

设定输入DCM的时钟频率,或者是周期,根据需要选择一种;

区域三:

设定DCM的输出时钟和输入时钟的相对位移,一般情况下不进行设置;

区域四:

选择输出时钟源,是FPGA外部输入,还是内部时钟信号,一般第一级的dcm是外部输入,二级、三级dcm是前一级的dcm输出,是内部信号;

区域五:

时钟反馈类型,是外部还是内部反馈,一般是直接使用DCM的clk0或者clk2x做内部反馈,特殊情况需要外部输入的时钟进行反馈,但很少使用;

区域六:

设定clkdv的分频数,即相对于clkin的分频数,如图选择的值为5,则50Mhz的输入进行五分频,那么clkdv输出为10Mhz。

如果没有勾clkdv输出,则不需要进行参数设置;

区域七:

反馈类型选择,可以是时钟的1或者2分频。

区域八:

时钟dutycycle的矫正,默认选上,可以更好的占空比为50%的时钟信号。

图表20

6.下一步进入clockbuffer的设置,默认使用个咯罢了globalbuffer。

点击next

图表21

7.下一步设置的是clkfx的时钟输出,一般采用设置M和D的值来控制clkFX的输出,计算公式为clkfx=clkin*(m/d),输入预计好的M、D值,点击calculate即可得到clkfx的输出频率,如果最开始没有选择clkfx输出,则可以跳过。

图表22

8.点击next,点击finish,完成DCM的生成。

完成后的界面如图所示。

图表23

9.在ise里面新建工程,将生成的dcm_test拷贝到工程目录下,并添加到工程文件中。

建完后如下图所示

图表24

观看综合后的原理图方法为:

10.给dcm_test添加测试文件,具体过程可参考实验一,建完后修改补充测试文件如下(

这里的dcm为高电平复位):

`timescale1ns/1ps

`defineclk_cycle15

////////////////////////////////////////////////////////////////////////////////

//Company:

//Engineer:

//CreateDate:

18:

42:

4301/02/2010

//DesignName:

dcm_test

//ModuleName:

E:

/xilinx/project/lab2/dcm_11M/dcm_11M_tb.v

//ProjectName:

dcm_11M

//TargetDevice:

//Toolversions:

//Description:

//VerilogTestFixturecreatedbyISEformodule:

dcm_test

//Dependencies:

//Revision:

//Revision0.01-FileCreated

//AdditionalComments:

///////////////////////////////////////////////////////////////////////////////

moduledcm_11M_tb_v;

//Inputs

regCLKIN_IN;

regRST_IN;

//Outputs

wireCLKDV_OUT;

wireCLKFX_OUT;

wireCLKIN_IBUFG_OUT;

wireCLK0_OUT;

wireLOCKED_OUT;

//InstantiatetheUnitUnderTest(UUT)

dcm_testuut(

.CLKIN_IN(CLKIN_IN),

.RST_IN(RST_IN),

.CLKDV_OUT(CLKDV_OUT),

.CLKFX_OUT(CLKFX_OUT),

.CLKIN_IBUFG_OUT(CLKIN_IBUFG_OUT),

.CLK0_OUT(CLK0_OUT),

.LOCKED_OUT(LOCKED_OUT)

);

always#(`clk_cycle/2)CLKIN_IN=~CLKIN_IN;

initialbegin

//InitializeInputs

CLKIN_IN=0;

RST_IN=0;

//Wait100nsforglobalresettofinish

#500RST_IN=1;

#100RST_IN=0;

#500$stop;

end

endmodule

11.添加管脚时许约束文件,先建立约束文件,然后双击creattimingconstraints—》global—》双击clock——in的period,如图所示进行配置,然后保存退出。

图表25

12.调用modelsim进行联合仿真,实验结束,可对DCM设置参数进行修改不断改变波形。

图表26

13.综合后几个常用的工具,如观察RTL级的电路结构和门级结构的原理图

图表27

2.4实验结果分析

1.调用modelsim的仿真结果如下

图表28

结果分析:

由于本实验在区域六选择的是6分频,clkfx也是六分频,无位相移动因此可以从波形很直观的看出实验结果。

即clkfx和clkdv都是六分频和clkin是同相位的

2.为了得到其他的频率输出可以对DCM参数进行修改,如将clkdv改成3分频后的仿真波形。

可以看到clkdv输出变成了3分频,而clkfx不做改变

图表29

3.将clk180选中,将clkfx180选中,两者都是六分频,仿真波形如图所示,从图形可以看出实验结果与预期的相符合。

Clkfx180和clk180与clkfx和clkdv是反相关系。

图表

实验三按键检测实验

3.1实验目的

1.学会鉴别信号的上升沿和下降沿,熟练掌握信号的检测。

2.学会按键检测原理,熟练掌握按键信号的检测,掌握和理解按键抖动对信号检测的影响。

3.2实验原理

3.2.1信号检测原理

信号的采集就是对信号的上升沿和下降沿进行采集,上图是一个信号enable,它变为高电平几个周期后再变为低电平。

首先对信号的enable进行一拍时钟采样,也就是一个时钟周期的延迟,经过处理后的信号enably_dly是enable的一个延迟一个时钟周期后的信号,如图所示。

图表31

3.2.2键盘检测原理

按键检测原理是:

当按键按下时,输入电平由高变低,按键松开后,输入电平有低变高,如此会产生一个下降沿和一个上升沿,只要扑捉到这两个沿,就可以确定按键按下。

3.2.3键盘防抖原理

在按键被按下的瞬间,由于物理上的原因,导致按键在被按键的瞬间的过程中其实是处于高电平和低电平之间进行抖动,加上本实验的时钟频率很高,容易产生信号采集错误,导致检测失败,无法得到正确的结果。

若要正确防抖,需要在检测到按键上升沿后延迟一小段信号在进行上升沿和下降沿检测。

3.3实验步骤

1.建立ise工程,建立按键检测文件和测试文件如图所示:

图表32

键盘检测程序如下:

modulekey_scan(clk,reset_n,key,led);

inputclk;

inputreset_n;

inputkey;

outputled;

regkey_dly;

regkey_dly1;

regkey_pose_flag;

regkey_nege_flag;

regkey_pulse;

regled;

always@(negedgereset_norposedgeclk)

begin

if(reset_n==1'b0)

key_dly<=1'b0;

else

key_dly<=key;

end

always@(negedgereset_norposedgeclk)

begin

if(reset_n==1'b0)

key_dly1<=1'b0;

else

key_dly1<=key_dly;

end

always@(negedgereset_norposedgeclk)

begin

if(reset_n==1'b0)

key_nege_flag<=1'b0;

else

if(key_dly==1'b0&&key_dly1==1'b1)

key_nege_flag<=1'b1;

elseif(key_pulse==1'b1)

key_nege_flag<=1'b0;

end

always@(negedgereset_norposedgeclk)

begin

if(reset_n==1'b0)

key_pose_flag<=1'b0;

else

if(key_nege_flag==1'b1)

begin

if(key_dly==1'b1&&key_dly1==1'b0)

key_pose_flag<=1'b1;

elseif(key_pulse==1'b1)

key_pose_flag<=1'b0;

end

end

always@(negedgereset_norposedgeclk)

begin

if(reset_n==1'b0)

key_pulse<=1'b0;

else

if(key_pose_flag==1'b1&&key_nege_flag==1'b1)

key_pulse<=~key_pulse;

else

key_pulse<=key_pulse;

end

always@(posedgeclkornegedgereset_n)

begin

if(reset_n==1'b0)

led<=1'b1;

else

if(key_pulse==1'b1)

led<=~led;

end

endmodule

测试文件:

`include"./key_scan.v"

`timescale1ns/1ns

modulekey_scan_t;

regclk,key,reset_n