基于VHDL的多功能电子秒表设计.docx

《基于VHDL的多功能电子秒表设计.docx》由会员分享,可在线阅读,更多相关《基于VHDL的多功能电子秒表设计.docx(13页珍藏版)》请在冰豆网上搜索。

基于VHDL的多功能电子秒表设计

数字系统设计与硬件描述语言

期末考试作业

题目:

多功能电子秒表设计

学院:

电子信息工程学院

专业:

电子信息工程

学号:

3009204308

姓名:

张嘉男

2012-05-31

一、选题设计描述

1.功能介绍

本系统能够精确计时,具有复位、计时功能,可显示计时时间的分、秒和0.1秒等度量,最长计时为10分钟。

2.算法简介

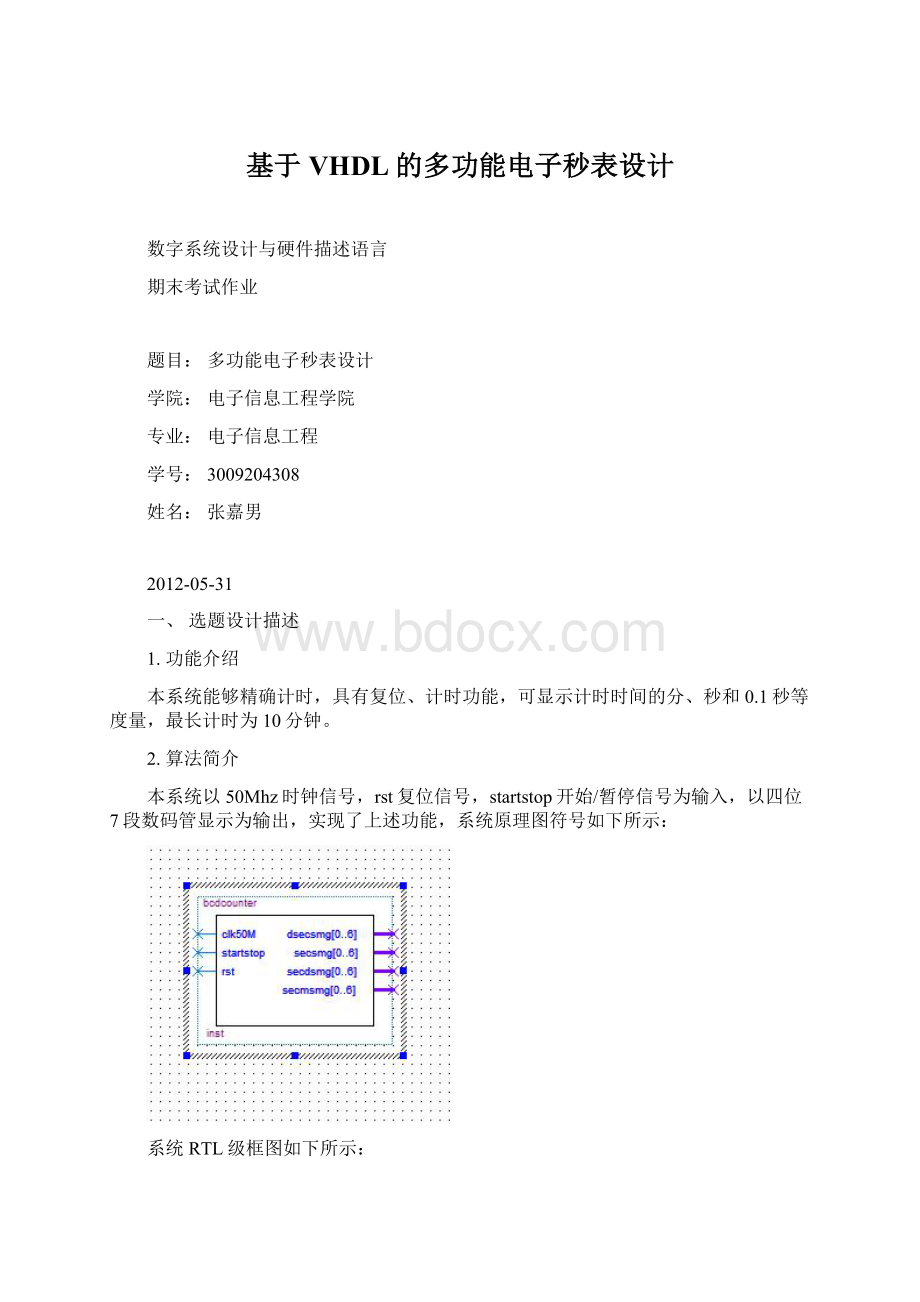

本系统以50Mhz时钟信号,rst复位信号,startstop开始/暂停信号为输入,以四位7段数码管显示为输出,实现了上述功能,系统原理图符号如下所示:

系统RTL级框图如下所示:

本系统的实现共分为以下几个模块:

模块一、分频器

该模块又分为1/5000分频器divf1,1/1000分频器divf2两部分,实现对50MHz系统时钟的两次分频,最终将系统时钟分频到10Hz,作为最低位(0.1秒位)的输入时钟。

divf1模块输入信号为50MHz时钟信号,复位信号,输出信号为10kHz时钟信号;

divf2模块输入信号为10KHz时钟(实现上不严格是,见后面T触发器模块解释)信号,输出,复位信号,输出信号为10Hz时钟信号。

模块二、计数器

该模块又分为十进制计数器counter10,和六进制计数器counter6,分别实现对输入时钟信号的十进制、六进制计数,十进制计数器在系统中用于对0.1秒位,秒个位,分位的输入时钟计数(1s=10*0.1s),六进制计数器在系统中用于对秒十位的输入时钟计数(1min=60s)。

模块三、T触发器Ttrigger

该模块实现系统复位,开始/暂停功能,以startstop信号作为触发器的时钟输入,复位信号作为T信号,触发器输出与分位进位信号和复位信号相与,其输出在作为10Hz时钟信号输入给0.1s位十进制计数器。

模块四、4-7译码器bcdsev

该模块实现将各计数器的计数输出显示到数码管上,输入信号为计数器4位计数输出,输出信号为相应数码管7段,当相应段为低电平(’0’)时亮起。

系统整体运行流程为:

50MHz时钟信号输入到1/5000分频器中,分为10kHz的时钟,再经过一个用来控制系统复位、启停的与门电路后,输入到1/1000的分频器中,分为10Hz的时钟,此时钟信号输入到一个十进制计数器内,十进制计数器输出4位计数信号给4-7译码器,同时输出1位进位信号给另一个十进制计数器内,4-7译码器输出7位段选信号给0.1s显示位数码管,显示此时0.1s位数值,而另三个计数器与此计数器进行相同的工作,唯一不同的是用于10s位计时的计数器用的是六进制计数器。

与此同时,当复位信号被触发(置低)时,第二个分频器divf2输入时钟为零(与门控制),同时4位数码管输出为0000,实现系统复位,当复位信号取消(置高),startstop信号每触发一个上升沿,秒表开始/暂停一次。

当秒表运行到10分钟后,进位信号使数码管输出归零,系统实现复位。

二、程序源代码及说明

-------------------------------------------------------------------------

模块名称:

divf1.vhd

模块功能:

实现对50MHz时钟信号的第一次分频

端口信号说明:

clk1:

待分频时钟信号

rst1:

分频器复位信号

q1:

分频后的输出信号

------------------------------------------------------------------------

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_unsigned.ALL;

ENTITYdivf1IS

PORT(clk1:

INSTD_LOGIC;

rst1:

instd_logic;

q1:

OUTSTD_LOGIC);

ENDdivf1;

ARCHITECTUREbehavOFdivf1IS

signalqn1:

std_logic_vector(13downto0);

BEGIN

PROCESS(clk1,rst1)

BEGIN

ifrst1='0'then

qn1<="00000000000000";

elsifclk1'eventandclk1='1'then

ifqn1<10000thenqn1<=qn1+1;

elseqn1<=(OTHERS=>'0');

endif;

endif;

ENDPROCESS;

q1<=qn1(13);--分频输出

ENDbehav;

-------------------------------------------------------------------------

模块名称:

divf2.vhd

模块功能:

实现对50MHz时钟信号的第二次分频

端口信号说明:

clk2:

待分频时钟信号

rst2:

分频器复位信号

q2:

分频后的输出信号

------------------------------------------------------------------------

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_unsigned.ALL;

ENTITYdivf2IS

PORT(clk2:

INSTD_LOGIC;

rst2:

instd_logic;

q2:

OUTSTD_LOGIC);

ENDdivf2;

ARCHITECTUREbehavOFdivf2IS

signalqn2:

std_logic_vector(9downto0);

BEGIN

PROCESS(clk2,rst2)

BEGIN

ifrst2='0'then

qn2<="0000000000";

elsifclk2'eventandclk2='1'then

ifqn2<1000thenqn2<=qn2+1;

elseqn2<=(OTHERS=>'0');

endif;

endif;

ENDPROCESS;

q2<=qn2(9);--分频输出

ENDbehav;

----------------------------------------------------------------

模块名称:

counter10.vhd

模块功能:

十进制计数器

端口信号说明:

CLK10:

计数器时钟信号

RST10:

计数器复位信号

CQ10:

计数器4位计数输出

COUT10:

计数器进位输出

------------------------------------------------------------------

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYcounter10IS

PORT(CLK10,RST10:

INSTD_LOGIC;

CQ10:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

COUT10:

OUTSTD_LOGIC);

ENDcounter10;

ARCHITECTUREbehavOFcounter10IS

BEGIN

PROCESS(CLK10,RST10)

VARIABLECQI10:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

IFRST10='0'THENCQI10:

=(OTHERS=>'0');--计数器复位

ELSIFCLK10'EVENTANDCLK10='1'THEN--检测时钟上升沿

IFCQI10<"1001"THENCQI10:

=CQI10+1;COUT10<='0';--允许计数

ELSECQI10:

="0000";COUT10<='1';--大于9,计数值清零

ENDIF;

ENDIF;

--IFCQI10="1001"THENCOUT10<='1';--计数大于9,输出进位信号

--ELSECOUT10<='0';

--ENDIF;

CQ10<=CQI10;--将计数值向端口输出

ENDPROCESS;

ENDbehav;

----------------------------------------------------------------

模块名称:

counter6.vhd

模块功能:

十进制计数器

端口信号说明:

CLK6:

计数器时钟信号

RST6:

计数器复位信号

CQ6:

计数器4位计数输出

COUT6:

计数器进位输出

------------------------------------------------------------------

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYcounter6IS

PORT(CLK6,RST6:

INSTD_LOGIC;

CQ6:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

COUT6:

OUTSTD_LOGIC);

ENDcounter6;

ARCHITECTUREbehavOFcounter6IS

BEGIN

PROCESS(CLK6,RST6)

VARIABLECQI6:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

IFRST6='0'THENCQI6:

=(OTHERS=>'0');--计数器复位

ELSIFCLK6'EVENTANDCLK6='1'THEN--检测时钟上升沿

IFCQI6<"0101"THENCQI6:

=CQI6+1;COUT6<='0';--允许计数

ELSECQI6:

="0000";COUT6<='1';--clearwhenit'sbiggerthan5

ENDIF;

ENDIF;

--IFCQI6="0101"THENCOUT6<='1';

--ELSECOUT6<='0';

--ENDIF;

CQ6<=CQI6;--将计数值向端口输出

ENDPROCESS;

ENDbehav;

---------------------------------------------------------------------------------

模块名称:

bcdsev.vhd

模块功能:

4-7译码器

端口信号说明:

a:

4位输入

rstsev:

复位信号

q:

7段输出

-----------------------------------------------------------------------------------

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYbcdsevIS

PORT(a:

INSTD_LOGIC_VECTOR(3DOWNTO0);

rstsev:

instd_logic;

q:

OUTSTD_LOGIC_VECTOR(0TO6));--7段输出

ENDbcdsev;

ARCHITECTUREbehavOFbcdsevIS

BEGIN

PROCESS(a)

BEGIN

ifrstsev='0'thenq<="0000001";

else

casea(3downto0)is--BCD7段译码表

when"0000"=>q<="0000001";when"0001"=>q<="1001111";

when"0010"=>q<="0010010";when"0011"=>q<="0000110";

when"0100"=>q<="1001100";when"0101"=>q<="0100100";

when"0110"=>q<="0100000";when"0111"=>q<="0001111";

when"1000"=>q<="0000000";when"1001"=>q<="0000100";

whenothers=>q<="1111111";

ENDcase;

endif;

ENDPROCESS;

ENDbehav;

-------------------------------------------------------------------

模块名称:

Ttrigger.vhd

模块功能:

T触发器

端口信号说明:

t:

t信号

clk:

时钟信号

q:

输出信号

-----------------------------------------------------------------------

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYTtriggerIS

port(t:

instd_logic;

clk:

instd_logic;

q:

outstd_logic);

endentityTtrigger;

architecturebehofTtriggeris

signaltmp:

std_logic:

='0';

begin

process(clk,t)

begin

ifclk'EVENTANDclk='1'THEN

ift='1'then

tmp<=nottmp;

endif;

endif;

q<=tmp;

endprocess;

endbeh;

-----------------------------------------------------------------------------

模块名称:

bcdcounter.vhd

模块功能:

系统顶层文件,调用各功能模块

模块端口信号说明:

clk50MHz:

50MHz时钟信号

rst:

复位信号

startstop:

系统启/停信号

dsecsmg[6…0]:

0.1s位数码管7段输出

secsmg[6…0]:

1s位数码管7段输出

secdsmg[6…0]:

10s位数码管7段输出

secmsmg[6…0]:

分钟位数码管7段输出

模块内部信号说明:

clk10khz:

第一次分频后的10khz信号

triggerout:

T触发器输出信号

clk10khzafterand:

经过控制与门后的10khz信号

clk10hz:

第二次分频后的10hz时钟信号

dsecout:

0.1s计数器进位信号

secout:

1s计数器进位信号

secdout:

10s计数器进位信号

bdsec[3..0]:

0.1s计数器计数信号

bsec[3..0]:

1s计数器计数信号

bsecd[3..0]:

10s计数器计数信号

bsecm[3..0]:

分钟计数器计数信号

cn:

分钟计数器进位信号

------------------------------------------------------------------------

--多功能电子秒表设计

--基本要求:

精确计时,具有复位、计时功能,可显示计时时间的分、秒和0.1秒等度量,最长计时为10分钟

libraryieee;

useieee.std_logic_1164.all;

entitybcdcounteris

port(clk50M:

instd_logic;

startstop:

instd_logic;

rst:

instd_logic;

dsecsmg,secsmg,secdsmg,secmsmg:

outstd_logic_vector(0to6));

endbcdcounter;

architectureoneofbcdcounteris

componentdivf1

PORT(clk1:

INSTD_LOGIC;

rst1:

instd_logic;

q1:

OUTSTD_LOGIC);

ENDcomponentdivf1;

componentTtrigger

port(t:

instd_logic;

clk:

instd_logic;

q:

outstd_logic);

endcomponentTtrigger;

componentdivf2

PORT(clk2:

INSTD_LOGIC;

rst2:

instd_logic;

q2:

OUTSTD_LOGIC);

ENDcomponentdivf2;

componentcounter10

PORT(CLK10,RST10:

INSTD_LOGIC;

CQ10:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

COUT10:

OUTSTD_LOGIC);

ENDcomponentcounter10;

componentcounter6

PORT(CLK6,RST6:

INSTD_LOGIC;

CQ6:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

COUT6:

OUTSTD_LOGIC);

ENDcomponentcounter6;

componentbcdsev

PORT(a:

INSTD_LOGIC_VECTOR(3DOWNTO0);--数据输入

rstsev:

instd_logic;

q:

OUTSTD_LOGIC_VECTOR(0TO6));--7段输出

ENDcomponentbcdsev;

signalclk10khz:

std_logic;

signaltriggerout:

std_logic;

signalclk10khzafterand:

std_logic;

signalclk10hz:

std_logic;

signaldsecout:

std_logic;

signalsecout:

std_logic;

signalsecdout:

std_logic;

signalbdsec,bsec,bsecd,bsecm:

std_logic_vector(3downto0);

signalcn:

std_logic;

begin

divf1ex:

divf1portmap(clk50M,rst,clk10khz);

trigger1:

Ttriggerportmap(rst,startstop,triggerout);

clk10khzafterand<=clk10khzandtriggeroutand(notcn);

divf2ex:

divf2portmap(clk10khzafterand,rst,clk10hz);

dseccouter10:

counter10portmap(clk10hz,rst,bdsec,dsecout);

seccounter10:

counter10portmap(dsecout,rst,bsec,secout);

secdcounter6:

counter6portmap(secout,rst,bsecd,secdout);

secmconter10:

counter10portmap(secdout,rst,bsecm,cn);

bcddsec:

bcdsevportmap(bdsec,rst,dsecsmg);

bcdsec:

bcdsevportmap(bsec,rst,secsmg);

bcdsecd:

bcdsevportmap(bsecd,rst,secdsmg);

bcdsecm:

bcdsevportmap(bsecm,rst,secmsmg);

endarchitectureone;

三、仿真结果及分析

系统总体仿真结果如下图所示:

首先说明,为使仿真能顺利进行,在仿真时将50Mhz时钟二次分频到10khz而不是实际的10hz,另外还去掉了startstop信号,这样做并不会影响电路的内部逻辑及输出结果。

由上图上图仿真结束时间设为10ms,理论仿真结果应为秒表从0000一直运行到0099,分析图中相应波形可知仿真结果正确。

四、心得体会

通过这次实验,使我对VHDL语言有了进一步的了解和熟悉,对以前学过的数电知识是一次很好的运用,同时熟悉了QuartusII软件的使用方法,能够独立完成VHDL中型项目的设计并进行仿真。

另外,通过本次实验还使我认识到在软件里的仿真参考价值是有限的,只有真正将程序下载到实际电路中才能真正检测程序的对错。

为了验证程序的正确性,在第二次实验课上,我将模块中的信号分配了引脚,并烧写到DE2实验平台中,以4位数码管做显示,以两个拨码开关座输入,控制秒表的启停,复位。

通过一段时间的调试,程序能够正确运行,能够实现预期功能。

这次作业为我以后的学习提供了思路,极大地提高了我的动手实践能力。