基于遗传基因算法的智能PID的设计和FPGA的使用.docx

《基于遗传基因算法的智能PID的设计和FPGA的使用.docx》由会员分享,可在线阅读,更多相关《基于遗传基因算法的智能PID的设计和FPGA的使用.docx(9页珍藏版)》请在冰豆网上搜索。

基于遗传基因算法的智能PID的设计和FPGA的使用

基于遗传基因算法的智能PID的设计和FPGA的使用

摘要:

现在,在工业控制过程中很多系统都是时变,实时和非线性的。

那些系统只通过PID参数的调整,已出现越来越多的问题了。

首先,通过遗传基因算法(AGA)来获得较好的PID控制参数并且通过FPGA1P1C6F256C8去进行PID控制。

第二,闭环系统的测试时通过DSP来建立的。

最后,在第四节的第二部分获得的TCL脚本文件是VHDL代码通过仿真软件的编译器后获得的。

结果证明了AGA增进了PID参数获取的精度和控制系统的实用性,同时证明了基于FPGA的只能PID控制的灵活和实用。

1介绍

PID控制时自动控制中最古老的,最通用的和最强大的控制方法。

随着工业的发展,控制的对象变得越来越复杂,其中最重要的是其时变,非线性和实时性。

传统的PID控制对其控制能力越来越低。

由于传统PID的一些缺点,一些人在PID参数的获得方面进行了很大的改进。

今年来像模糊PID控制,神经网络PID控制器,专家PID控制等智能PID控制已经成为越来越流行的控制方法。

智能PID控制器简化了程序的设计,并且有自我适应,自我组织和自我学习的能力,同时它也有传统PID的有点,如简单的结构和较好的鲁棒性。

同时VLSI的智能化和科技都有了很大的进步。

它使将一个控制系统集成在一个芯片中成为可能。

由于FPGA有并行计算和过程的能力,它能快速的完成大量复杂的计算。

此外,基于FPGA的控制器的设计有强的经济性,因为它很灵活而且普遍。

这篇文章详细介绍了一个基于AGA的智能PID控制的具体的实践方案。

硬件是基于FPGA1P1C6F256C8。

在进行硬件设计时,是用VHDL语言来描述整个算法的。

2智能PID控制器的设计原则

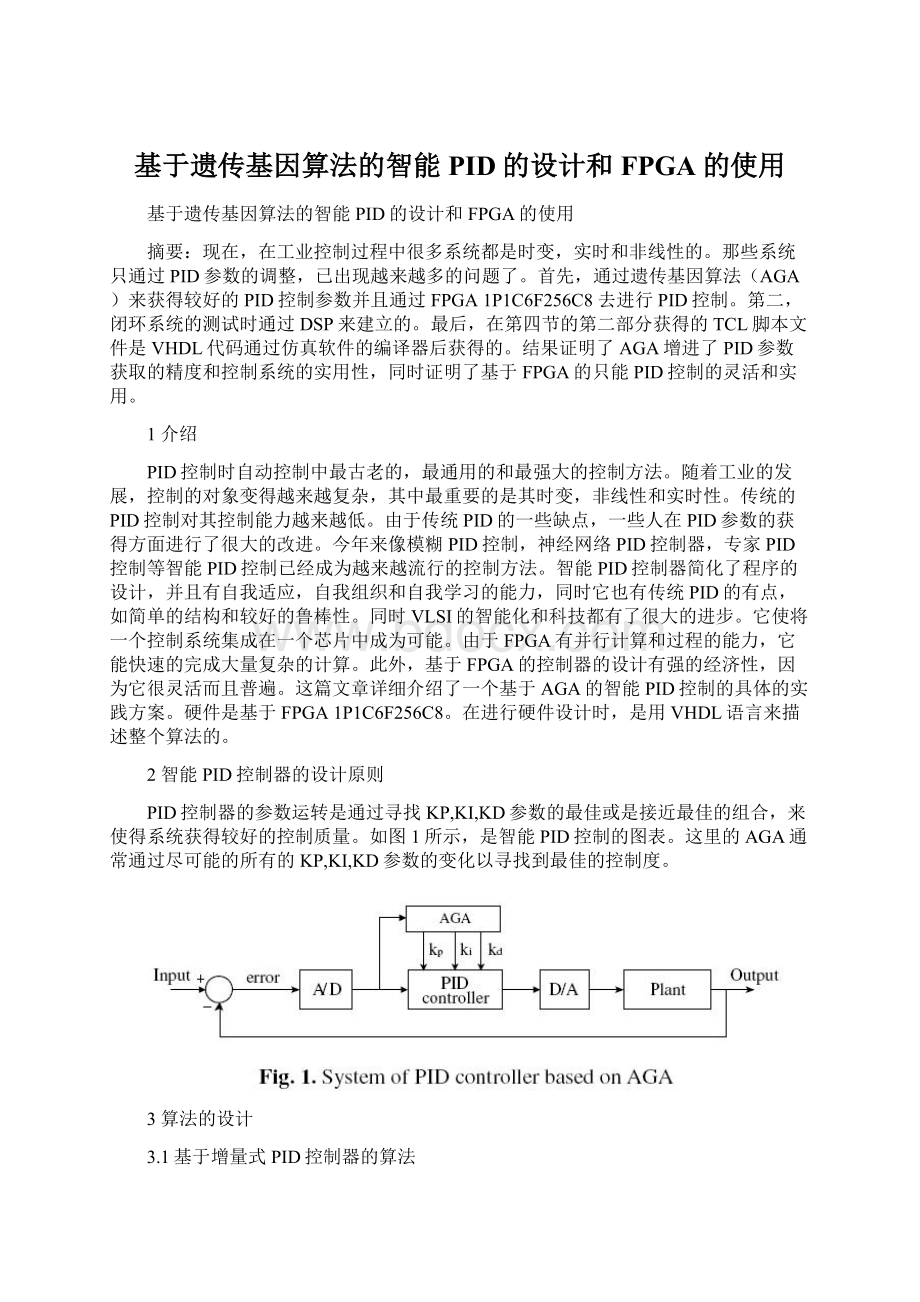

PID控制器的参数运转是通过寻找KP,KI,KD参数的最佳或是接近最佳的组合,来使得系统获得较好的控制质量。

如图1所示,是智能PID控制的图表。

这里的AGA通常通过尽可能的所有的KP,KI,KD参数的变化以寻找到最佳的控制度。

3算法的设计

3.1基于增量式PID控制器的算法

为了节省FPGA的硬件资源,PID控制器通常使用增量式PID算法。

如方程式1,如果我们知道u(k-1),e(k),e(k-1)的话,从方程式1中我们可以计算出u(k)

3.2自适应基因算法(AGA)

AGA采用,由适合度的值和循环次数决定的PC和PM的值,以避免不同步的聚焦,AGA的主要方面如下所示:

AGA采用实时编码。

它能增加结果的精度和超调的速度。

为了使FPGA的运行更加容易,AGA随机选取两个不同的个体,然后保留一个和它适合度一致的且最优的。

在AGA里,适合的参数被获得。

通过PC

在AGA里,合适的转化率获得。

计算适合度的函数

为了获得适合的动态参数。

我们可以通过ITAE来对象的函数,ITAE可以表达如下:

分离ITAE可以表示成:

4智能PID控制器的硬件设计

通过分析PID控制的条件和基因算法的特性,首先,我们将系统的函数模型转换成连续的电路和联合的逻辑电路。

第二步,我们进行系统时钟设计。

时钟就像一个系统的指挥官,命令所有的模块有序的工作。

在硬件的设计过程中,我们同样考虑包括运行的速度和资源的占用率,最后我们使他达到一个很好的平

衡。

4.1硬件的结构

如图2所示,智能PID控制器的硬件结构。

它主要包括初始化模块,选择模块,转接和转化模块,存储模块,多路器模块,随机数产生模块,双通道RAM模块,适合度计算模块,控制模块和增量式PID控制器。

RAM1是用存储个体对象的,而RAM2是用来存储个体对象的适合度值。

图3是增量式PID的硬件结构。

它主要包括暂存器,累加器多路器和控制器。

由于要提高速度和被加数的数据类型,增量式PID控制器要并行式的设计,并且多路器为了节省资源也要进行SBF。

E(K)存储在REG1中。

E(K-1)存储在REG2中,E(K-2)存储在REG3中。

中间的结果存储在REG4到REG9中。

4.2机械装置的正式设计

如果我们想让所有的模块都有序的工作,对时钟的控制时最关键的。

Statemachine对时钟控制来说是个很好的工具。

在一个单一的进程中模拟电路和逻辑电路可以联合进行。

它可以尽可能的避免出现故障。

这里我们用一个简单的过程图来模拟一下用statemachine来进行控制模块设计的过程。

4.2.1主要控制模块的设计

图4是图2里的主要控制模块的机器工作过程。

它包含6个主要的方面(IDLE,ST1,ST2,ST3,ST4,STOP)。

IDLE是一个复位步骤。

STOP是结束命令。

其他的是机器工作的四个过程。

每个的工作过程如下。

IDLE:

当异步复位信号从1变为0时,机器会立即跳转到“IDLE”状态。

在这个状态,所有的模块会开始发出一个初始化信号。

我们把这个过程叫做系统的初始化。

当初始化完成之后,机器进入下个状态:

ST1.

ST1:

系统的各个部分在这一步完成赋初值的过程。

当系统进入这个过程时,控制模块把START1信号变为1,然后赋给参数初始值。

在FPGA的时钟下,初始化模块同时产生一个新的数据信号和地址信号。

由多路器发出的数据信号和地址信号,是初始化模块在控制模块的控制下给与的。

在同一个时刻一个新的独立的行为由MUXB按照2:

1的比例在PID控制器上执行,同时初始化模块由MUXC按照2:

1的比例来计算适合度的值。

当适合度的值计算完成以后,适合度模块就会得到一个结束信号。

当接收的一个OVER的结束信号,初试化模块会通过MUXA按照2:

1的比例产生一个在RAM1和RAM2里运行的WR1的写信号。

然后这个个体和适合度的值会同时分别的写进RAM1和RAM2里,当一个个体存储完成以后,个体计数器会加一。

然后根据个体的数量是否达到了群组的值决定初始化模块是否跳转。

如果还没达到,初始值模块会重新得到一个新个体,如果达到了,初始值模块会得到一个OVER1的结束信号应且将START1的信号值改为0以关闭初始值模块,然后机器会跳转到下一个状态ST2。

ST2:

在这一个模块系统主要完成参数的选择。

当进入这个状态时,系统将ST2信号值变为1,然后开始参数的选择。

随机模块会由多路器随机产生两个在RAM1和RAM2上运行的不同的地址信号AD1和AD2。

然后选择模块同时同群组里选择两个不同的个体,保留那个个体与其适合度最优的。

当选择完成以后,选择模块会产生一个OVER2的结束信号,并且将START2的信号值变为0以关闭选择模块,然后机器跳转到ST3状态。

ST3:

系统完成参数的分频和转变在这个部分。

当进入这个环节后,控制模块将START3信号环节变为1,然后进行参数的变频和转变。

两个来自选择模块的个体会首先根据PC进行分频和通过PM进行转换,然后我们就得到了两个新的个体,分频器和转换器会发出一个OVER3的选择结束信号,然后将STAR3的信号值变为0以便关闭分频器和转换器模块,接着机器跳转到ST4状态。

ST4:

系统在这个环节完成主要操作数的存储。

进入这个环节以后,控制模块将START4的信号值变为1,然后开始操作数的存储。

这个存储过程跟初始值的存储过程时相似的。

当一个个体存储结束,个体计数器就加一。

如果新的个体的数量达到了群组的值,迭代计数器就加一。

控制模块根据要求的迭代次数来决定是否跳转,如果没有达到,机器就会跳到ST2状态去继续执行遗传算法的计算,如果达到了机器就跳转到STOP状态。

STOP:

当来到STOP状态,遗传算法已经结束,然后个体的最优数据“BESTDATA”会被输出,并且通过MUXB按照2:

1的比例在PID控制器上执行。

STOP状态不存在下一个状态。

机器在这个时候处于停顿状态。

当异步的复位信号RESET变为有效时,系统会跳转到IDLE状态。

我们不会在STOP状态时来确定RESET信号,因为他们异步信号。

4.2.2机器的控制模块在增量式PID控制器中的设计

图5是在图3中所示的机器的控制模块。

IDLE状态是一个复位状态。

ST1,ST2,ST3,和ST4是四个工作状态。

在每个时钟的上升沿,机器会从当前状态进入下一个状态。

这些状态的转化过程如下所示:

IDLE:

当控制信号CLEAR的值变为1时,系统会进入IDLE状态。

有些迭代器会在这个状态赋初值。

ST1:

REG1,REG2,REG3在这个状态会移位。

REG2的值会在REG3里被改变。

REG1的值会在REG2里被改变。

ERROR(K)的值会在REG1里被改变。

KP,KI,KD的总和会被存储在REG4里。

KP和2KD的和会被存储在REG5里。

KD会被存储在REG6里。

ST2:

控制模块使REG7,REG8,REG9能够工作。

【(KP+KI+KD)*E(K)】的值会存储在REG7,【(KP+2KD)*E(K-1)】会存储在REG8里。

【KD*E(K-2)】会存储在REG9里。

ST3:

控制模块会使REG10输出U(K)

5仿真与实践

因为智能PID控制器的开环系统的仿真不能精确的模拟输入信号,所以本篇论文用基于QUARTUSII6.0,DSPBUILDER6.0,MODELSIMSE6.1F和SIMULINK6.0的闭环系统来进行仿真。

测试的步骤如下。

STEP1:

用DSPBUILDER的HDL输入工具,输入VHDL代码进行仿真和测试模块的设计。

STEP2:

当测试模块正确的运作完后。

将.MDL格式文件转换成VHDL文件和TCL脚本文件,以便让信号编译器的仿真软件识别。

STEP3:

设置VHDL文件和TCL脚本文件。

STEP4:

运行MODELSIM里的测试文件,应且检查测试结果。

图6是DSPBUILDER里的智能PID的测试计划。

系统的传递函数可以表示为

AGA的参数设置如下。

群组的容量是32.PC_MAX是0.125。

PC_MIN是0.125。

PM_MAX是0.5,PM_MIN是0.0625。

ITMAX是128.如图7所示在参数运行以后我们可以分别获得KP,KI,KD的值为3.25,5.5,0.625,图8是图6的SCOPE1的仿真曲线。

从图8我们可以看出系统的输出有一点轻微的超调。

但是最后系统获得了一个稳态值1.图8(b)是图6的SCOPE3的仿真曲线。

图8(c)是图6的scope2的仿真曲线。

PID控制器的输出曲线最终稳定在1O。

图9是智能PID控制器在仿真软件里的RTL水平电路的仿真曲线。

控制器的输出和误差信号的输入是按照模拟量来进行的。

从图9我们可以看出,当输出值从0上升到稳态值9F9的时候,误差信号从1下降到0.因为输出结果是用SBF来表达的(高8位是积分部分,低8位是微分部分),9F9的十进制为9.97265625,仿真的结果与在MATLAB中的仿真结果基本一样。

当正确的完成上述工作以后,我们把所有的设计用QUARTUSII的语法环境下载到FPGA1P1C6F256C8中。

6结论

AGA用来获得PID控制器的最佳参数。

仿真结果证明了AGA增强了全局的搜索能力,并且提高了GA的聚焦速度。

这个方法是灵活且使用的。

通过DSP建立的PID控制器的闭环测试,模拟和仿真软件解决了控制器输入信号测试的样本资源。

它能快速的模拟控制器的输入行为,增强了设计和测试的灵活性,同时测试结果也是可靠和有说服力的。

在FPGA上进行智能控制器的设计有很多有点如,设计灵活,在线的自我运转,可靠性高,开发周期短和速度快。