计算机微指令对应的机器码.docx

《计算机微指令对应的机器码.docx》由会员分享,可在线阅读,更多相关《计算机微指令对应的机器码.docx(26页珍藏版)》请在冰豆网上搜索。

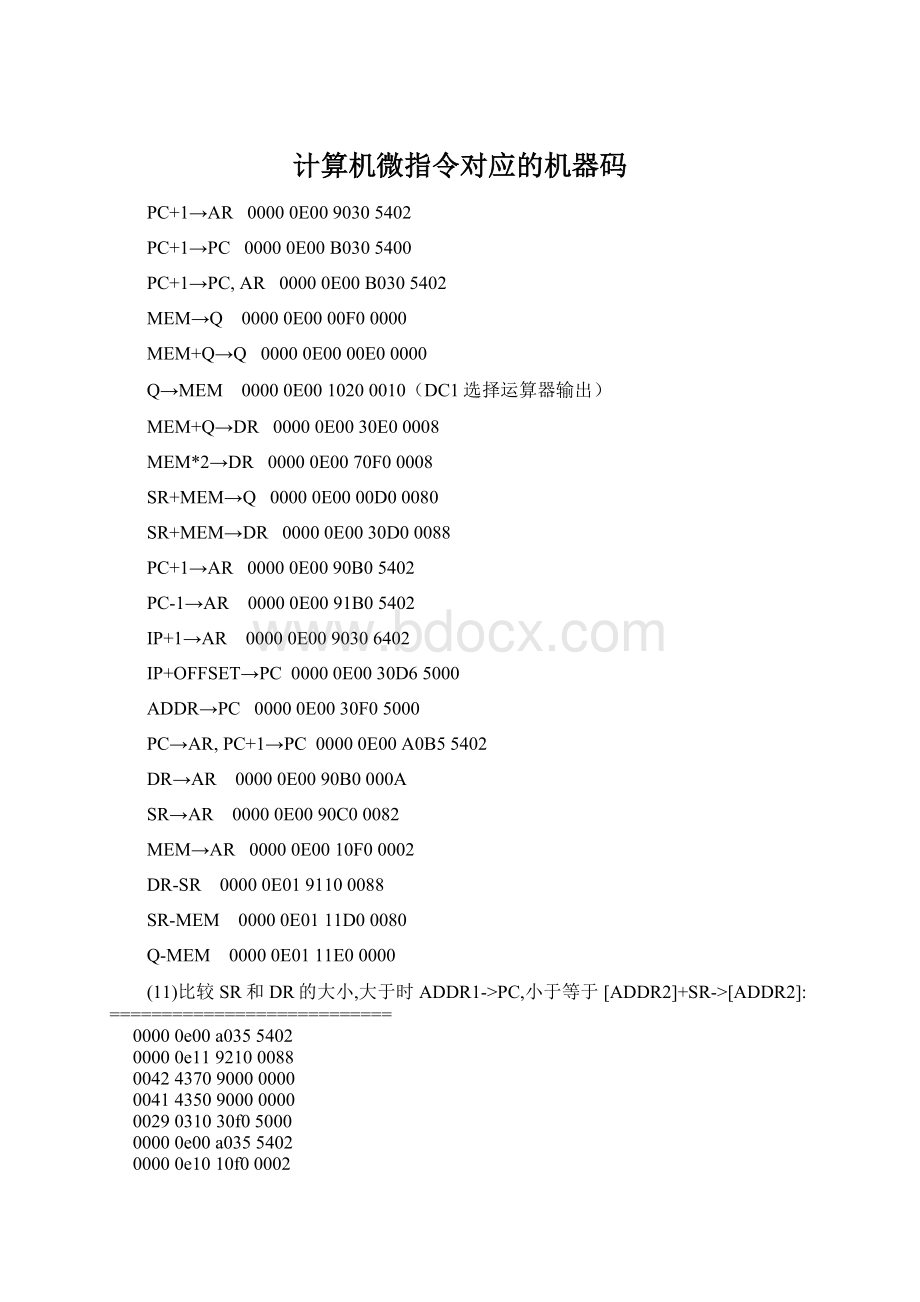

计算机微指令对应的机器码

PC+1→AR00000E0090305402

PC+1→PC00000E00B0305400

PC+1→PC,AR00000E00B0305402

MEM→Q00000E0000F00000

MEM+Q→Q00000E0000E00000

Q→MEM00000E0010200010(DC1选择运算器输出)

MEM+Q→DR00000E0030E00008

MEM*2→DR00000E0070F00008

SR+MEM→Q00000E0000D00080

SR+MEM→DR00000E0030D00088

PC+1→AR00000E0090B05402

PC-1→AR00000E0091B05402

IP+1→AR00000E0090306402

IP+OFFSET→PC00000E0030D65000

ADDR→PC00000E0030F05000

PC→AR,PC+1→PC00000E00A0B55402

DR→AR00000E0090B0000A

SR→AR00000E0090C00082

MEM→AR00000E0010F00002

DR-SR00000E0191100088

SR-MEM00000E0111D00080

Q-MEM00000E0111E00000

(11)比较SR和DR的大小,大于时ADDR1->PC,小于等于[ADDR2]+SR->[ADDR2]:

===========================

00000e00a0355402

00000e1192100088

0042437090000000

0041435090000000

0029031030f05000

00000e00a0355402

00000e1010f00002

00000e1000d00080

0029031010200010

00000e10b1100088

00290300b0355400

>a800

↙

movr1,900

movr2,b

movr3,100

ldmc

ret

>g800↙

>a820↙

movr0,2

movr1,4

movr2,3

mov[0890],r2

nop

nop

nop

ret

>e828↙

d41008800890

>a880↙

movr3,100

ret

>g820↙

(12)设计一条条件转移指令。

将SR与内存单元DATA的值进行比较,如果SRDR,否则ADDR->PC

===========================

指令格式:

D4 DR SR

DATA

ADDR

100:

PC->AR,PC+1->PC(data) 00000E00A0B55402

101:

MEM->Q(data=88) 00000E0000F00002

102:

SR-Q,标志 00000E0192800088

103:

S=1时跳到107,否则顺序104 0041D3B080000000

104:

PC->AR(addr) 00000E00A0B55002

105:

MEM->PC(addr=082A) 00000E1030F55000

106:

CC#=0退出 0029030090100000

107:

SR+Q->DR,标志 00000E10B0800088

108:

PC+1->PC,CC#=0退出 00290300B0B55400

>A800↙

0800:

MOVR1,900 ;微码在内存中的首地址

0802:

MOVR2,9 ;共9条微指令

0804:

MOVR3,100 ;微码在微控存中的首地址

0806:

LDMC ;加载微码指令

0807:

RET

0808:

>G800↙ ;加载微指令到控制存储器

>A820↙

MOVR1,99 ;R1是指令中的SR,用它和DATA比较

NOP

NOP

NOP

RET

>A82A↙

MOVR8,D ;大于等于时,将会跳到82A执行这条赋值指令

RET

>E822↙

输入以下内容:

D4218882A

运行结果

>G820↙ ;运行程序

结果:

1.SR SR=99

DATA=100

DR=199

2.SR≥DATA时

SR=99

DATA=99

R8=000D

(13)设计一条指令,比较SR内容与[ADDR].如果SR<[ADDR],则SR+[ADDR]->[ADDR];否则SR-[ADDR]->[ADDR].

===========================

100H:

PC->AR,PC+1->PC:

00000E00A0B55402

101H:

MEM->AR:

00000E0010F00002

102H:

SR-MEM->Q:

00000E0101D00080

103H:

条件转移:

004143B090800000

104H:

Q->MEM,CC#=0:

0029030010200010(SR>=MEM)

105H:

SR+MEM->Q:

00000E0000D00080(SR106H:

Q->MEM,CC#=0:

0029030010200010

>A800

↙

MOVR1,900

MOVR2,7

MOVR3,100

LDMC

RET

>G800↙

>A820↙

MOVR7,0001

MOVR1,0002

MOV[082A],R1

NOP

NOP

RET

>E826↙

D407082A

>G820↙

可以节省一条语句,在执行到105H的时候,让他无条件跳转到104H,就可以了!

则:

105H:

SR+MEM->Q,条件转移:

00410E0000D00080(SR舍弃106H

(14)设计一条指令,比较SR内容与[ADDR].如果SR<[ADDR],则IP+OFFSET->PC;否则SR+[ADDR]->DR.错误

===========================

100H:

PC->AR:

00000E0090B05002

101H:

MEM->AR:

00000E0010F00002

102H:

SR-MEM:

00000E0111D00080

103H:

条件转移:

004183B090800000

104H:

SR+MEM->DR,CC#=0:

00294E1030D00088

105H:

PC+1->AR:

00000E0090B05402

106H:

IP+MEM->PC:

0029030020D65000

(15)DR>[ADDR]则DR-[ADDR]->DR;DR<=[ADDR]则DR+[ADDR]->DR

===========================

00000e10a0355402

00000e1080300008

00000e1010f0000a

00000e1111e00000

0041c37090800000

0041c35090800000

0029031031e00008

0029031030e00008

>a800

↙

movr1,900

movr2,8

movr3,100

ldmc

ret

>g800↙

>a820↙

movr0,5

nop

nop

ret

>e822↙

d4000890

>e890↙

0003

>g820↙

设计一条减法指令

把内存单元数据DATA与用绝地址表示的内存单元ADDR的内容相减,结果存到DR寄存器中。

1.指令格式

指令格式:

D4

DR

X

ADDR

DATA

2.指令功能

功能:

DATA-[ADDR]→DR

3.设计分析

根据指令的功能和指令格式,先读取地址ADDR单元内容暂时放置于Q寄存器中,然后再读取内存单元数据DATA内容,同时与Q寄存器内容相减,结果也暂存放在Q寄存器中,最后把Q寄存器的运算结果传到DR中。

4.微程序

100:

PC→AR,PC+1→PC:

00000E00A0B55402

101:

MEM→AR:

00000E0010F00002

102:

MEM→Q:

00000E0000F00000

103:

PC→AR,PC+1→PC:

00000E00A0B55402

104:

MEM-Q→DR,CC#=0:

0029030132E00008

5.加载微码到微控存程序段

说明:

微码存放在900H(或某内存单元)开始的内存单元中

>A0800↙

0800:

MOVR1,900;微码在内存中的首地址

0802:

MOVR2,5;微指令条数

0804:

MOVR3,100;微码在微控存中的首地址

0806:

LDMC;加载微码指令,将微码指令加载到控存

0807:

RET

0808:

>G0800↙

6.运行程序段

>A0820↙

0820:

MOVR0,0004

0822:

MOV[0890],R0

0824:

NOP

0825:

NOP

0826:

NOP

0827:

RET

>E0824↙

然后输入以下内容:

D41008900013

7.运行结果

>G0820↙

>RR1↙

R1=0009

设计一条同值补码数符号扩展指令

设计一条指令,完成对存放在低位的8位有符号补码数进行符号扩展,即将其变为16位的同值得补码数,结果仍保存在原寄存器中。

8.指令格式

指令格式:

D4

DR

X

9.指令功能

功能:

对存放在低位的8位有符号补码数进行符号扩展,即将其变为16位的同值得补码数,结果仍保存在原寄存器中。

10.设计分析

正数的补码中符号位为0,各数位为其本身,负数的补码符号位为1,各数位为其的反,末尾再加一。

那么对于正数的扩展,直接在高8位添0即可。

对于负数的扩展,先假设把它还原成原码,符号位移动到最高位,然后变为反码,则高8位全为1,低8位与未扩展之前相同。

综上,可以把待扩展的补码数通过左移9位得到其符号位,保存在C中。

然后采用8次带符号位的右移操作,得到结果。

11.微程序

100:

8→RC:

0002040080800000

101:

2DR→DR:

00000806F0B00008

102:

8→RC:

0002040080800000

103:

DR/2→DR:

00000800D0B00108

104:

CC#=0:

0029030080000000

12.加载微码到微控存程序段

说明:

微码存放在900H(或某内存单元)开始的内存单元中

>A0800↙

0800:

MOVR1,900;微码在内存中的首地址

0802:

MOVR2,5;微指令条数

0804:

MOVR3,100;微码在微控存中的首地址

0806:

LDMC;加载微码指令,将微码指令加载到控存

0807:

RET

0808:

>G0800↙

13.运行程序段

>A0820↙

0820:

MOVR0,0029

0822:

MOVR1,00A9

0824:

NOP

0825:

NOP

0826:

RET

>E0824↙

然后输入以下内容:

D400

>E0825↙

然后输入以下内容:

D410

14.运行结果

>G0820↙

>RR0↙

R0=0029

>RR1↙

R1=FFA9

设计一条条件控制转移指令

设计一条指令,实现地功能是:

(说明:

其中有一种情况请用SCC=7,IR10~IR8=0~7的条件实现)

当DR=SR时,则IP+OFFSET→PC;

当DR否则执行下条汇编指令。

(注:

OFFSET为位移量;ADDR为某内存单元地址)

1.指令格式

指令格式:

D9

DR

SR

OFFSET

ADDR

2.指令功能

功能:

当DR=SR时,则IP+OFFSET→PC;

当DR否则执行下条汇编指令。

3.设计分析

指令通过比较DR和SR的大小实现语句的条件转移。

先对DR和SR作差得到运算结果标志Z和符号标志S。

首先根据Z进行转移,如果Z=1,那么说明DR=SR,跳转到CC#=0;否则顺序执行根据S进行转移,如果S=1,那么说明DRSR。

根据Z转移利用的是SCC=7,IR10~IR8=001的条件实现的,故操作码使用D9;而根据S转移是利用SCC=5的条件实现的。

4.微程序

110:

DR-SR,得到Z和S:

00000E0191100088

111:

PC→AR,PC→Q:

00000E0080305002

112:

IP+MEM→PC,Z=1跳转116:

004583F030D65000

113:

Q+1→Q,Q→AR:

00000E00B0200402

114:

MEM→PC,S=1跳转116:

004583B030F05000

115:

Q+1→PC:

00000E10B0205400

116:

CC#=0:

0029030080000000

或:

110:

DR-SR,得到Z和S:

00000E0191100088

111:

PC→AR,PC+1→PC,Z=1跳转114:

004503E0A0B55402

112:

PC→AR,PC+1→PC,S=1跳转115:

004543B0A0B55402

113:

CC#=0:

0029030080000000

114:

MEM+IP→PC,CC#=0:

0029030030D65000

115:

MEM→PC,CC#=0:

0029031030F05000

5.加载微码到微控存程序段

说明:

微码存放在900H(或某内存单元)开始的内存单元中

>A0800↙

0800:

MOVR1,900;微码在内存中的首地址

0802:

MOVR2,7;微指令条数

0804:

MOVR3,110;微码在微控存中的首地址

0806:

LDMC;加载微码指令,将微码指令加载到控存

0807:

RET

0808:

>G0800↙

6.运行程序段

>A0820↙

0820:

MOVR8,0001;运行三次,R8分别为0,1,2

0822:

MOVR9,0001

0824:

NOP

0825:

NOP

0826:

NOP

0827:

MOVR1,99;若DR>SR,输出99

0829:

RET

082A:

MOVR1,77;若DR=SR,输出77

082C:

RET

082D:

MOVR1,88;若DR082F:

RET

>E0824↙

然后输入以下内容:

D9890006082D

7.运行结果

>G0820↙

>RR1↙

R1=77(当R8=0时,R1=88,当R8=2时,R1=99)

设计一条半字交换指令

设计一条指令,其功能是把一个通用寄存器中的内容进行半字交换,即将其高低位字节的内容对换。

15.指令格式

指令格式:

D8

DR

X

16.指令功能

功能:

RAMH,RAML→RAML,RAMH

17.设计分析

将DR的内容送去Q。

利用DR和Q组成联合移位,联合右移8位后Q将为所求数,最后将Q送到DR,

18.微程序

100:

DR→Q,7→RC;0001C40080300008

101:

DRQ联合右移→DRQ;00000807C0300208

102:

Q→DR,CC#=0:

00290300B0200018

19.加载到微控存程序段

说明:

微码存放在900H(或某内存单元)开始的内存单元中

>A800↙

0800:

MOVR1,900;微码在内存中的首地址

0802:

MOVR2,3;微指令条数

0804:

MOVR3,110;微码在微控存中的首地址

0806:

LDMC;加载微码指令

0807:

RET

0808:

>G800↙

20.运行程序段

>A820↙

0820:

MOVR9,1289

0822:

NOP

0824:

RET

>E822↙

然后输入以下内容:

D890

21.运行结果

>G820↙

>RR9↙

R9=8912

设计一条条件控制处理与转移指令

设计一条指令,将SR的内容与内存单元数据DATA相比较,如果SR1.指令格式

指令格式:

D8

DR

SR

DATA

ADDR

2.指令功能

功能:

当SR当SR>=DATA时,则ADDR→PC

3.设计分析

本次实验要求完成的是一条条件控制指令。

首先,将DATA的地址放到AR,读出DATA放到寄存器Q,利用SR-Q得出标志位SF,再根据标志位SF判断跳转与否,如果SF=1,则跳到115,否则顺序执行114,之后再根据两个不同条件需要完成的操作实现。

4.微程序

110:

PC→AR,PC+1→PC;00000E00A0B55402

111:

MEM→Q;00000E0000F00000

112:

SR-Q;00000E0192000080

113:

SF=1跳转PC→AR,PC+1→PC0045004143B0A0355402

114:

MEM→PCCC#=0;0029030030F05000

115:

SR+Q→DRCC#=0;002903010300B0000088

5.加载微码到微控存程序段

微码存放在900H(或某内存单元)开始的内存单元中

>A800↙

0800:

MOVR1,900;微码在内存中的首地址

0802:

MOVR2,6;微指令条数

0804:

MOVR3,110;微码在微控存中的首地址

0806:

LDMC;加载微码指令,将微码写入控存

0807:

RET

0808:

>G800↙;加载微指令到控存

6.运行程序段

>A820↙

0820:

MOVR7,4444

0822:

MOVR8,4444

0824:

NOP

0825:

NOP

0826:

NOP

0827:

MOVR0,4444

0829:

RET

082A:

MOVR0,5555

082C:

RET

>E826↙

输入以下内容:

D8784445082A

7.运行结果

>G820↙

DATA>SR,DATA=4445,SR=4444,DR=8889

DATA=SR,DATA=4444,SR=4444,R0=5555

DATA设计一条加法指令

把用绝对地址表示的内存单元ADDR1的内容与内存单元ADDR2的内容相加,结果存到ADDR1单元中。

1.指令格式

指令格式:

D4XX

ADDR1

ADDR2

2.指令功能

功能:

[ADDR1]+[ADDR2]→[ADDR1]

1.设计分析

思路为先把PC指向ADDR2,然后先读取ADDR2,再PC减1,返回去读ADDR1的值,随后进行加法和赋值操作,最后把PC加3,使得PC返回,为执行下一条指令做好准备。

于是有以下操作步骤:

根据指令的功能和指令格式,先执行PC+1→PC,使得指向ADDR2。

读取地址ADDR2单元内容暂时放置于Q寄存器中,然后PC-1→PC,再读取地址ADDR1单元内容,同时与Q寄存器内容相加,结果也暂存放在Q寄存器中,此时,由于地址寄存器AR中存放的正好是地址ADDR1,因此只要将Q寄存器内容写入存储器就可以完成指令功能。

此后,微程序中必须再执行3次PC+1→PC操作,才能确保PC的正确走向。

2.微程序

100:

PC+1→PC:

00000E00A0B55400

101:

P