完整版PCIe总线基础及FPGA设计实战.docx

《完整版PCIe总线基础及FPGA设计实战.docx》由会员分享,可在线阅读,更多相关《完整版PCIe总线基础及FPGA设计实战.docx(26页珍藏版)》请在冰豆网上搜索。

完整版PCIe总线基础及FPGA设计实战

PCIExpress总线基础及FPGA设计实战

1.PCIExpress基础

PCIe总线是基于PCI总线发展起来的,很多基本概念都来自于PCI总线,有必要在介绍

PCIe之前了解PCI总线。

1.1PCI基础

pci总线作为处理器系统的局部总线,其主要目的是为了连接外部设备,而不是作为处理器系统的系统总线连接Cache和主存储器。

PCI总线作为系统总线的延伸,其设计考虑了许多与处理器相关的内容,孤立的研究PCI总线并不可取,因此需要将PCI作为存储器系统

的一个部分来研究。

1.1.1几个重要概念

1)PCI总线空间与处理器空间隔离

PCI设备具有独立的地址空间,即PCI总线地址空间,该空间与存储器地址空间通过HOST

主桥隔离。

处理器需要通过HOST主桥才能访问PCI设备,而PCI设备需要通过HOST主桥

才能方位主存储器。

PCI总

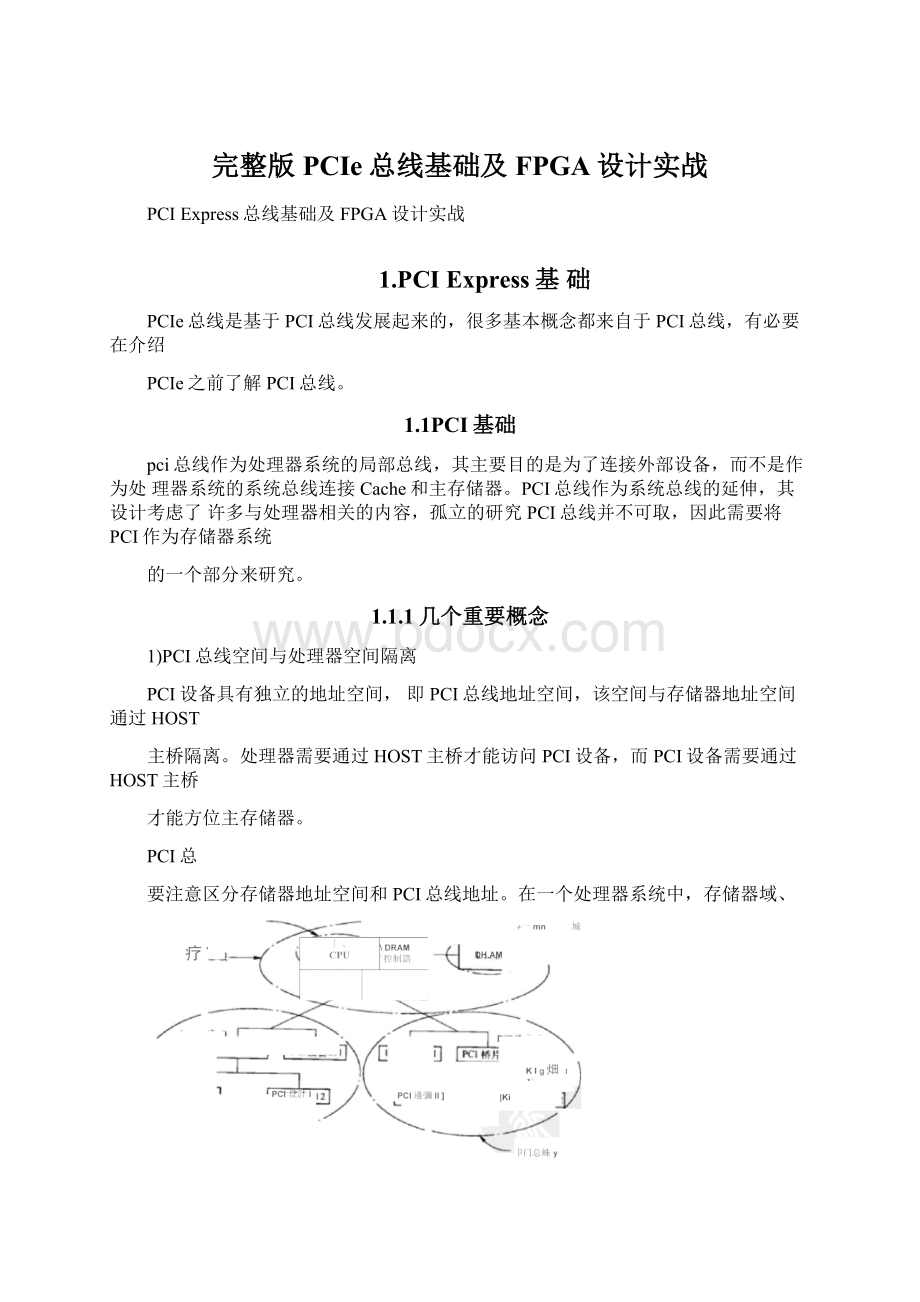

要注意区分存储器地址空间和PCI总线地址。

在一个处理器系统中,存储器域、

线域与HOST主桥的关系如下图。

图中的处理器系统由一个CPU

器系统中,包含CPU域、DRAM域、

存储器域与PCI总线域的划分

一个DRAM控制器和两个HOST主桥组成。

在这个处理存储器域和PCI总线域地址空间。

其中HOST主桥x和

HOST主桥y分别管理PCI总线x域与PCI总线y域。

CPU访问PCI设备,必须通过HOST主

桥进行地址转换,而PCI设备访问存储器设备,也需要HOST主桥进行地址转换。

HOST主桥

的一个重要作用就是将存储器访问的存储器地址转换成PCI总线地址。

CPU域地址空间是指CPU所能直接访问的地址空间集合。

DRAM域地址空间是指DRAM控制器所能访问的地址空间集合,又称为主主存储器域。

存储器域是CPU域和DRAM域的集合。

存储器域包括CPU内部的通用寄存器、存储器映射寻址的寄存器、主存储器空间和外部设备空间。

在Intel的x86处理系统中,外部设备

空间与PCI总线域地址空间等效。

因为在x86处理器系统中,使用PCI总线同一管理全部外部设备。

值得注意的是,存储器域的外部设备空间,在PCI总线域中还有一个地址映射。

当处理

器访问PCI设备时,首先访问的是这个设备在存储器域上的PCI设备空间,之后HOST主桥

将这个存储器域的PCI总线地址转换成PCI总线域的物理地址,然后通过PCI总线事务访问

PCI总线域的地址空间。

2)可扩展性

(包括PCI桥)。

PCI总线具有很强的扩展性。

在PCI总线中,HOST主桥可以直接推出一条PCI总线,这条总线也是该HOST主桥管理的第一条PCI总线,该总线还可以通过PCI桥扩展一系列PCI总线,并以HOST主桥作为根节点,形成1棵PCI总线树。

这些PCI总线都可以连接PCI设备,但是一棵PCI设备树上,最多只能挂接256个PCI设备

PCI总线使用这种方式合理地

PCI设备都有独立的配置空BAR地址,从而保证每一个PCI'PCI子树所能使用的地址范

3)动态配置机制

PCI设备使用的地址可以根据需要由系统软件动态分配。

解决设备间的地址冲突,从而实现了“即插即用”功能。

每一个间,在配置空间中包含该设备在PCI总线中使用的基地址即

设备使用的物理地址并不相同。

PCI桥的配置空间中包含有其下

围。

x86系统的工作流程是:

主板上的BIOS程序会扫描PCI/PCIE设备,读取其BAR空间的大小,动态地为PCI/PCIE设备分配地址空间。

在调试过中发现,假如将BAR空间设置成2G,x86系统会报nobootabledevice的错误,原因应该是BIOS给PCIE设备分配了2G的地址空间,暂用了硬盘的地址空间,导致无法加载操作系统。

4)总线带宽

PCI总线与之前的局部总线相比,极大提高了数据传送带宽,32位/33MHz的PCI总线

可以提供132MB/S的峰值带宽,而64位/66MHz的PCI总线可以提供的峰值带宽为532MB/S。

虽然PCI总线所能提供的峰值带宽远不能和PCIe总线相比,但是与之前的局部总线ISAEISA

和MCA总线相比,仍然具有极大的优势。

ISA总线的最高主频为8MHz,位宽为16,其峰值带宽为16MB/S;EISA总线的最高主频为8.33MHz,位宽为32,其峰值带宽为33MB/S;而MCA总线的最高主频为10MHz,最高位宽为32,其峰值带宽为40MB/S。

PCI总线提供的峰值带宽远高于这些总线。

P思红赣覃•帚畫与如赠之阎妁姜JK

总竣类煨

饮戟龍力

PC1

■

*

33

*-5

PCIX

--巴一^

"

2M

—-一—一

1_—

——■

2个楠能

—■

1Ttrtw

533

2UI

1牛插摘

♦i—0

5)共享总线机制

PCI设备通过仲裁获得PCI总线的使用权后,才能进行数据传送,在PCI总线上进行数

据传送,并不需要处理器进行干预。

PCI总线仲裁器不在PCI总线规范定义的范围内,也不

一定是HOST主桥和PCI桥的一部分,虽然绝大多数HOST主桥和PCI桥都包含PCI总线仲裁器,但是在某些处理器系统设计中也可以使用独立的PCI总线仲裁器。

PCI设备使用共享总线方式进行数据传递,在同一条总线上,所有PCI设备共享同一总

线带宽,这将极大地影响PCI总线的利用率。

这种机制显然不如PCIe总线采用的交换结构。

6)中断机制

PCI总线上的设备可以通过四根中断请求信号INTA~D#向处理器提交中断请求。

与ISA

总线上的设备不同,PCI总线上的设备可以共享这些中断请求信号,不同的PCI设备可以将

这些中断请求信号线与后,与中断控制器的中断请求引脚连接。

PCI设备的配置空间记录了

该设备使用这四根中断请求信号的信息。

PCI总线还进一步提出了MSI(MessageSignalInterrupt)机制,该机制使用存储器写总线事务传递中断请求,并可以使用x86处理器FSB(FrontSideBus)总线提供的InterruptMessage总线事务,从而提高了PCI设备的中断请求效率。

1.1.2PCI总线的组成结构。

图(-1AEFPC1总线的处理器系统

图中与PCI总线相关的模块包括:

HOST主桥、PCI总线、PCI桥和PCI设备。

PCI总线是

由HOST主桥和PCI桥推出,HOST主桥与主存储器控制器在同一级总线上,因此PCI设备可

以方便通过HOST主桥访问存储器,即进行DMA操作。

在一些简单的处理器系统中,可能不包含PCI桥,此时所有PCI设备都是连接再HOST主桥上推出的PCI总线上。

在一些处理器系统中有可能有多个HOST主桥,如图1-1所示处理器系统中含有HOST主桥x和HOST主桥y。

X86处理器的HOST主桥

X86处理器使用南北桥结构连接CPU和PCI设备。

其中北桥连接快速设备,如显卡和内

存条,并推出PCI总线,HOST主桥包含在北桥中。

而南桥连接慢速设备。

图2-6湍&处理器的南北桥结构

1.2PCIE总线概述

PCI总线使用并行总线结构,在同一条总线上的所有外部设备共享总线带宽,而PCIe总

线使用高速查分总线,采用端对端的连接方式,因此在每一条PCIe链路中只能连接两个设

备。

这使得PCIe与PCI总线采用的拓扑结构有所不同。

PCIe总线除了在连接方式上与PCI

总线不同之外,还使用一些在网络通信中使用的技术,如支持多种数据路由方式,基于多通

路的数据传递方式,和基于报文的数据传送方式,并充分考虑在数据传送中出现的服务质量QoS(QualityofService)问题。

1.2.1基于PCIe的系统结构

前期的Intel主板中会集成单独的南北桥芯片,北桥负责连接速度较快的CPU、主存储

器以及显卡等元件,南桥负责连接速度较慢的设备,包括硬盘、USB网卡等。

只要CPU读

取主存储器,还需要北桥的支持,也就是CPU与主存储器的交流,会占用北桥的带宽。

因

此新一代的Intel主板架构,大多将北桥存储控制器整合到CPU封装中,CPU直接与主存储

器交互,速度较快。

主存储器的速度

SDRAM/DDR

型号

数据位宽

内部时钟

频率速度

带宽

SDRAM

PC100

64

100

100

800MBytes/sec

SDRAM

PC133

64

133

133

1064MBytes/sec

DDR

DDR-266

64

133

266

2.1GBytes/sec

DDR

DDR-400

64

200

400

3.2GBytes/sec

DDR

DDR2-900

64

200

800

6.4GBytes/sec

DDR

DDR3-1600

64

200

1600

12.8GBytes/sec

PCIe总线带宽

规格

1x带宽

16x带宽

PCIe1.0

250Mbytes/sec

4GBytes/sec

PCIe2.0

500Mbytes/sec

8GBytes/sec

PCIe3.0

~1GBytes/sec

16GBytes/sec

PCIe4.0

~2GBytes/sec

32GBytes/sec

SATA总线带宽

版本

带宽

SATA1.0

150Mbytes/sec

SATA2.0

300Mbytes/sec

SATA3.0

600Mbytes/sec

USB总线带宽

版本

带宽

USB1.0

1.5Mbytes/sec

USB2.0

60Mbytes/sec

USB3.0

500Mbytes/sec

USB3.1

1000Mbytes/sec

1.2.2端到端的数据传递

PCI总线不同,PCIe总线采用端到端的连接方式,在一条PCIe链路的两端只能各连接个设备,这两个设备互为数据发送端和数据接收端。

笈送禺按收濟

Fta馅linkerlaynPhysicalUyer皿倔Lin^(aycr

图4-1兀花总线的物理链路

在PCIe总线的物理链路的一个数据通路(Lane)中,有两组查分信号,共4根信号线。

其

中发送端的TX部件与接收端的RX部件使用一组差分信号连接,该链路也被称为发送端的发送链路,也是接收端的接收链路;而发送端的RX部件与接收端TX部件使用另一组查分

信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。

一个PCIe链路可以由多个数据通路Lane组成,目前PCIe链路可以支持1、2、4、8、

16和32Lane,即x1、x2、x4、x8、x16、x32宽度的PCIe链路。

視4-1PCfe总线屈范耳总拔锁军和第码的关黑

PCIe爲織氓柜

妁硏方式

J

J.U

丸、|15

:

S_

—

#/10b妨別

10

4

8

H理卑同总鏡欄呻持星井牯寸疫加摟悅”0”和-r世践僮览肿的槪莘

PCIe总线物理链路间的数据传送使用基于时钟的同步传送机制,但是在物理链路上并没

有时钟线,PCIE总线的接收端含有时钟恢复模块CDR(ClockDataRecovery),CDR将从接收

报文中提取接收时钟,从而进行同步数据传递,PCIe设备进行链路训练时将完成时钟的提取

工作。

123PCIe总线的层次结构

PCIe总线采用串行连接方式,并使用数据包(Packet)进行数据传输。

在PCIe总线中,

数据报文在接收和发送过程中,需要通过多个层次,包括事务层、数据链路层和物理层。

图4-4PCIE’prw总线的层次组成結构

PCIe总线的层次组成结构与网络中的层次结构有类似之处,但PCIe总线的各个层次都是用

硬件逻辑实现的。

在PCIe体系结构中,根据报文首先在设备的核心层(DeviceCore)中产

生,然后再经过该设备的事务层(TransactionLayer)、数据链路层(DataLinkLayer)和物理

层(PhysicalLayer),最终发送出去。

而接收端的数据也需要经过物理层、数据链路层和事务层,最终到达核心层。

1.事务层

事务层定义了PCIe总线使用总线事务,其中多数总线事务与PCI总线兼容。

这些总线

事务可以通过Switch等设备传送到其他PCIe设备或者RC设备。

RC设备也可以使用这些总线事务访问PCIe设备。

事务层接收来自PCIe设备核心层的数据,并将其封装成TLP(TransactionLayerPacket)后,发向数据链路层。

此外事务层还可以从数据链路层中接收数据报文,然后转发至PCIe

设备的核心层。

2.数据链路层

数据链路层保证来自发送端事务层的报文可以可靠、完整地发送到接收端的数据链路层。

来自事务层的报文在通过数据链路层时,被添加SequeneeNumber前缀和CRC后缀。

数据

链路层使用ACK/NAK协议保证报文的可靠传递。

PCIe总线的数据链路层还定义了多种DLLP(DataLinkLayerPacket),DLLP产生于数据链

路层,终止与数据链路层。

3.物理层

物理层是PCIe的最底层,将PCIe设备连接再一起。

PCIe总线的物理电气特性决定了PCIe

链路只能使用端到端的连接方式。

PCIe总线的物理层为PCIe设备间的数据通信提供传送介

质,为数据提供可靠的物理环境。

1.2.3PCIe体系结构的组成结构

PCIe总线作为处理器系统的局部总线,其作用于PCI总线类似,主要目的是为了连接处

理器系统中的外部设备。

在大多数处理器系统中,都使用RCSwitch和PCIe-to-PCI桥这些基

本模块连接PCIe和PCI设备。

在PCIe总线中,基于PCIe总线的设备,也成为EP(Endpoint)。

基于PCIe总线的通用处理器系统如下图

EPEP

图4-9基rPCk总线的通用处理器系统

图中所示的结构将PCIe总线端口、存储器控制器等一系列与外部设备有关的接口都集成在一起,并统称为RCoRC具有一个或者多个PCIe端口,可以连接各类PCIe设备。

PCIe设备包括(网卡、显卡等设备)、Switch和PCIe桥。

PCIe总线采取端到端的连接方式,每一个PCIe端口只能连接一个EP,当然PCIe端口也

可以连接Switch进行链路扩展。

通过Switch扩展出的PCIe链路可以继续挂接EP或者其它

Switcho

2.基于FPGA的PCIe总线分析

2.1硬件系统设计

本章将采用xilinx的FPGA芯片搭建一个RC端和EP端的硬件平台,用于仿真学习PCIe总线相关的知识包括DMA操作、地址映射等,以及xilinx的AXIMemoyMappedTOPCIExpress、AXIDMA等IP使用。

2.1.1RC端系统设计

RC端硬件系统由MicroBlaze处理器、R(采用xilinx的AXIMemonyMappedToPCIExpress配置成RC模式)、内存(采用内置BRAM块)、常用外设包括GPIO串口。

地址分配

Bcvfl

64K

,!

T

0«0§QQ_FT?

r

亍•叵^izi_Epia_!

0

Gn

ass

Ox;IG匚少泌

&-LK

TF

Om:

4JOD_?

IFT

■™{■Zl.lA.tc_0

a_ajj

Befi

石辽

V

OKU2CJI5T

□jm

OiKKCJOM

*

OmCMCJIFT

5_AM_CIL

CIS

。

疥DOC.IM®

»

加WF」T打

wiJMTtlit

恥岸

昏之

m.-a.FFFF

rl^-sicrz'bl-izfljD

BaJLfe.02HdkLrKEIlIe.AG)

■■U1_t1tjl_'

MX.

伽做[」幷『

■皿二加皿

芍JUT

OSiWu_l»M

翳JC

¥

"E.inXjO

肌

DM垢口JM冈

触X

■w

owustjm

口aiijcie-jO

S^AIT

E和

0吨刃匚_K)卫

64K

■T

OaCOQDJIJr

:

azi_pcie_:

O

SJUJ1L

CILO

0m5MC_COM

0=<53i?

_?

i5t

2fSKi_a*rllrte_O

SJX1

Rte

Ojti«C_CO:

C

向

*

0?

ti:

4C_!

T?

F

*,nhi託理e_Q_l-;fa]|_ristwrWdlnb

Irin.

Wtr

0浦CW_t祝。

1.彌

V-

TISluirvTitn4;;斥

nirTzllojAOJ^-eralfimorTy1lLnli

ferun.

皿E

Van

Die&MCJOM

LZSK

耳

Ok&ZGI^T'T

2.1.2EP端系统设计

EP端硬件系统由MicroBlaze处理器、E(采用xilinx的AXIMemonyMappedToPCIExpress配置成EP模式)、DMA以及内置BRAM块。

地址分配

■Jui_(ifiai_Cl

■j^rljO

SJIL

**

OiOKOjMW)

32X

oioeoo/rrTF

S_AII

旨也

■

^■raiojjyF

™EV3a

Sjar/TL

tnx

血LOGOJ»卿

255M

OxlFFF»IF

icEkfl1AJiL'^EE

£AZL^LirE

iji2DMjidOO

6dX

&z2OQ0-_FITp-

=3J-alienstits,■=:

.

asjan_cIrljO

S_AI:

■■srf

bOBGOJHM

洛

6toaa_7i?

F

3Nl古1*_CI

3匸

OiCTOJITF

S_AII_CIL

CIU

asLEKM.XOT

■

JI!

?

Ufid.d»1加誑生■代

kb>uri_anaJD

»平■中E

Ig

exijj3ci.e_0

USH_AIZ七亡“Ln=:

uJtrnn_erar1_C

SJkiL

H":

32S

■r

OtOBO&JTTJT

oaa_Si

£_All_LItE

»

OiOSOOjnF

™ua_s-sit_Q

sjar

>AfL

■3a■w

cruo

OjLQGOjMOT

■

QilfFFRTF

2.2读写数据分析

2.2.1读写MEM数据

操作地址为RC端BAR空间存储器域地址+偏移量

例如,往EP端偏移量为0x1000的MEM写数据,RC端写地址为0xC000_000+0x10000xC000_000为RC端axi_pcie_bar0基地址,即EP端PCIe域基地址映射到RC端存储器地址域的基地址。

将RC端存储器域地址0xC000_1000,转换成EP端AXI地址0x0800_1000,最终写入到EP端MEM。

RC端存储器域PCI总线接口EP端PCIe总线域EP端AXI总线地址域

RC_AXIBAR2PCIEBAR_0=0xFFFF_0000EP_CFG_BAR0=0xFFFF_0000EP_PCIEBAR2AXIBAR0=0x0800_0000

0xC000_1000A0xFFFF_1000A0x0000_1000|A0x0800_1000

222DMA操作

DMA在EP端,源地址和目的地址为EP端AXI总线地址

0x0800_0000

0x0800_1000

0x0800_2000

0x08003000

2.2.2.1读内存

读内存指将RC端的内存的数据搬移到EP端MEM。

数据流图如下

RC端

EP端

源地址为0x4000_1000,RC端存储器域地址在EP端AXI总线域的映射地址目标地址为0x0800_2000,EP端AXI总线域地址

EP_AXIBAR2PCIEBAR_0=0xEEEE_0000RP_CFG_BARO=OxEEEE_OOOOEP_PCIEBAR2AXIBAR0=0x0600_0000

0x4000_1000OxEEEE_1OOOOxOOOO_1OOOA0x0600_1000

222.2写内存

写内存将EP端的数据写入RC端的内存。

数据流图

EP端

RC端

源地址为0x0800_1000,EP端AXI总线地址

目标地址为0x4000_2000,RC端存储器域内存地址在EP端AXI总线地址域的映射地址

EP端AX总线地址域PCIE总线接口RP端PCIE总线域RR端存储器域

EP_AXIBAR2PCIEBAR_0=0xEEEE_0000RP_CFG_BAR0=0xEEEE_0000EP_PCIEBAR2AXIBAR0=0x0600_0000

0x4000_20000xEEEE_2000二"0x0000_2000“0x0600_2000

3.设计实战

本章将搭建一个基于PCIex4的EP端硬件系统,并在安装Windows7的x86电脑上,使用WinDriver软件完成驱动开发。

3.1EP端硬件系统搭建

地址分配

AXIMemonyMappedToPCIExpress参数配置

1.将Device/PortType配置成功PCIExpressEndpointdevice

2.

将LaneWidth配置成x4,将LinkSpeed配置成5.0GT/S

产话」札密鼻Hl

WA.niLi.gaft■

zlm

Wi»T*T!

■UH肿

■闻黑

—£二

ITiflaTtp1_HW*■

EJIHJElJw

■HTe-^:

-rndthlnilv

3.

配置VendorID和DeviceID,驱动开发时将根据VendorID和DeviceID来扫描PCIe设备。

4.配置BAR0的地址空间为128K,配