数字电路期末复习题0.docx

《数字电路期末复习题0.docx》由会员分享,可在线阅读,更多相关《数字电路期末复习题0.docx(35页珍藏版)》请在冰豆网上搜索。

数字电路期末复习题0

第一套

一、选择题(本大题共10道小题,每小题2分,共20分。

)

1.用编码器对16个信号进行编码,其输出二进制代码的位数是()

A.2位B.3位C.4位D.16位

2.逻辑函数F=(A+B)(B+)的对偶式F′=()

A.+CB.AB+BC.+CD.AB+C

3.一个8选一数据选择器的地址输入端有_______个。

()

A.1B.2C.3D.4

4.同步时序电路和异步时序电路比较,其差异在于后者()

A.没有触发器B.没有统一的时钟脉冲控制

C.没有稳定状态D.输出只与内部状态有关

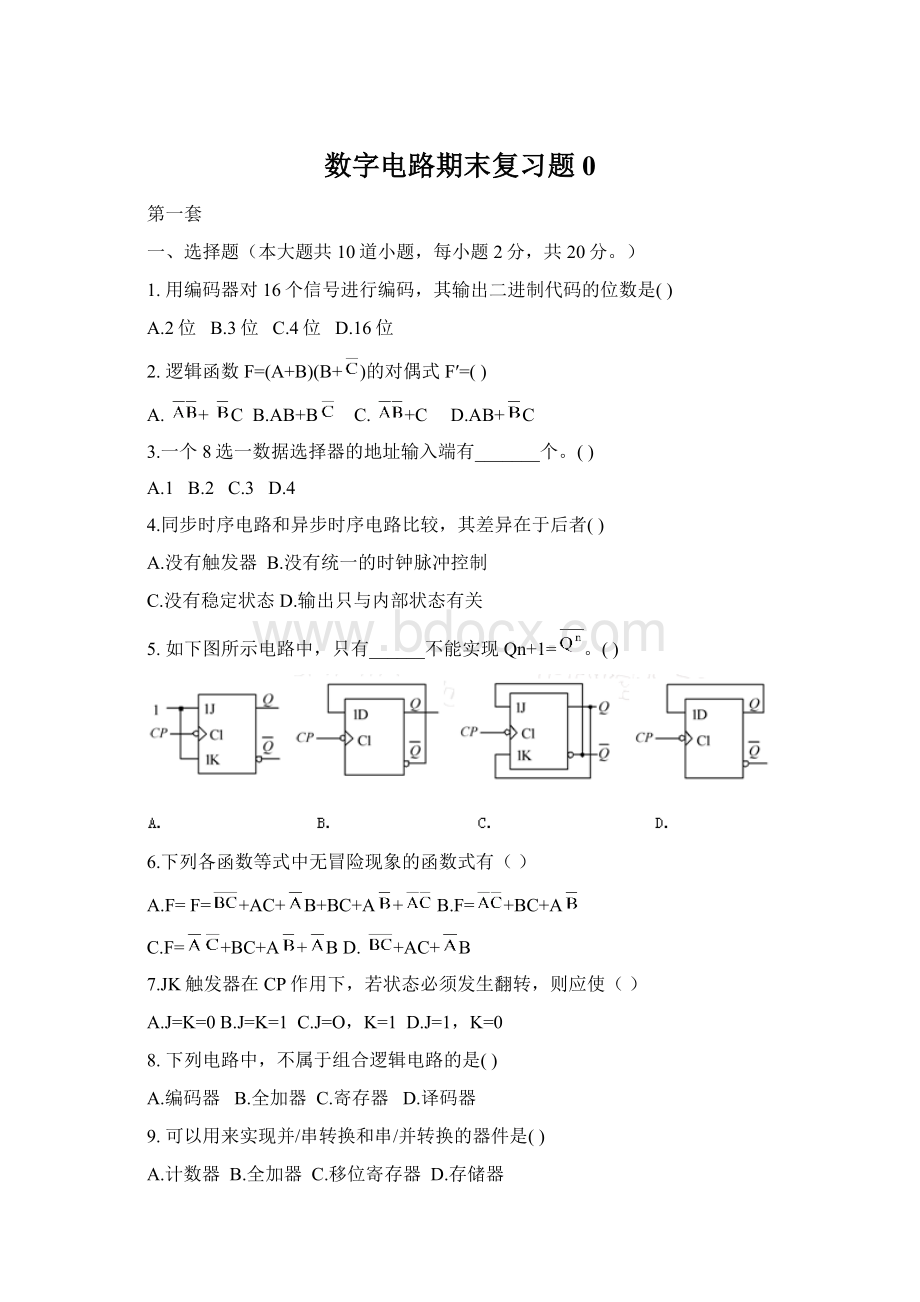

5.如下图所示电路中,只有______不能实现Qn+1=。

()

6.下列各函数等式中无冒险现象的函数式有()

A.F=F=+AC+B+BC+A+B.F=+BC+A

C.F=+BC+A+BD.+AC+B

7.JK触发器在CP作用下,若状态必须发生翻转,则应使()

A.J=K=0B.J=K=1C.J=O,K=1D.J=1,K=0

8.下列电路中,不属于组合逻辑电路的是()

A.编码器B.全加器C.寄存器D.译码器

9.可以用来实现并/串转换和串/并转换的器件是()

A.计数器B.全加器C.移位寄存器D.存储器

10.自动产生矩形波脉冲信号为()

A.施密特触发器B.单稳态触发器C.T触发器D.多谐振荡器

二、填空题(本大题共10道小题,每小题2分,共20分。

)

1.八进制数(34.2)8的等值二进制数为 ;十进制数98的8421BCD码为 。

2.二极管内含PN结,PN结在导电性能上的最大特点是_______________。

3.函数,其反函数为,对偶式为。

4.常见的脉冲产生电路有,常见的脉冲整形电路有。

5.A/D转换器的主要参数有,。

6.四位环型计数器和扭环形计数器,初始状态是1000,经过5个时钟脉冲后,状态分别为和。

7.对于JK触发器的两个输入端,当输入信号相反时构成触发器,当输入信号相同时构成触发器。

8.时序逻辑电路的输出不仅和_______有关,而且还与___________有关。

9.TTL或非门多余输入端应.三态门的输出除了有高、低电平外,还有一种输出状态叫态

10.D触发器的特征方程为,JK触发器的特征方程为。

得分

阅卷人

三、作图题(本大题共2道小题,每小题6分,共12分。

)

1、如下图所示,根据CP波形画出Q波形。

(设各触发器的初态均为1)

2、试说明如下图所示的用555定时器构成的电路功能,求出UT+、UT-和ΔUT,并画出其输出波形。

四、分析题

1.利用公式法将函数Y化简成最简与或式:

(本小题5分)

2.利用图形法将函数F化简成最简与或式:

F2(A,B,C,D)=∑m(0,1,2,4,5,9)+∑d(7,8,10,11,12,13)(本小题5分)

3.试分析图示电路,写出其驱动方程、输出方程、状态方程,画出状态转换图、说明其逻辑功能。

(本小题10分)

五、设计题

1.设计一个A、B、C三人表决电路,以表决某一提案是否通过,如多数赞成,则提案通过,同时A有否决权。

用4选1数据选择器74LS153来实现,连线时可附加适当门电路。

2.用同步四位二进制计数器74163构成八进制计数器,画出连线图。

74163引脚图和功能表如下图。

3.用JK触发器设计一个按自然态序进行计数的六进制同步加法计数器。

第二套

一、选择题

1.在四变量卡诺图中,逻辑上不相邻的一组最小项为:

()

A.m1与m3B.m4与m6C.m5与m13D.m2与m8

2.L=AB+C的对偶式为:

()

A.A+BCB.(A+B)CC.A+B+CD.ABC

3.属于组合逻辑电路的部件是()。

A.编码器B.寄存器C.触发器D.计数器

4.T触发器中,当T=1时,触发器实现()功能。

A.置1B.置0C.计数D.保持

5.指出下列电路中能够把串行数据变成并行数据的电路应该是()。

A.JK触发器B.3/8线译码器C.移位寄存器D.十进制计数器

6.某电路的输入波形uI和输出波形uO下图所示,则该电路为()。

A.施密特触发器B.反相器C.单稳态触发器D.JK触发器

7.三极管作为开关时工作区域是()

A.饱和区+放大区B.击穿区+截止区C.放大区+击穿区D.饱和区+截止区

8.已知逻辑函数与其相等的函数为()。

A.B.C.D.

9.一个数据选择器的地址输入端有3个时,最多可以有()个数据信号输出。

A.4B.6C.8D.16

10.用触发器设计一个24进制的计数器,至少需要()个触发器。

A.3B.4C.6D.5

二、填空题

1.八进制数(34.2)8的等值二进制数为 ;十进制数98的8421BCD码为 。

2.组合逻辑电路的冒险现象是由引起,表现为脉冲。

3.函数,其反函数为,对偶式为。

4.有一个稳定状态和一个暂稳状态。

有两个稳定状态、有两个不同的触发电平,具有回差特性。

5.A/D转换器的主要参数有,。

6.欲构成能计最大十进制数为999的计数器,至少需要片十进制加法计数器,或片4位二进制加法计数器芯片。

7.一个JK触发器有 个稳态,它可存储 位二进制数。

8.时序逻辑电路的输出不仅和_______有关,而且还与__________有关。

9.在使用与非门时多余的输入端应接电平,在使用或非门时多余的输入端应接电平。

10.n进制计数器中的n表示计数器的,最大计数值是。

三、作图题

1、555定时器应用电路如下图所示,若输入信号uI如图(b)所示,请画出uO的波形,说明这是什么电路。

2、主从型JK触发器各输入端的波形如下图所示,试画出Q端对应的电压波形。

四、分析题

1.利用公式法将函数Y化简成最简与或式:

2.利用图形法将函数F化简成最简与或式:

3.分析图5所示电路,写出Z1、Z2的逻辑表达式,列出真值表,说明电路的逻辑功能。

4.已知下图所示的时序逻辑电路,假设触发器的初始状态均为“0”,试分析:

(1)写出驱动方程、状态方程、输出方程。

(2)画出状态转换图,指出是几进制计数器。

(3)说明该计数器能否自启动。

五、设计题

1.试用两个3线-8线译码器和适当的门电路设计一个三人多数表决器。

2.用JK触发器设计一个按自然态序进行计数的六进制同步加法计数器。

第三套

一、选择题

1.下列电路中不属于时序电路的是()。

A.同步计数器B.异步计数器

C.组合逻辑电路D.数据寄存器

2.3线—8线译码器有()。

A.3条输入线,8条输出线B.8条输入线,3条输出线

C.2条输入线,8条输出线D.3条输入线,4条输出线

3.一个五位的二进制加法计数器,初始状态为00000,问经过201个输入脉冲后,此计数器的状态为()。

A.00111B.00101C.01000D.01001

4.若将一TTL异或门输入端A、B当作反相器使用,则A、B端的连接方式为()。

A.A或B中有一个接1B.A或B中有一个接0

C.A和B并联使用D.不能实现

5.下列各种电路结构的触发器中哪种能构成移位寄存器()。

A.基本RS触发器B.同步RS触

C.主从结构触发器D.SR锁存器

6.逻辑函数F(A,B,C)=AB+BC+AC'的最小项标准式为()。

A.F(A,B,C)=∑m(0,2,4)B.F(A,B,C)=∑m(1,5,6,7)

C.F(A,B,C)=∑m(0,2,3,4)D.F(A,B,C)=∑m(3,4,6,7)

7.设计一个把十进制转换成二进制的编码器,则输入端数M和输出端数N分别为()

A.M=N=10B.M=10,N=2

C.M=10,N=4D.M=10,N=3

8.数字电路中的工作信号为()。

A.直流信号B.脉冲信号

C.随时间连续变化的电流信号D.随时间连续变化的电压信号

9.L=AB+C的对偶式为:

()

A.A+BCB.(A+B)CC.A+B+CD.ABC

10.自动产生矩形波脉冲信号为()

A.施密特触发器B.单稳态触发器C.T触发器D.多谐振荡器

二、填空题

1.(101011111)2=()16=()8421BCD

2.在数字电路中三极管工作在和状态,所以数字电路只有两个状态。

3.函数,其反函数为,对偶式为。

4.施密特触发器有个稳定状态.,多谐振荡器有个稳定状态。

5.A/D转换器的主要参数有,。

6.四位环型计数器和扭环形计数器,初始状态都是1000,经过5个时钟脉冲后,状态分别为和。

7.一个JK触发器有 个稳态,它可存储 位二进制数。

8.时序逻辑电路的输出不仅和_______有关,而且还与_____________有关。

9.TTL或非门多余输入端应.三态门的输出除了有高、低电平外,还有一种输出状态叫态

10.基本的RS触发器的特征方程为,约束条件为。

三、作图题

1.D触发器各输入端的波形如图所示,试画出Q端对应的电压波形。

2.用集成芯片555构成的施密特触发器电路及输入波形Vi如图6.3(a、b)所示,试画出对应的输出波形Vo

四、分析题

1.利用公式法将函数Y化简成最简与或式:

2.利用图形法将函数F化简成最简与或式:

Y(A,B,C,D)=∑m(0,1,4,9,2)+∑d(2,3,6,10,11,14)

3.试分析图示电路,写出其驱动方程、输出方程、状态方程,画出状态转换图、说明其逻辑功能。

五、设计题

1.设计一个三变量判偶电路,当输入变量A,B,C中有偶数个1时,其输出为1;否则输出为0。

并用3/8线译码器(74LS138)和适当门电路实现。

2.用两个十六进制74161计数器设计一个完整的19进制计数器。

CP

EPET

工作状态

×

0

×

××

异步置零

1

0

××

置数

×

1

1

01

保持

×

1

1

×0

保持(C=0)

1

1

11

计数

3.用JK触发器设计一个按自然态序进行计数的七进制同步加法计数器。

第四套

一、选择题

1.十进制数25用8421BCD码表示为()

A.10101B.00100101C.100101D.10101

2.当TTL与非门的输入端悬空时相当于输入为()

A.逻辑0B.逻辑1C.不确定D.0.5V

3.逻辑函数F=AB+B的对偶式F′=()

A.+CB.(A+B)(B+