8访问外部存储器.docx

《8访问外部存储器.docx》由会员分享,可在线阅读,更多相关《8访问外部存储器.docx(31页珍藏版)》请在冰豆网上搜索。

8访问外部存储器

8访问外部存储器

和5.2章描述的一样,访问外部数据存储器需要将EXTRAM位置1。

访问外部数据存储器既可用16位地址(使用“MOVX@DPTR),也可以使用8位地址(使用“MOVX@Ri”),如下所述。

通过8位地址访问

8位地址线经常使用1个或多个I/O线结合来访问RAM页面。

如果使用8位地址,在外部存储器读写周期,专用寄存器P2口的内容始终保持在P2引脚。

使得访问页面非常容易。

图5-5示一个访问2K的外部RAM的硬件配置。

P0用作一个地址/数据分时复用总线到RAM,P2口的三线用来访问RAM页。

CPU产生/RD和/WR(P3.7和P3.6可选择功能)来选通存储器。

当然,用户可以使用其它I/O线来代替P2到RAM页面。

通过16位地址访问

16位地址线经常用来访问64K的外部数据存储器。

图5-6示硬件配置来访问外部64K的RAM。

只要使用16位地址,除了P0口、/RD和/WR之外,P2口的高位地址在读写周期一直保持。

在任何情况下,P0口的低位地址线和数据线为分时复用。

ALE(地址锁存使能)用来将地址字节捕获到外部锁存器。

在ALE的负跳变时地址字节有效。

接着,在写周期,在/WR激活之前,要写的数据出现在P0口,并一直保持直到/WR信号释放。

在一个读周期,信号字节从P0口接收在读选通信号释放前。

在访问外部存储器时,CPU写0FFH到端口0锁存(专用寄存器),专用寄存器P0保持的信息被擦除。

8.1配置ALE引脚

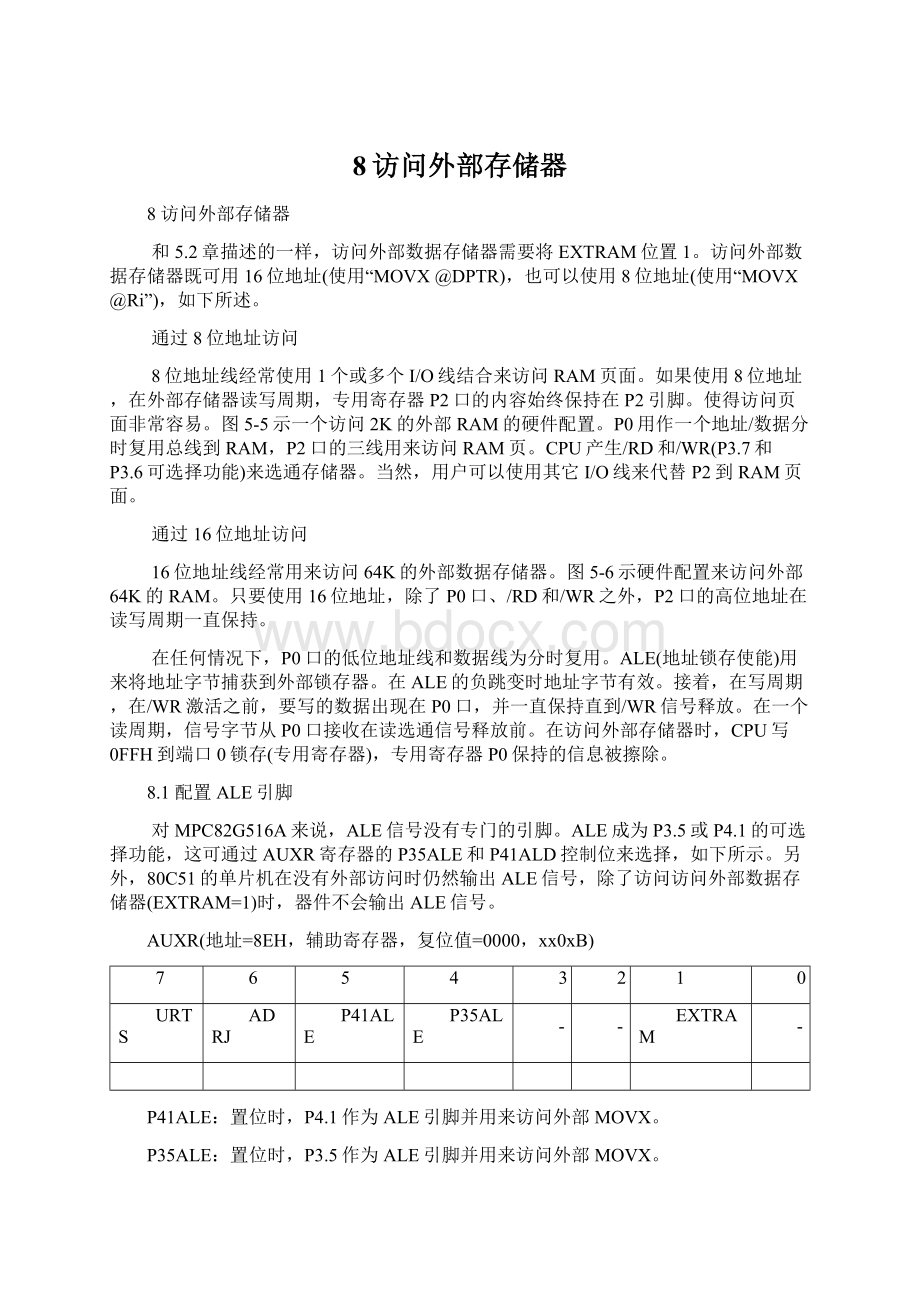

对MPC82G516A来说,ALE信号没有专门的引脚。

ALE成为P3.5或P4.1的可选择功能,这可通过AUXR寄存器的P35ALE和P41ALD控制位来选择,如下所示。

另外,80C51的单片机在没有外部访问时仍然输出ALE信号,除了访问访问外部数据存储器(EXTRAM=1)时,器件不会输出ALE信号。

AUXR(地址=8EH,辅助寄存器,复位值=0000,xx0xB)

7

6

5

4

3

2

1

0

URTS

ADRJ

P41ALE

P35ALE

-

-

EXTRAM

-

P41ALE:

置位时,P4.1作为ALE引脚并用来访问外部MOVX。

P35ALE:

置位时,P3.5作为ALE引脚并用来访问外部MOVX。

EXTRAM:

0:

当地址小于0x400时,禁止访问外部数据存储器;

当访问地址为0x0000~0x03FF时自动切换到片上XRAM。

1:

允许访问全部外部数据存储器,地址范围为0x0000~0xFFFF;

禁止访问片内XRAM。

8.2延长时序来访问低速存储器

为了访问低速的外部数据存储器,设计了时序延长机制来控制“MOVX”指令的访问时序。

延长(STRETCH)寄存器的位ALES1和ALES0,控制延长设置时间和保持时间并保持到ALE的下降沿。

另外,位RWS2、RWS1和RWS0控制延长读写脉冲宽度。

用户可以通过适当的配置STRETCH寄存器,以适应外部数据存储器读写的需求。

STRETCH(地址=8FH,延长寄存器,复位值=0000,0011B)

7

6

5

4

3

2

1

0

-

-

ALES1

ALES0

-

RWS2

RWS1

RWS0

{ALES1,ALES0}:

00:

没有延长,P0口地址的设置/保持时间随着ALE的下降沿在一个时钟周期;

01:

1个时钟周期的延长,P0口地址设置/保持时间随着ALE的下降沿在二个时钟周期;

10:

2个时钟周期的延长,P0口地址设置/保持时间随着ALE的下降沿在三个时钟周期;

11:

3个时钟周期的延长,P0口地址设置/保持时间随着ALE的下降沿在四个时钟周期;

{RWS2,RWS1,RWS0}:

000:

没有延长,MOVX读写脉冲为一个时钟周期;

001:

1个时钟延长,MOVX读写脉冲为2个时钟周期;

010:

2个时钟延长,MOVX读写脉冲为3个时钟周期;

011:

3个时钟延长,MOVX读写脉冲为4个时钟周期;

100:

4个时钟延长,MOVX读写脉冲为5个时钟周期;

101:

5个时钟延长,MOVX读写脉冲为6个时钟周期;

110:

6个时钟延长,MOVX读写脉冲为7个时钟周期;

111:

7个时钟延长,MOVX读写脉冲为8个时钟周期;

看如下时序波形的演示。

Figure8-1.“MOVX@DPTR,A”没有延迟

图8-2“MOVX@DPTR,A”有延迟

图8-3“MOVXA,@DPTR”没有延迟

图8-4“MOVXA,@DPTR”有延迟

9双数据指针寄存器(DPTR)

传统的数据指针用来加速代码执行和减少代码尺寸。

双DPTR结构是一种方法,芯片将指定外部数据存储器的定位地址。

外部存储器有两个16位DPTR寄存器,和一个控制位称作为DPS(AUXR1.0),允许在程序代码和外部存储器之间的切换。

图9-1使用双DPTR

DPTR指令

使用DPS位的六条指令参考DPTR的当前选择,如下:

INCDPTR;数据指针加1

MOVDPTR,#data16;DPTR加载16位常量

MOVCA,@A+DPTR;将代码字节移动到ACC

MOVXA,@DPTR;移动外部RAM(16位地址)到ACC

MOVX@DPTR,A;移动ACC到外部RAM(16位地址)

JMP@A+DPTR;直接跳转到DPTR

AUXR1(地址=8EH,辅助寄存器1,复位值=0000,0000B)

7

6

5

4

3

2

1

0

P4KB

P4PCA

P4SPI

P4S2

GF2

-

-

DPS

DPS:

DPTR选择位,用来在DPTR0和DPTR1之间切换

在DPTR0和DPTR1之间切换时,可通过软件来保存DPS位状态

DPSDPTR选择

1DPTR0

2DPTR1

10I/O端口结构和操作

MPC82G516A有五个I/O端口:

端口0、端口1、端口2、端口3和端口4。

所有的端口都为8位端口。

准确的可用I/O引脚数量由封装类型决定。

见表10-1。

表10-1可用I/O引脚数量

封装类型

I/O引脚脚

引脚数量

40-pinDIP

P0,P1,P2,P3

32

28-pinSSOP

P0.1~P0.4,P0.6,P1.0,P1.2,P1.3,P1.5,

P2.0,P2.1,P2.3,P2.4,P2.5

P3.0~P3.3,P3.5

P4.2

20

44-pinPLCC

P0,P1,P2,P3,P4.0~P4.3

36

44-pinPQFP

P0,P1,P2,P3,P4.0~P4.3

36

48-pinLQFP

P0,P1,P2,P3,P4

40

10.1端口配置

MPC82G516A的所有端口可通过软件个别的、独立的配置为四种之中的一种类型,基于位位基础,如表10-2所示。

这四种类型有:

准双向(标准8051的I/O端口)、上拉输出、集电极开路输出和输入(高阻抗输入)。

每个端口有两个模式寄存器来选择每个端口引脚的输出类型。

表10-2端口配置设定

PxM0.y

PxM1.y

端口

0

0

准双向端口

0

1

上拉输出

1

0

输入(高阻抗)

1

1

集电极开路输出

这里x=0~4(端口号),y=0~7(端口引脚号)。

寄存器PxM0和PxM1列表如下。

P0M0(地址=93H,端口0模式寄存器0,复位值=0000,0000B)

7

6

5

4

3

2

1

0

P0M0.7

P0M0.6

P0M0.5

P0M0.4

P0M0.3

P0M0.2

P0M0.1

P0M0.0

P0M1(地址=94H,端口0模式寄存器1,复位值=0000,0000B)

7

6

5

4

3

2

1

0

P0M1.7

P0M1.6

P0M1.5

P0M1.4

P0M1.3

P0M1.2

P0M1.1

P0M1.0

P1M0(地址=91H,端口1模式寄存器0,复位值=0000,0000B)

7

6

5

4

3

2

1

0

P1M0.7

P1M0.6

P1M0.5

P1M0.4

P1M0.3

P1M0.2

P1M0.1

P1M0.0

P1M1(地址=92H,端口1模式寄存器1,复位值=0000,0000B)

7

6

5

4

3

2

1

0

P1M1.7

P1M1.6

P1M1.5

P1M1.4

P1M1.3

P1M1.2

P1M1.1

P1M1.0

P2M0(地址=95H,端口2模式寄存器0,复位值=0000,0000B)

7

6

5

4

3

2

1

0

P2M0.7

P2M0.6

P2M0.5

P2M0.4

P2M0.3

P2M0.2

P2M0.1

P2M0.0

P2M1(地址=96H,端口2模式寄存器1,复位值=0000,0000B)

7

6

5

4

3

2

1

0

P2M1.7

P2M1.6

P2M1.5

P2M1.4

P2M1.3

P2M1.2

P2M1.1

P2M1.0

P3M0(地址=B1H,端口3模式寄存器0,复位值=0000,0000B)

7

6

5

4

3

2

1

0

P3M0.7

P3M0.6

P3M0.5

P3M0.4

P3M0.3

P3M0.2

P3M0.1

P3M0.0

P3M1(地址=B2H,端口3模式寄存器1,复位值=0000,0000B)

7

6

5

4

3

2

1

0

P3M1.7

P3M1.6

P3M1.5

P3M1.4

P3M1.3

P3M1.2

P3M1.1

P3M1.0

P4M0(地址=B3H,端口4模式寄存器0,复位值=0000,0000B)

7

6

5

4

3

2

1

0

P4M0.7

P4M0.6

P4M0.5

P4M0.4

P4M0.3

P4M0.2

P4M0.1

P4M0.0

P4M1(地址=B4H,端口4模式寄存器1,复位值=0000,0000B)

7

6

5

4

3

2

1

0

P4M1.7

P4M1.6

P4M1.5

P4M1.4

P4M1.3

P4M1.2

P4M1.1

P4M1.0

10.1.1准双向I/O

端口引脚工作在准双向模式时与标准8051端口引脚类似。

一个准双向端口用作输入和输出时不需要对端口重新配置。

这种可能是因为端口输出逻辑高时,弱上拉,允许外部器件拉低引脚。

当输出低时,强的驱动能力可吸收大电流。

在准双向输出时有三个上拉晶体管用于不同的目的。

其中的一种上拉,称为微上拉,只要端口寄存器的引脚包含逻辑1则打开。

如果引脚悬空,则这种非常弱上拉提供一个非常小的电流将引脚拉高。

第二种上拉称为“弱上拉”,端口寄存器的引脚包含逻辑1时且引脚自身也在逻辑电平时打开。

这种上拉对准双向引脚提供主要的电流源输出为1。

如果引脚被外部器件拉低,这个弱上拉关闭,只剩一个微上拉。

为了在这种条件下将引脚拉低,外部器件不得不吸收超过弱上拉功率的电流,且拉低引脚在输入的极限电压之下。

第三种上拉称为“强”上拉。

这种上拉用于加速准双向端口的上升沿跳变,当端口寄存器从逻辑0到逻辑1时。

当这发生时,强上拉打开两个CPU时钟,快速将端口引脚拉高。

准双向端口配置如图10-1所示。

准双向端口有施密特触发器来抑制输入噪音。

图10-1准双向I/O

10.1.2集电极开路输出

配置为集电极开路输出时,当端口寄存器包含逻辑0时,关闭所有上拉,只有端口引脚的下拉晶体管。

使用这个功能配置应用,端口引脚必须有外部上拉,典型的将电阻接到VDD。

这个模式的下拉和准双向端口的模式相同。

另外,在这种配置下的端口输入引脚的输入路径和准双向模式相同。

集电极开路端口配置如图10-2所示。

开路集电极输入也有一个施密特触发器用来抑制噪音。

图10-2集电极开路输出

10.1.3输入(高阻抗)

输入配置一个施密特触发器但是在引脚上没有任何上拉电阻,如下图10-3所示。

图10-3输入

10.1.4推挽输出

推挽输出配置有下拉,和集电极开路、准双向输出模式有着相同的结构,当端口寄存器包含逻辑1时提供一个连续的强上拉。

当一个端口输出需要更大的电流时可配置为推挽输出模式。

另外,在这种配置下的端口输入引脚和输入路径的准双向模式的配置相同。

上拉端口配置如图10-4所示。

上拉端口引脚也包含一个输入施密特触发器用来降低噪音。

图10-4上拉输出

10.2I/O引脚用作ADC功能

端口1用作于可选择功能的模拟输入。

为了获得最好的模拟性能,引脚用作ADC时应将数字输出禁止。

这可能通过将引脚配置为输入模式来实现。

10.3I/O端口的其它备注

MPC82G516A的每个输出都设计有吸收典型LED的驱动电流能力,然而,所有端口的总输出最大电流不能超过极限值。

请参考29章:

绝对最大值

11定时器/计数器

MPC82G516A有三个16位定时器/计数器:

定时器0、定时器1和定时器2。

每一个包含两个8位寄存器,THx和TLx(这里,x=0、1或2)。

所有这些操作既可配置为定时器或事件记数器。

定时器功能,TLx寄存器每12个时钟周期或1个周期加1,通过软件来选择。

因此可认为为计数器时钟周期。

每记12个时钟周期,计数速率达1/12的晶振频率。

计数器功能,下降沿时寄存器加1,根据外部输入引脚T0、T1或T2。

在这些功能中,每个时钟周期对外部输入信号(T0引脚和T1引脚)进行采样,每12个时钟周期对T2引脚采样。

当采样信号出现一个高电平接着一个低电平,计数加1。

当检测到跳变时新计数值出现在寄存器中。

对定时器0和定时器1来说,需要用两个时钟周期来识别下降沿跳变,最大的计数速率为1/2的晶振频率;对于定时器2,需要用24个时钟周期来识别下降沿跳变,最大计数速率为1/24的晶振频率。

外部输入信号没有严格的周期限制,但是要确保在电平改变前至少有一次采样,对定时器0和定时器1来说信号应该至少保持一个时钟,定时器2需要12个时钟周期。

对定时器0和定时器2来说,除了标准8051定时器的功能之外,添加了一些新的特征。

下面的子章节将详细描述这些定时器/计数器。

11.1定时器0和定时器1

定时器或计数器功能通过专用寄存器TMOD的控制位C/T来选择,如下所示。

这两个定时器/计数器有四种工作模式,通过TMOD的位对(M1,M0)来选择。

这两个定时器/计数器的模式0、1和模式2是相同的,模式3是不同的。

除了TMOD之外,其它专用寄存器TCON和AUXR2包含几个控制位和状态位与这两个定时也相关,也如下所示。

TMOD(地址=89H,定时器/计数器模式控制位,复位值=0000,0000B)

定时器1

定时器2

7

6

5

4

3

2

1

0

GATE

C/-T

M1

M0

GATE

C/-T

M1

M0

GATE:

当门控位置位时,只有在/INT0或/INT1引脚是高电平且TR0或TR1控制位置位时,定时器/计数器0或1使能。

当门控制位清零时,只要TR0或TR1置1定时器0或1使能。

C/T:

定时器或计数器选择器。

清零为定时器功能(从内部系统时钟输入)。

置位为计数器功能(从T0或T1引脚输入)。

M0M1

工作模式

0

0

8位定时器/计数器。

THx与TLx作为5位预分频器

0

1

16位定时器/计数器。

THx与TLx串联;没有分步频器

1

0

8位自动重载定时器/计数器。

THx保持一个值,并在每次溢出时加载到TLx

1

1

(定时器0)TL0是一个8位定时器/计数器并通过标准定时器0的控制位控制。

TH0仅仅是一个8位定时器通过定时器1的控制位控制

1

1

(定时器1)定时器/计数器停止

TCON(地址=88H,定时器/计数器控制位,复位值=0000,0000B)

7

6

5

4

3

2

1

0

TF1

TR1

TF0

TR0

IE1

IT1

IE0

IT0

TF1:

定时器1溢出标志位。

定时器/计数器溢出时由硬件置位。

处理器进入中断向量程序由硬件清零。

TR1:

定时器1运行控制位。

通过软件置位/清零开启或关闭定时器/计数器1。

TF0:

定时器0溢出标志位。

定时器/计数器溢出时由硬件置位。

处理器进入中断向量程序由硬件清零。

TR0:

定时器0运行控制位。

通过软件置位/清零开启或关闭定时器/计数器0。

AUXR2(地址=A6H,辅助寄存器2,复位值=0000,0000B)

7

6

5

4

3

2

1

0

T0X12

T1X12

URM0X6

S2TR

S2SMOD

S2TX12

S2CKOE

T0CKOE

T0X12:

当C/T=0时,定时器0的时钟源选择。

置位选择Fosc作为系统时钟源,清零选择Fosc/12作为时钟源。

T1X12:

当C/T=0时,定时器1的时钟源选择。

置位选择Fosc作为系统时钟源,清零选择Fosc/12作为时钟源。

T0CKOE:

置位/清零来使能/禁止从P3.4输出定时器0时钟。

四种工作模式在以下的文本中描述。

11.1.1模式0:

13位定时器/计数器

定时器0和定时器1的模式0看起来像一个32预分频的8位计数器。

且这两个定时器运行模式0是相同的。

图11-1展示模式0的运行。

在这个模式,定时器寄存器配置为一个13位寄存器。

计数器所有位从全1翻转到全0,置位定时器中断标志位TFx。

当TRx=1且GATE=0或/INTx=1,定时器使能输入计数。

(置GATE=1时通过外部输入/INTx控制定时器,以便脉冲宽度测量)。

TRx和TFx控制位在专用寄存器TCON。

GATE位在TMOD。

有两个不同的GATE位,一个是定时器0(TMOD.7)另一个是定时器0(TMOD.3)。

13位寄存器包含THx的所有8位和TLx的低5位。

TLx的高3位是不确定的可以忽略。

置位运行标志(TRx)不会清除寄存器。

意思是说用户在开始计数前应对THx和TLx进行初始化。

图11-1.定时器1工作在模式0:

13位定时器/计数器

11.1.2模式1:

16位定时器/计数器

除了定时器的寄存器使用全部16位外,模式1和模式0是相同的。

参考图11-2。

在这个模式,THx和TLx串联,没有预分频。

图11-2.定时器1的模式1:

16位定时器/计数器

11.1.3模式2:

8位自动加载

模式2配置定时器寄存器为一个自动加载的8位计数器(TLx),如图11-3所示。

TLx溢出不仅置位TFx,而且也将THx的内容加载到TLx,THx内容由软件预置,加载不会改变THx的值。

图11-3.定时器1的模式2:

8位自动加载

11.1.4模式3:

两个8位定时器/计数器

定时器1在模式3保持计数值。

效果和设置TR1=0一样。

定时器0在模式3建立TL0和TH0两个独立的计数器。

定时器0的模式3的逻辑图如图11-4所示。

TL0使用定时器0控制位:

C/T、GATE、TR0、/INT0和TF0。

TH0锁定为定时器功能(每个机器周期计数)且接替定时器1来使用TR1和TF1,因从TH0控制定时器1中断。

模式3提供当有额外的需求应用时的一个8位时器或计数器时。

当定时器0在模式3时,定时器1可打开或关闭并切换到脱离,进入到自己的模式3,或仍然可用作为串行口的波特率发生器,或者不需要中断的其它应用。

图11-4定时器0工作在模式3:

两个8位定时器/计数器

11.1.5可编程时钟输出从定时器0

使用定时器0,可编程从引脚T0CK0(P3.4)输出占空比为50%的时钟周期。

输出频率根据系统时钟频率(Fosc)和加载值到TH0寄存器,公式如下所示。

定时器0时钟输出模式编程如下:

●在AUXR2寄存器置位T0CKOE。

●清除定时器0的C/T位在TMOD寄存器。

●清除定时器0的GATE位在TMOD寄存器。

●从公式计算出8位自动加载值并输入到TH0寄存器。

●在TL0寄存器输入一个8位初始值。

可以和自动加载值相同。

●通过设置TCON寄存器的TR0位启动定时器。

图11-5.编程从定时器0的时钟输出

11.2定时器2

定时器2是一个16位定时器/计数器,既可作为一个定时器也可以作为一个事件计数器,通过专用寄存器T2CON的C/T2位来选择。

定时器2有四种工作模式:

捕获、自动加载(向上或向下计数)、波特率发生器和可编程时钟输出,通过专用寄存器T2CON和T2MOD来选择,如下所示。

T2CON(地址=C8H,定时器/计数器2控制寄存器,复位值=0000,0000B)

7

6

5

4

3

2

1

0

TF2

EXF2

RCLK

TCLK

EXEN2

TR2

C/-T2

CP/-RL2

TF2:

定时器2溢出标志位,定时器2溢出置位且必须通过软件清零。

当RCLK=1或TCLK=1时,TF2不会被置位。

EXF2:

定时器2外部标志位,在EXEN2=1时,且在T2EX上有负跳变时加载或捕获将引起置位。

当时器2中断使能时,EXF2=1时将引起CPU进入定时器2中断向量程序。

EXF2必须通过软件清零。

EXF2在向上/向下计数器模式不会产生中断。

RCLK:

接收时钟控制位。

置位时,串行口使用定时器2溢出脉冲来接收,在模式1和模式3时。

RCLK=0使用定时器1溢出脉冲来产生接收时钟。

TCLK:

传送时钟控制位。

置位时,串行口使用定时器2溢出脉冲来发送,在模式1和模式3时。

TCLK=0使用定时器1溢出脉冲来产生发送时钟。

EXEN2:

定时器2外部使能位。

置位时,如果定时器2没有用作串行口时钟,在T2EX的负跳变时捕获或加载并作为结果。

TR2:

定时器2的启始和停止位。

逻辑1时启动定时器。

C/T2:

定时器或计数器选择。

清零时,选择内部定时器。

置位时,选择外部事件计数器(下降沿触发)。

CP/RL2:

捕获/加载控制位。

置位时,如果EXEN2=1,在T2EX的负跳变时将产生捕获。

清零时,如果EXEN2=1,定时器2溢出或T2EX上有负跳变时将产生自动加载。

当RCLK=1或TCLK=1时,这一位被忽略并强制加载在定时器2溢出时。

T2MOD(地址=C9H,定时器/计数器2控制寄存器,复位值=xxxx,xx00B)

7

6

5

4

3

2

1

0

-

-

-

-

-

-

T2OE

DCEN

T2OE:

定时器2时钟输出使能位,置位使能清零禁止。

DCEN:

定时器