EDA大三课程设计.docx

《EDA大三课程设计.docx》由会员分享,可在线阅读,更多相关《EDA大三课程设计.docx(27页珍藏版)》请在冰豆网上搜索。

EDA大三课程设计

一,课件

今需设计一个十六路彩灯控制器,6种花型循环变化,有清零开关,并且可以选择快慢两种节拍。

根据系统设计要求可知,整个系统共有三个输入信号:

控制彩灯节奏快慢的基准时钟信号CLK_IN,系统清零信号CLR,彩灯节奏快慢选择开关CHOSE_KEY;共有16个输出信号LED[15..0],分别用于控制十六路彩灯。

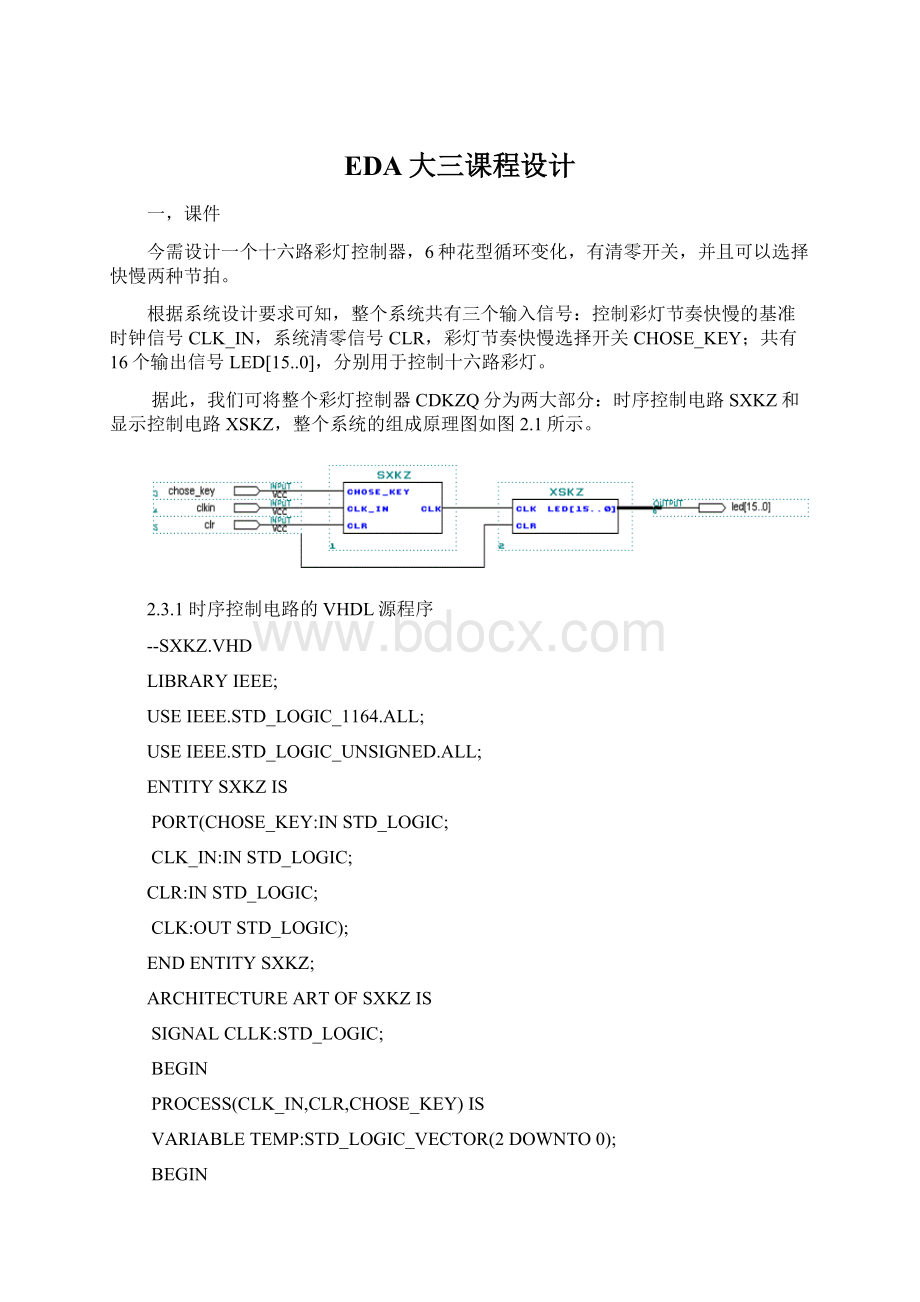

据此,我们可将整个彩灯控制器CDKZQ分为两大部分:

时序控制电路SXKZ和显示控制电路XSKZ,整个系统的组成原理图如图2.1所示。

2.3.1时序控制电路的VHDL源程序

--SXKZ.VHD

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYSXKZIS

PORT(CHOSE_KEY:

INSTD_LOGIC;

CLK_IN:

INSTD_LOGIC;

CLR:

INSTD_LOGIC;

CLK:

OUTSTD_LOGIC);

ENDENTITYSXKZ;

ARCHITECTUREARTOFSXKZIS

SIGNALCLLK:

STD_LOGIC;

BEGIN

PROCESS(CLK_IN,CLR,CHOSE_KEY)IS

VARIABLETEMP:

STD_LOGIC_VECTOR(2DOWNTO0);

BEGIN

IFCLR='1'THEN--当CLR='1'时清零,否则正常工作

CLLK<='0';TEMP:

="000";

ELSIFRISING_EDGE(CLK_IN)THEN

IFCHOSE_KEY='1'THEN

IFTEMP="011"THEN

TEMP:

="000";

CLLK<=NOTCLLK;

ELSE

TEMP:

=TEMP+'1';

ENDIF;

--当CHOSE_KEY='1'时产生基准时钟频率的1/4的时钟信号,否则产生基准时钟

--频率的1/8的时钟信号

ELSE

IFTEMP="111"THEN

TEMP:

="000";

CLLK<=NOTCLLK;

ELSE

TEMP:

=TEMP+'1';

ENDIF;

ENDIF;

ENDIF;

ENDPROCESS;

CLK<=CLLK;

ENDARCHITECTUREART;

2.3.2显示控制电路的VHDL源程序

--XSKZ.VHD

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYXSKZIS

PORT(CLK:

INSTD_LOGIC;

CLR:

INSTD_LOGIC;

LED:

OUTSTD_LOGIC_VECTOR(15DOWNTO0));

ENDENTITYXSKZ;

ARCHITECTUREARTOFXSKZIS

TYPESTATEIS(S0,S1,S2,S2,S4,S5,S6);

SIGNALCURRENT_STATE:

STATE;

SIGNALFLOWER:

STD_LOGIC_VECTOR(15DOWNTO0);

BEGIN

PROCESS(CLR,CLK)IS

CONSTANTF1:

STD_LOGIC_VECTOR(15DOWNTO0):

="0001000100010001";

CONSTANTF2:

STD_LOGIC_VECTOR(15DOWNTO0):

="1010101010101010";

CONSTANTF2:

STD_LOGIC_VECTOR(15DOWNTO0):

="0011001100110011";

CONSTANTF4:

STD_LOGIC_VECTOR(15DOWNTO0):

="0100100100100100";

CONSTANTF5:

STD_LOGIC_VECTOR(15DOWNTO0):

="1001010010100101";

CONSTANTF6:

STD_LOGIC_VECTOR(15DOWNTO0):

="1101101101100110";

--六种花型的定义

BEGIN

IFCLR='1'THEN

CURRENT_STATE<=S0;

ELSIFRISING_EDGE(CLK)THEN

CASECURRENT_STATEIS

WHENS0=>

FLOWER<="ZZZZZZZZZZZZZZZZ";

CURRENT_STATE<=S1;

WHENS1=>

FLOWER<=F1;

CURRENT_STATE<=S2;

WHENS2=>

FLOWER<=F2;

CURRENT_STATE<=S2;

WHENS2=>

FLOWER<=F2;

CURRENT_STATE<=S4;

WHENS4=>

FLOWER<=F4;

CURRENT_STATE<=S5;

WHENS5=>

FLOWER<=F5;

2.3.3整个电路系统的VHDL源程序

--CDKZQ.VHD

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYCDKZQIS

PORT(CLK_IN:

INSTD_LOGIC;

CLR:

INSTD_LOGIC;

CHOSE_KEY:

INSTD_LOGIC;

LED:

OUTSTD_LOGIC_VECTOR(15DOWNTO0));

ENDENTITYCDKZQ;

ARCHITECTUREARTOFCDKZQIS

COMPONENTSXKZIS

PORT(CHOSE_KEY:

INSTD_LOGIC;

CLK_IN:

INSTD_LOGIC;

CLR:

INSTD_LOGIC;

CLK:

OUTSTD_LOGIC);

ENDCOMPONENTSXKZ;

COMPONENTXSKZIS

PORT(CLK:

INSTD_LOGIC;

CLR:

INSTD_LOGIC;

LED:

OUTSTD_LOGIC_VECTOR(15DOWNTO0));

ENDCOMPONENTXSKZ;

SIGNALS1:

STD_LOGIC;

BEGIN

U1:

SXKZPORTMAP(CHOSE_KEY,CLK_IN,CLR,S1);

U2:

XSKZPORTMAP(S1,CLR,LED);

ENDARCHITECTUREART;

2.4.1系统的有关仿真

时序控制电路SXKZ、显示控制电路XSKZ及整个电路系统CDKZQ的仿真图分别如图2.2、图2.3和图2.4所示。

2.4.2系统的硬件验证

系统通过仿真后,我们可根据自己所拥有的EDA实验开发系统进行编程下载和硬件验证。

考虑到一般EDA实验开发系统提供的输出显示资源有限,我们可将输出适当调整后进行硬件验证。

(1)在时序控制电路SXKZ的设计中,利用计数器计数达到分频值时,对计数器进行清零,同时将输出信号反向,这就非常简洁地实现了对输入基准时钟信号的分频,并且分频信号的占空比为0.5。

(2)在显示控制电路XSKZ的设计中,利用状态机非常简洁地实现了六种花型的循环变化,同时利用六个十六位常数的设计,可非常方便地设置和修改六种花型。

(3)对于顶层程序的设计,因本系统模块较少,既可使用文本的程序设计方式,也可使用原理图的设计方式。

但对于模块较多的系统,最好使用文本的程序设计方式。

二,多路彩灯控制设计

1)系统设计要求

设计一个多路彩灯控制器,十六种彩灯能循环变化,有清零开关,可以变化彩灯闪动频率即是可以选择快慢两种节拍。

2).设计方案

整个系统有三个输入信号,分别为控制快慢的信号OPT,复位清零信号CLR,输出信号是16路彩灯输出状态。

系统框图如:

主要模块组成:

时序控制电路模块和显示电路模块,时序控制电路是根据输入信号的设置得到相应的输出信号,并将此信号作为显示电路的时钟信号;显示电路输入时钟信号的周期,有规律的输出设定的六种彩灯变化类型。

3).模块设计

时序控制模块:

CLK为输入时钟信号,电路在时钟上升沿变化;CLR为复位清零信号,高电平有效,一旦有效时,电路无条件的回到初始状态;OPT为频率快慢选择信号,低电平节奏快,高电平节奏慢;CLKOUT为输出信号,CLR有效时输出为零,否则,随OPT信号的变化而改变。

我们假设时序控制电路所产生的控制时钟信号的快慢两种节奏分别为输入时钟信号频率的1/4和1/8,因而输出时钟控制信号可以通过对输入时钟的计数来获得。

当opt为低电平时,输出没经过两个时钟周期进行翻转,实现四分频的快节奏;当opt为高电平时,输出每经过四个时钟周期进行翻转,实现把八分频的慢节奏。

显示控制电路的模块框图如图所示,输入信号clk和clr的定义与时序控制电路一样,输入信号led[15...0]能够循环输出16路彩灯16种不同状态的花型。

对状态的所对应的彩灯输出花型定义如下:

S0:

0000000000000000S1:

0001000100010001

S2:

0010001000100010S3:

0011001100110011

:

010*********

S6:

0110011001100110S7:

0111011101110111

S8:

1000100010001000S9:

1001100110011001

S10:

1010101010101010S11:

1011101110111011

S12:

1100110011001100S13:

110111*********1

S14:

111011*********0S15:

111111*********1

多路彩灯在多种花型之间的转换可以通过状态机实现,当复位信号clr有效时,彩灯恢复初始状态s0,否则,每个时钟周期,状态都将向下一个状态发生改变,并对应输出的花型,这里的时钟周期即时时序控制电路模块产生的输出信号,它根据opt信号的不同取值得到两种快慢不同的时钟频率。

clr

4).序控制电路模块程序如下:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitymetronomeis--定义实体

port(

clk:

instd_logic;--时钟信号

clr:

instd_logic;--复位信号

opt:

instd_logic;--快慢控制信号

clkout:

outstd_logic--输出时钟信号

);

endmetronome;

architecturertlofmetronomeis

signalclk_tmp:

std_logic;

signalcounter:

std_logic_vector(1downto0);--定义计数器

begin

process(clk,clr,opt)

begin

ifclr='1'then--清零

clk_tmp<='0';

counter<="00";

elsifclk'eventandclk='1'then

ifopt='0'then--四分频,快节奏

ifcounter="01"then

counter<="00";

clk_tmp<=notclk_tmp;

else

counter<=counter+'1';

endif;

else--八分频,慢节奏

ifcounter="11"then

counter<="00";

clk_tmp<=notclk_tmp;

else

counter<=counter+'1';

endif;

endif;

endif;

endprocess;

clkout<=clk_tmp;--输出分频后的信号

endrtl;endrtl;

显示模块电路程序如下:

libraryieee;

useieee.std_logic_1164.all;

entityoutputis

port(

clk:

instd_logic;--输入时钟信号

clr:

instd_logic;--复位信号

led:

outstd_logic_vector(15downto0));--彩灯输出

endoutput;

architecturertlofoutputis

typestatesis--状态机状态列举

(s0,s1,s2,s3,s4,s5,s6,s7,s8,s9,s10,s11,s12,s13,s14,s15);

signalstate:

states;

begin

process(clk,clr)

begin

ifclr='1'then

state<=s0;

led<="0000000000000000";

elsifclk'eventandclk='1'then

casestateis

whens0=>

state<=s1;

whens1=>

state<=s2;

led<="0001000100010001";

whens2=>

state<=s3;

led<="0010001000100010";

whens3=>

state<=s4;

led<="0011001100110011";

whens4=>

state<=s5;

led<="0100010001000100";

whens5=>

state<=s6;

led<="0101010101010101";

whens6=>

state<=s7;

led<="0110011001100110";

whens7=>

state<=s8;

led<="0111011101110111";

whens8=>

state<=s9;

led<="1000100010001000";

whens9=>

state<=s10;

led<="1001100110011001";

whens10=>

state<=s11;

led<="1010101010101010";

whens11=>

state<=s12;

led<="1011101110111011";

whens12=>

state<=s13;

led<="1100110011001100";

whens13=>

state<=s14;

led<="1101110111011101";

whens14=>

state<=s15;

led<="1110111011101110";

whens15=>

state<=s1;

led<="1111111111111111";

endcase;

endif;

endprocess;

endrtl;

顶出模块设计程序:

libraryieee;

useieee.std_logic_1164.all;

entitycotopis

port(

clk:

instd_logic;

clr:

instd_logic;

opt:

instd_logic;

led:

outstd_logic_vector(15downto0));--八路彩灯输出

endcolorled;

architecturertlofcolorledis

componentmetonomeis--定义元件:

时序控制电路

port(

clk:

instd_logic;

clr:

instd_logic;

opt:

instd_logic;

clkout:

outstd_logic);

endcomponentmetonome;

componentoutputis--定义元件:

显示电路

port(

clk:

instd_logic;

clr:

instd_logic;

led:

outstd_logic_vector(7downto0));

endcomponentoutput;

signalclk_tmp:

std_logic;

begin

u1:

metonomeportmap(clk,clr,opt,clk_tmp);--例化时序控制模块

u2:

outputportmap(clk_tmp,clr,led);--例化显示电路模块

endrtl;

时序控制模块仿真波形:

从图中可以看出,当复位信号为高电平时,电路时钟输出清零,当快慢信号OPT为低电平时,时序控制电路四分频起作用,当快慢信号OPT为高电平时,时序控制电路八分频起作用,仿真结果符合电路要求。

显示模块仿真波形:

当复位信号有效时彩灯输出为零,否则,显示电路在十六种不同状态间转换。

多路彩灯控制仿真波形:

从图中可以看出当OPT为高电平时彩灯状态转换慢,为低电平时转换要快,当复位信号有效时,所用输出都清零。

综上所述,本次设计实现了设计要求中的要求。

北京理工大学珠海学院

课程设计

课程设计内容简介:

(任务概述,技术参数)

本统系由一个时序控制模块SX和一个显示控制模块XS组成;

基本功能:

(1)通过CLK键,输入时钟脉冲,用9盏灯实现四种花型的循环交替变化,有四方形,十字形,z形和U字形;

(2)每两种花形变化的间隔为2秒;

(3)有复位的功能,通过CLR键来控制复位;

(4)有暂停功能,通过K1键来控制暂停和继续;

扩展功能:

(1)可调节花形循环的速度,SPEED键为控制速度键;

(2)用户可以选择对应的彩灯形状,当K1为暂停状态时,用K2和K3键的四个组合来控制所要显示的花形;

(3)彩灯可以按指定的图形去闪烁发亮。

1.3程序设计任务

设计课题:

彩灯控制器的设计

二:

设计流程

彩灯控制器由一个时序控制模块SX和一个显示控制模块XS组成;

时序控制模块上:

输入有端口SPEED,CLK,CLR,K1,K2,K3。

SPEED控制彩灯循环速度;CLK为输入时钟脉冲信号端口;CLR为清零复位键;K1为暂停键;当K1为暂停状态时,通过控制K2和K3的四个给合来实现某种花形的显示;

输出端口有CLK1和STATE;

通过CLK1端口对显示模块输入时钟脉冲,达到循环亮灯的效果;

STATE键就是输入端K1和K2的组合,通过该键对显示模块的单独亮花形的控制;

显示控制模块:

输入端口CLK1,CLR,STATE;

CLK1为上一时序控制模块的输出端,通过该端口对彩灯的循环显示提供脉冲信号;CLR键为清零复位键;

STATE键为控制单个花形的显示;

输出端口LED0,LED1,LED2,LED3,LED4,LED5,LED6,LED7,LED8;

LED0至LED8为灯的显示情况。

花形为:

四方形:

OOO十字形:

XOXZ形:

OOO工字形:

OXO

OXOOOOXOXOXO

OOOXOXOOOOOO

系统开始运行时,把CLR打到高电平,系统清零,全部灯不亮。

把SPEED键打到高电平,把CLR打到低电平,把K1打到低电平,再把CLK键打到高

电平时,彩灯以2秒的速度循环显示,把SPEED键打到低电平时,彩灯以1秒的速度

循环显示。

把K1打到高电平,彩灯没有显示

(1)把K2打到低电平,K3打到低电平,彩色显示四方形;

(2)把K2打到低电平,K3打到高电平,彩色显示十字形;

(3)把K2打到高电平,K3打到低电平,彩色显示Z形;

(4)把K2打到高电平,K3打到高电平,彩色显示U字形;

三:

ASM图及框架

Process(CLK,CLR,K1,K2,K3,K4)

系统的结构图如下:

四:

编译的调试,处理和仿真

经过调试,处理和仿真,本系统成功运行,具体的图如下:

时序模块的仿真图:

显示仿真模块仿真图:

总芯片仿真图如下:

五:

下载验证

经下载验证,本系统成功运行:

引脚图如下:

芯片下载图如下:

六:

调试分析和结果

系统开始运行时,把CLR打到高电平,系统清零,全部灯不亮。

把SPEED键打到高电平,把CLR打到低电平,把K1打到低电平,再把CLK键打到高

电平时,彩灯以2秒的速度循环显示,把SPEED键打到低电平时,彩灯以1秒的速度

循环显示。

把K1打到高电平,彩灯没有显示

(1)把K2打到低电平,K3打到低电平,彩色显示四方形

OOO

OXO

OOO

(2)把K2打到低电平,K3打到高电平,彩色显示十字形;

XOX

OOO

XOX

(3)把K2打到高电平,K3打到低电平,彩色显示Z形;

OOO

XOX

OOO

(4)把K2打到高电平,K3打到高电平,彩色显示U字形;

OXO

OXO

OOO

七:

附录I

彩灯控制器的源程序

时序控制模块SX的源程序如下:

----------------------------------------------------------------------------------

--Company:

--Engineer:

--

--CreateDate:

15:

09:

0401/09/2008

--DesignName:

--ModuleName:

sx

--ProjectName:

--TargetDevices:

--Toolversions:

--Description:

--

--Dependencies:

--

--Revision:

--Revision0.01-FileCreated

--AdditionalComments:

--

----------------------------------------------------------------------------------

libraryIEEE;

useIEEE.STD_LOGIC_1164.ALL;

useIEEE.STD_LOGIC_ARITH.ALL;

useIEEE.STD_LOGIC_UNSIGNED.ALL;

---