CadenceAllegro学习心得分享.docx

《CadenceAllegro学习心得分享.docx》由会员分享,可在线阅读,更多相关《CadenceAllegro学习心得分享.docx(56页珍藏版)》请在冰豆网上搜索。

CadenceAllegro学习心得分享

PCB学习心得

一、写在前面的话

本文将着重介绍一个PCB菜鸟的学习心得,详细的记录每个要点的操作方法和原因,着重将这个过程中学习到的一些东西与大家分享。

同时如发现有任何问题或者是好的方法和建议,请大家指出,共同学习、共同进步!

——PCB路漫漫其修远兮,吾将上下而求索

接下来将从PCB设计的怎个流程和大家分享

二、PCB设计前的准备

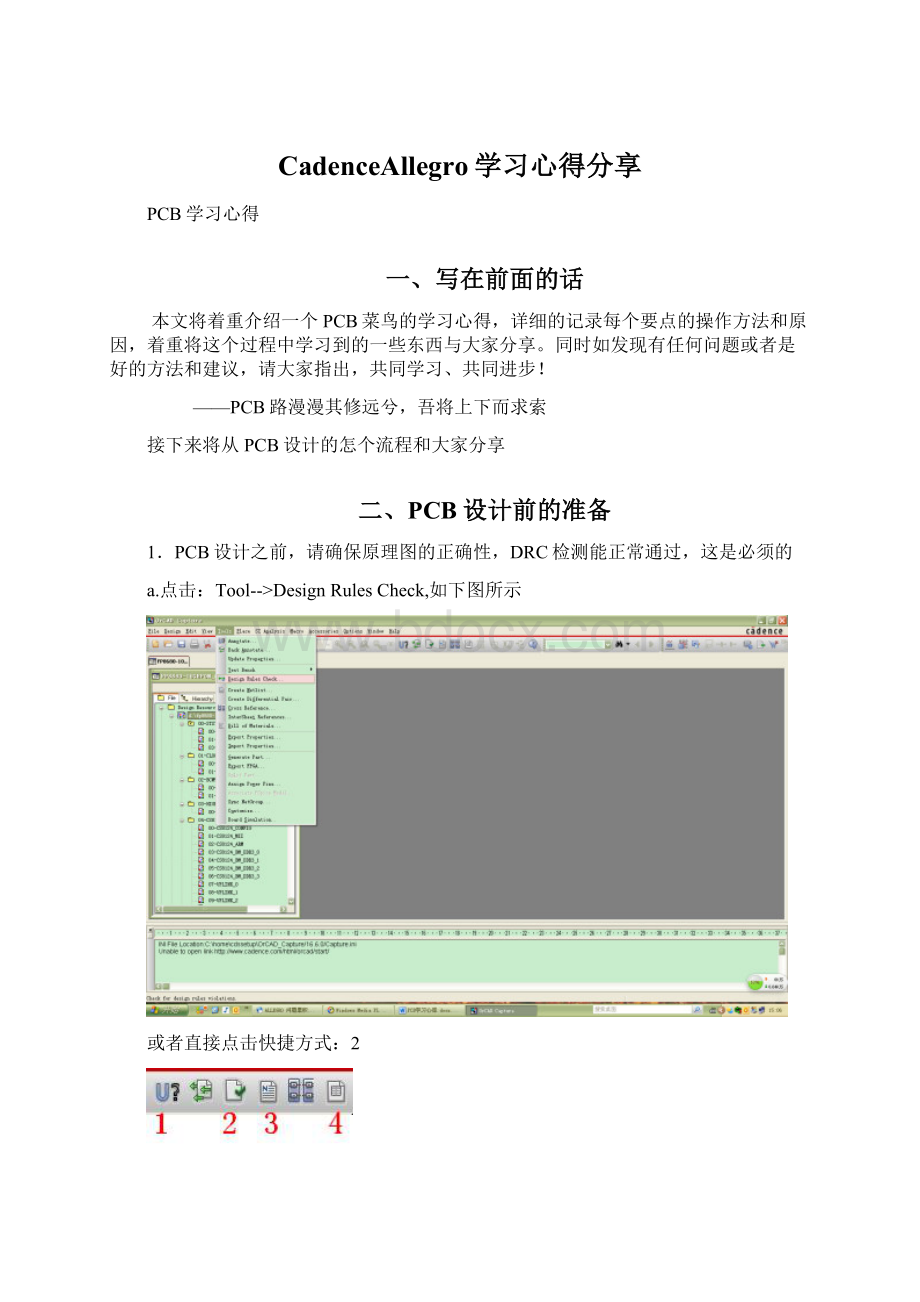

1.PCB设计之前,请确保原理图的正确性,DRC检测能正常通过,这是必须的

a.点击:

Tool-->DesignRulesCheck,如下图所示

或者直接点击快捷方式:

2

具体的每个操作的说明:

元器件快速排序

DRC检查(作用同上)

网表生成

元器件清单

注:

元器件生成清单,点击上图中的4,需要在下图位置添加PCB封装属性即可得到元器件清单BOM

具体操作为在Header添加tPCBFootprint,在Combinedpropertystring添加t{PCBFootprint}

2.DRC检测规则按如下规则即可

如图的检测规则为默认,如有特殊需求可自行修改!

出现最多的“WARNING(ORCAP-1829):

PossiblepintypeconflictICXX”这个是指CPLD或者FPGA的IO口方向设置,可以忽略!

由于后期可能需求调整IO口的位置,现在操作无意义。

注:

1、所选的原理图封装一定要正确,PCB封装同时也应该制作好。

2、原理图的封装应该选择合理,避免在实际的PCB绘制过程中存在问题。

三、DXF文件的导入

1.新建一个.brd文件

注意:

选择Mechanicalsymbol

2.按如下操作File-->Import-->DXF

点击Edit后,出现如下的画面,并且按数字的标记操作即可。

3.完成如上两步,点击OK,再点击Import,出现了Dxf文件。

找到板框外形后,点击Edit-->Change,在Options中选择BoardGeometry,在子项中选择Outline

然后选择一个封闭的外框作为Outline,如下图,然后保存。

注:

封闭的Outline便于后面Z-copy的使用,在RouteKeepin和铺地平面时使用

四、PCB初始设置

1.首先新建一个Bord类型的brd文件,将工作区域设置的足够大,保证能够将整个板框放置在工作区域内。

2.设置PCB库的路径Setup-->UserPreferences-->Path-->Library子项的Padpath和Psmpath路径指向PCB库的位置。

注:

如果想要使PCB中的光标显示为大十字(如下图所示),操作方法:

Setup-->UserPreferences-->Display-->Cursor中的Pcb_cursor的Value值选择“infinite”即可。

3.将刚才制作好的DXF文件,相当于一个结构器件导入,方便以后DXF文件的变更或者是修改都比较方便。

首先确保如下无问题:

确保DXF文件放入刚才设置的Library路径下面

确保PCB工作区域足够大

现在PCB工作单位设置为mm,和刚才导入的DXF文件单位保持一致。

具体操作步骤:

Place-->Manually弹出对话框,在AdvancedSettings选项勾选上Library子项

接下来选择PlacementList项,在下拉菜单中选择MechanicalSymbols,在列表中选择刚才制作好的DXF文件,鼠标点击屏幕即可将DXF文件放置在工作区域中,然后点击OK

然后可以将PCB左下角设置为坐标(0,0)点,方法是在MoveOrigin中的X和Y坐标,分别填入DXF文件左下角的坐标即可实现。

至此,DXF文件导入就顺利的完成了,接着就是网表的导入,剩下就是我们大展拳脚的时候了\(^o^)/~

五、PCB叠层设计

1.PCB的叠层设计严重影响着我们产品的EMC性能,一个好的叠层是我们EMC成败的基础。

层叠结构是影响PCB板EMC性能的一个重要因素,也是抑制电磁干扰的一个重要手段。

首先在叠层的时候应该先明白几个问题:

PCB板叠层数量

电源的数目和分布情况

2.多层板叠层推荐

12层板,叠层14层板,叠层

在具体时候可不同于上面的叠层设计

同时在设置叠层的时候,地平面和电源层一般设置为负片,信号层为正片,这样在电源分割时比较方便,而且电源平面也容易编辑。

注:

正片和负片的区别

正片:

在生成Gerber文件后,可见即可得;制板时在Gerber看到什么就是什么。

负片:

在生成Gerber文件后,可见即不可得,值板时在Gerber看到什么就没有什么。

被蚀

刻掉了。

正片的优点是如果移动元件或者过孔需要重新铺铜,有较全面的DRC校验。

负片的优点是移动元件或者过孔不需重新铺铜,自动更新铺铜,没有全面的DRC校验

3.具体的操作:

在每一行前面右键选择添加或者是删除当前层;当添加层后根据前面预期

的叠层设计命名,地平面和电源平面的Type类型选择Plane,片类型选择负片。

信号层的Type类型选择Conductor,片类型默认选择为正片。

所有信号和平面的材质均选择Copper,中间板层材质为FR-4。

这样PCB的叠层设计也就完成了,接下来可以在每一层上面绘制属于自己的蓝图了…..

六、区域约束规则

1.Xnet:

简单的说就是在两个不同的网络通过一个电阻或者电容等连接起来,电阻、电容两端的网络就是Xnet。

如图中的Net_A和Net_B分别是两个不同的网络,如果需要设置从A端到B的规则,则需要分别作两个网络的规则才可以,并且误差增加,所以需要寻找一种能够简单设置A到B端的规则的方法,那就是Xnet。

2.Xnet设置方法:

操作步骤:

Analysis-->SI/EMIsim-->Model_Assigment出现如下的画面

在DevType中选择需要使用Xnet设置的器件,一般情况下为电容或者电阻;之后点击CreateModel

点击OK

继续OK即可,之后就可以看到在DevType中SignalModel中出现Xnet属性。

自此,Xnet属性设置完成,如果想要删除Xnet属性,在Model下拉菜单中选择”NoModel”

注:

可以将原理图中同类想要设置Xnet的电容、电阻,可以添加有别于相同value的描述

3.差分对的建立和规则设置

首先打开区域约束规则界面如下图

具体的操作:

Electrical-->ECS-->Routing-->DifferentialPair

项目名称上右键Create-->ECS新建一个差分规则名称DIFF

StaticPhaseTolerance设置差分对等长最大差值,再设置差分对的走线规则,如果是走窄差分的话即两根线之间的线间距为12mil,如果走宽差分对的话线间距是15mil.

4.应用差分对规则

Electrical-->Net-->Routing-->DifferentialPair

项目名称上右键Create-->DifferentialPair点击AutoSetup,在+Filter中输入P或者+,在-Filter中输入N或者-,即出现符合条件的差分对,点击Create

在设置好的差分对后面ReferencedElectricalCset的下拉中选择上面设置的差分对约束规则DIFF。

如果还需要对差分对的总长度做约束,只需要在Net-->Routing下面的TotalEtchLength中设置总长度即可实现差分对的双重约束。

5.物理约束规则

首先明白物理约束规则主要是约束一个区域的,重在约束一个区域中的孔的类型、线的宽度、Neck的宽度,同时还需要考虑区域中电源的特殊地位。

明白所绘制的PCB的区域主要有哪些,比如说BGA芯片的PIN-PIN间距为0.8mm和1mm,这就决定了在扇出、走线时的不同,所以需要有不同的物理约束规则。

建立PCS的方法类似于上面建立ECS的方法:

Physical-->PCS-->AllLayers

项目名称上右键Create-->PCS新建一个物理区域规则名称

新建好的规则后面设定不同的走线宽度、Neck线宽、过孔等。

在Net选项下面,同样的方法Create-->NetClass,新建一个Net组

找到所有的电源网络,右键点击AddClass,然后选择刚才新建的Net组,即可将电源网络全部加入网络组中。

随后在ReferencedPhysicalCset下拉中选择PCS中的电源网络规则即可,这样所有的电源网络就加入到了电源网络的物理规则约束当中了,其余的网络同样的方法选择默认组即可。

完成上面的操作算是基本上是完成规则的设计,但是假如当在BGA区域中出现电源网络应该怎样处理呢?

这两个到底该怎么选择呢?

回答是:

通过设置不同物理规则区域约束之间的优先级,让规则更好的发挥作用。

Region下面先新建几个物理区域规则的名字,然后不同区域中两个约束规则的优先级

注:

在PCB中添加区域约束规则的方法

Shape-->Rectangular,然后再右侧Options中选择ConstraintRegion,下面的层选择All,然后在AssigntoRegion中选择PCS中新建的区域约束规则,在PCB上绘制区域就可以了。

如果所示就是已经画好的区域,另外如果未对区域命名或者需要更改区域的类型,可以如下操作:

Shape-->SelectShaporVoid,然后选择Shape在右侧的AssigntoRegion中选择区域类型。

6.空间约束规则

空间约束规则主要是约束每一个区域中的线、孔、焊盘等之间的距离的约束规则,从每一个细小的点出发,约束这个PCB的布局和走线。

具体的操作和上面的物理约束规则类似,这里就不一一的操作说明了。

约束结果参照上图。

七、快速布局布线

由于现在每个单板上有很多布局结构类似的器件和布线,这就需要有一个快速布局来提高工作效率。

很多之前做过的项目中有类似的结构,这就需要快速的布线来提高布线的精度和准确度。

1.快速布局方法

先自己手动放置好一个模块,可以布局也可以走线,如下图所示。

生成模块方法:

Setup-->ApplicationMode-->PlacementEdit或者是快捷菜单

选中要生成模块的区域-->鼠标放于选中器件区域的地方-->右键选择PlacereplicateCreate-->右键点击Done-->左键点击工作区域,然后生成unnamed.mdd,在应用此文件时必须放置于当前PCB目录文件下面,也适用于不同PCB之间、属性完全相同的模块。

适用于所有封装完全一致,Value值也一致的器件。

应用模块的方法:

前提是需要使用和原理图交叉布局的方法,将同一个模块的器件放置在集中的区域,这样便于两个模块之间的完全匹配。

在同样的PlacementEdit模式下-->选中需要应用模块的器件-->右键选择PlacereplicateApply-->选择刚才的unnamed.mdd,或者是Browse其它的模块名字,即可得到一个同样的模块。

具体的操作方法如下:

操作说明:

在手动布局的情况下还可以使用对齐功能,保证器件摆放美观、布线方便。

首先需要将两个器件之间的距离调整好,可以使用大格点的方法放置,同样在PlacementEdit模式下-->选择器件-->右键选择AlignComponents-->Done即可实现相对于另一边的对齐功能。

Allegro16.3不支持等间距的对齐方法,并且只能对齐Top层或者是Bottom层,不能两层同时选择对齐。

2.多人布局方法

由于现在单板器件越来却多,需要小模块的布局也是越来越多,这样就可以采用多人布局的方法共同实现PCB的布局。

每个人都只能放置属于自己的那一块器件,放置在单板的任意位置,然后Export-->Placement,然后集合多人的布局,分别采用Import-->Placement即可。

3.快速布线方法

当我们需要从A板拷贝B板PCB布线的时候,就需要使用Sub-Drawing功能。

首先我们应该明白需要从B板拷贝什么到A板,在拷贝之前应该保证在选择的时候能最小化的影响A板,而又最大的满足我们的需求。

当我们想要从B板拷贝布线的时候,可以在File-->Export-->Sub-Drawing,在右侧打开所有的层,Find中选择Net、Shaps、Clines和Vias,Options中选择Preservenetsofshaps、Preservenetsofvias和PreserveTestpointonvias

如下图所示:

选中需要拷贝的网络,

在Command中输入需要导出的参考点,比如x00

如上操作即可得到一个clp文件。

导入A前的准备,先确保B导出的参考点和A中的那个参考点是对应的,这样可以避免后期移动过程中再出问题。

选择导入Import-->Sub-Drawing,选择我们刚才导出的Clp文件。

然后在Command中输入

导入坐标参考点,比如也是(0,0),那我们只要在里面输入x00即可。

在平时经常备份PCB文件,这样在严重的误操作情况下,可以采用这种办法保证还能达到理想的情况,将损失降到最低,同时也可以大大的提升工作效率。

八、覆铜操作

1.正片的覆铜方法

正片的覆铜主要是在信号层面,操作如下:

Shape-->Rectangular等其它形状或者是快捷菜单,在右侧的Options中选择Etch和需要覆铜的层,铜皮的属性选择动态Dynamiccopper。

同时下面的Assignnetname可以选择这块铜皮的网络,也可以先画出铜皮后再使用Shape-->SelectShaporVoid或者ShapeSelect选中需要命名的铜皮,点击网络或者是在Options的AssigntoRegion中选择网络。

铜皮的编辑方法

a.使用ShapEditBoundary,选中铜皮-->点击铜皮的边缘-->选择需要割掉的部分(每次会割掉较小的那一部分)

b.使用Shape-->SelectShaporVoid或者ShapeSelect,选中铜皮后点击边界,在边界处拉动光标即可实现铜皮的编辑功能。

c.采用Shape-->MergeShapes选中需要合并的两块铜皮即可,但是需要保证两块铜皮的Net是一样的,只有这样才能合并。

上述操作,前面一个表示操作前的动作,后面一个表示操作后的结果。

在具体的设计过程中应该合理的使用,发挥每个不同的功效。

2.负片覆铜

负片覆铜主要针对电源平面和地平面。

首先是负平面的创建。

平面的创建采用Z-copy的方式建立。

具体操作:

Edit-->Z-copy,右侧的设置如图然后选择RouteKeepin的外形Shape,就可以得到形状和RouteKeepin一模一样的地平面。

铜皮的编辑方法同正片

多电源平面的分割方法

当一个电源平面又多个小电源出现时,这时就可以采用AntiEtch的方法。

具体操作如下:

Add-->line,再右边的Options的设置如下,AntiEtch的宽度设置为20mi,保证两个铜皮的距离不至于太近。

然后将电源平面分割成合理的形状,同时需要考虑大电流处的铜皮不能太窄,保证能够通过足够的电流。

画完AntiEtch后,Edit-->SplitPlane-->Create,在下拉菜单中选择需要分割的电源平面,点击Create-->在对应的分割区域选择正确的网络即可。

注:

如果网络分割太多,直接寻找网络不方便,可以一路Cancel,等最后再依据上面正片命名铜皮的方法执行。

这样就可完成所有平面的覆铜,其实在布局时就应该考虑到后期覆铜问题,这样可以事半功倍的。

九、丝印

1.首先丝印的方向

第一种:

正面:

从左到右,从下到上反面:

从右到左,从下到上

第二种:

正面:

从左到右,从上到下反面:

从右到左,从上到下

总之就是正反面左右反,上下不变,所有丝印保持一致即可。

2.丝印的大小

最好是IC等大器件一个大种类,阻容及其它一个种类即可;但是当BGA区域丝印摆放困难时可以再使用一个种类,或者也可以将BGA密集区域的丝印在PDF文件中,附带PCB一起查看已可以。

同时丝印的方向最好和器件的方向保持一致,这样有利于调试时方便寻找。

注:

在PCB上添加的其它丝印线,画在BoardGeometry-->Silkscreen_Top/Bottom

十、PCB走线和优化

1.高速线走线注意事项

首先应该设置好差分对规则,在BGA区域可采用Neck模式走线。

高速差分线在打孔换层的时候,应该同时打孔并且需要在两侧打上地孔。

注:

放置地孔的方法,应该尽量在走好差分线之后就放置,避免后期打孔带来的其它问题。

选择Copy-->在Find中选择Vias-->在Options中选择RetainnetofVias,选择合适的孔放置在差分线换层处。

同一组内的收和发应该最好在不同层,或者在同一层中距离应该够大,起码应该大于3倍线宽。

而且在同一层当中,尽量把收和发分开,即收在一遍、发在另一边。

在时钟等高速器件下面尽量避免高速线穿过,避免信号之间的串扰。

2.高速线优化

在走高速线时,多采用圆弧走线而不是45度角走线,保证阻抗变化连续。

圆弧优化方法如下:

首先Route-->Slide或者是快捷菜单-->Options菜单栏中VertexAction选择ArcCorner,然后在工作区域中点击差分线的拐角出的45度线,调整到满意为止。

按照上述操作可将每段差分线调整为圆弧走线,但是在差分线的两端处调整起来较为复杂,可采用下面的方法实现。

整个网络优化

Route-->Custom或者是快捷菜单-->Options菜单栏中Conrnertype中选择Arc,Restrictsegentryforpadsoftype中选择All,下面的两项选择默认。

然后选择要改变成圆弧型的差分线。

这样既可将所有的差分线优化完成。

注1:

为什么不一开始就用圆弧形走线呢?

由于差分线是最早走的线,后续好需要做适当的修改,但是圆弧形走线调整起来比较复杂,所以先使用45度角走线,最后再优化为圆弧形走线既可,这样调整和优化两不误。

同时也能达到阻抗连续、保证较好的EMC特性。

注2:

在上述优化完成PCB后,需要在仔细的检查差分走线,有可能部分地方还是需要再做微小的调整,千万不可大意。

差分线打孔换层需要注意的问题。

差分线打孔换层的地方其它层处的pads需要移除,而且差分线进和出的层不能离的太近,这样做的结果会导致下面部分的Stub太长,类似于一个抽头,这样会产生严重的信号干扰。

正确的做法是需要进和出的层离的较远,这样Stub很短,信号质量较好。

例如一块14层板,信号从顶层进入,最好打孔换层到L12(信号层)。

如果从顶层换到底层会导致两侧没有完整的平面包围,信号质量也会受到较大的干扰。

除了采用上述方法外,对多层板来说,也可以采用背钻的方法得到较好的信号质量。

除了上述需要注意的地方,还有就是高速差分线最好不要跨两侧的平面,比如差分线在走线的时候在电源平面侧从3.3V到1.5V,这样也会出现阻抗不连续的情况。

还有就是差分线换层过孔附近的层应该被挖空。

注:

挖空方法:

首先最好将需要将换层的差分线高亮,打开要挖割的平面,这样就能很好的分清哪些需要被挖空的地方。

点击Shape-->ShapeVoidRectangle或者是快捷菜单-->点击需要挖割平面-->在右侧的Options中Cornets处选择Round和%ofShortedge,后面设置为99即可。

这个选项只有在Allegro16.5或者更高的版本中才有。

挖空后的效果。

此外还可以复制外控区域,只限于同一层的同一网络可以应用。

操作如下:

Shape-->ManualVoid-->Copy-->点击需要复制的外框,然后放置到另外一个需要挖空的地方。

挖空区域的删除、移动等操作同样在Shape-->ManualVoid目录下面。

这么多的高速信号优化就可以看出在PCB布线中的重要性,尤其是在10GXAUi、10G-KR、10GSerdes或者更高的40G、100G更是重中之重。

这方面一定不能马虎大意,否则到时候PCB出现干扰、不容易重现等现象时就非常纠结了,问题很难查找,不容易定位、也不容易调试。

布线优化

由于Allegro允许工程师自定义Skill,完成很多功能,比如接下来要用到的Stub检查。

具体的Skill加载方法私下交流讨论。

在自定义菜单中选择查找Stub的Skill,然后点击Stubs挨个删除,如果非常多可以选择鼠标工具哦,例如鼠标电击器、按键精灵等!

同时比较实用的还有NC_Vias检查,检查出PCB中没有Net的过孔,同时删除。

十一、PCB板的属性

1.Mark点放置,操作如下:

Place-->Manually弹出对话框,在AdvancedSettings选项勾选上Library子项

选择PlacementList项,在下拉菜单中选择MechanicalSymbols,在列表中选择Mark点,放置在PCB的边缘,每块PCB板Top和Bottom都至少需要三个Mark点,放置在不同的角落即可。

2.静电防护和无铅标识,操作同Mark点放置。

3.生产工艺框,PCB生产完成后,PCB厂家印刷自己的信息在上面。

规格一般是:

7*20mm

除此之外还需添加PCB料号,和WDK商标LOGO,放置在醒目的位置。

十二、Gerber导出

1.导出Gerber前的准备

在allegro中打开Setup-->DesignParameters菜单,调出设置对话框

单位就为之前绘制PCB的单位,精度最少为2,其余的默认即可。

在allegro中打开Shape->GlobalDynamicShapeParameters菜单,调出设置对话框,Dynamicfill选Smooth,如下图。

在Voidcontrols选择GerberRS274X

2.Artwork设置

选择菜单Manufacture>Artwork,出现ArtworkControlForm对话框,如下:

Devicetype选择GerberRS274X,Format选择Integerplaces:

2,DecimalPlaces:

4

3.Artwork底片控制文件的建立

如上图所示菜单中,选择FilmControl选项,如下图所示

左侧显示的就是我们需要建立的Artwork底片文件,右边的是生成底片的属性。

一般需要注意的就是Plotmode选项中的Positive(正片)和Negative(负片),此处的选择同前面叠层设置的一致,信号层选择正片而电源和地平面选择负片即可。

左边的底片菜单上面右键:

Add添加新的底片文件,也可以在子菜单下面选择其中包含的内容,