进制10进制BCD码数码转换器设计Word.docx

《进制10进制BCD码数码转换器设计Word.docx》由会员分享,可在线阅读,更多相关《进制10进制BCD码数码转换器设计Word.docx(13页珍藏版)》请在冰豆网上搜索。

进制10进制BCD码数码转换器设计Word

摘要

BCD码亦称二进码十进数或二-十进制代码。

用4位二进制数来表示1位十进制数中的0~9这10个数码。

是一种二进制的数字编码形式,用二进制编码的十进制代码。

BCD码这种编码形式利用了四个位元来储存一个十进制的数码,使二进制和十进制之间的转换得以快捷的进行。

本文就是在quartus软件环境下利用VHDL语言将输入的八位二进制转换为BCD十进制数并且在数码管中显示出来。

关键词:

二--十进制转换器,BCD码,quartus,VHDL。

2进制-10进制(BCD码)数码转换器设计

1原理分析

BCD码这种编码形式利用了四个位元来储存一个十进制的数码,使二进制和十进制之间的转换得以快捷的进行。

这种编码技巧,最常用于会计系统的设计里,因为会计制度经常需要对很长的数字串作准确的计算。

相对于一般的浮点式记数法,采用BCD码,既可保存数值的精确度,又可免却使电脑作浮点运算时所耗费的时间。

此外,对于其他需要高精确度的计算,BCD编码亦很常用。

此处要介绍的是八位二进制转BCD码的硬件实现,采用左移加3的算法,具体描述如下:

(1)、左移要转换的二进制码1位

(2)、左移之后,BCD码分别置于百位、十位、个位

(3)、如果移位后所在的BCD码列大于或等于5,则对该值加3

(4)、继续左移的过程直至全部移位完成

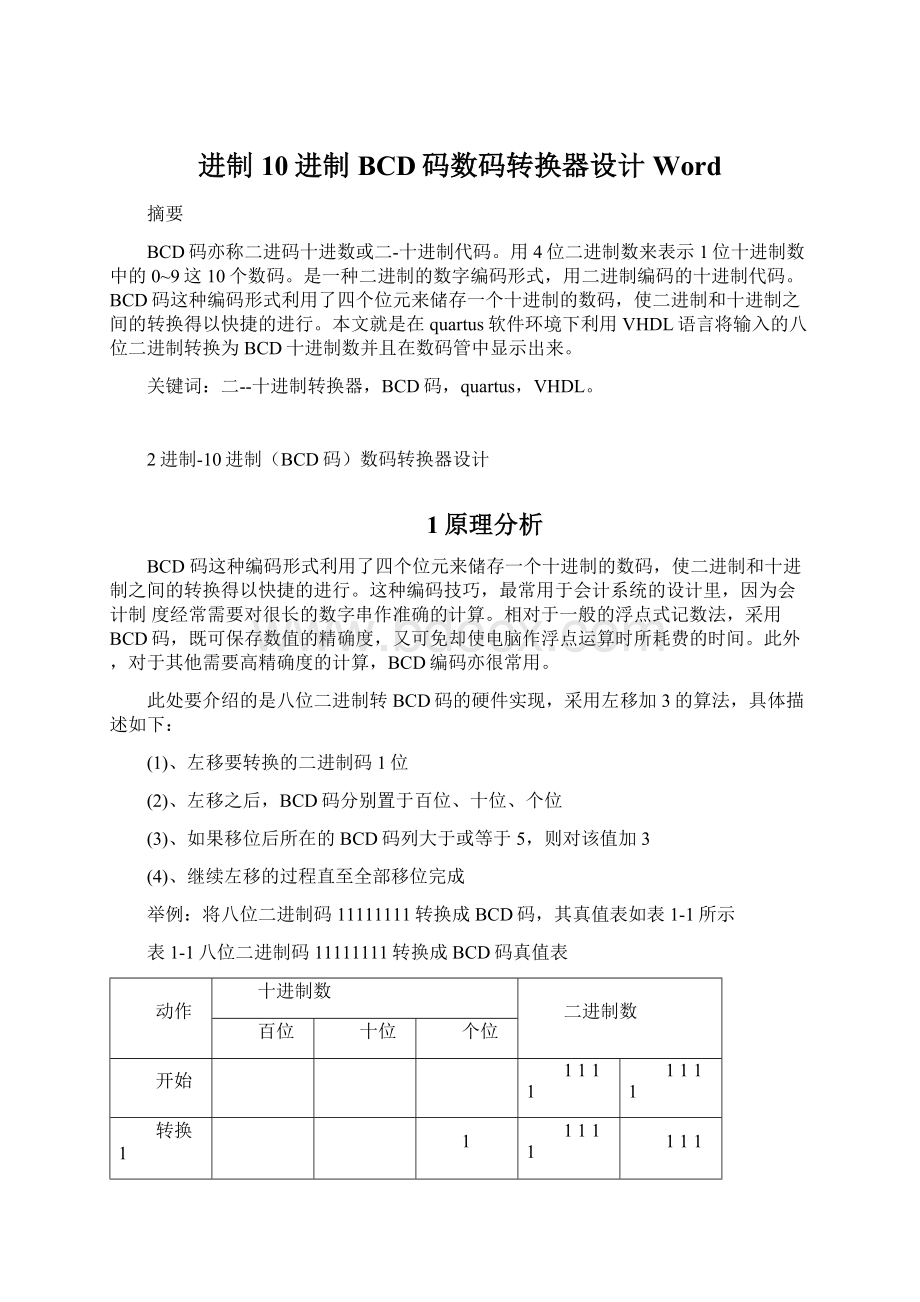

举例:

将八位二进制码11111111转换成BCD码,其真值表如表1-1所示

表1-1八位二进制码11111111转换成BCD码真值表

动作

十进制数

二进制数

百位

十位

个位

开始

1111

1111

转换1

1

1111

111

转换2

11

1111

11

转换3

111

1111

1

加3

1010

1111

1

转换4

1

0101

1111

加3

1

1000

1111

转换5

11

0001

111

转换6

110

0011

11

加3

1001

0011

11

转换7

1

0010

0111

1

加3

1

0010

1010

1

转换8

10

0101

0101

BCD

2

5

5

2设计思路

本次设计并没有用到左移的原理进行操作,直接对输出芯片的输出进行定义,虽然较为繁琐,但是原理却简单,所以才用此种方法,具体原理如下:

2进制-10进制(BCD码)的转换可以通过一个芯片实现,即输入的八位二进制码通过编程输出十进制码,八位二进制能表示的最大的数为“255”,即输出的十进制为三位数,此时输出的BCD码就要有12位,每四位代表一个数,此时可再利用一个芯片把输出的12位数重新分配到三个输出管脚中,每个管脚代表一位数,时钟信号每输变一次,输出数字的位也会变一次,即个、十、百位分别输出,同时芯片的selout输出端输出时钟信号的数字到下一个芯片的接收端,通过编程实现000对应110,001对应101,010对应011,即输出0的位置可以表示数码管中所显示数字的位,然后再通过芯片输出到七段数码管进行显示,具体流程图如图2-1所示:

图2-1设计总流程图

3设计程序

3.1二-十进制转换

原理图如图3-1所示:

图3-1二进制到十进制转换原理图

具体程序语言如下:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitybin2bcdis

port(din:

instd_logic_vector(7downto0);

bcd:

outstd_logic_vector(11downto0)

);

endbin2bcd;

architecturefunofbin2bcdis

begin

process(din)is

begin

casedinis

when"00000000"=>bcd<="000000000000";

when"00000001"=>bcd<="000000000001";

when"00000010"=>bcd<="000000000010";

when"00000011"=>bcd<="000000000011";

when"00000100"=>bcd<="000000000100";

when"00000101"=>bcd<="000000000101";

when"00000110"=>bcd<="000000000110";

when"00000111"=>bcd<="000000000111";

when"00001000"=>bcd<="000000001000";

when"00001001"=>bcd<="000000001001";

when"00001010"=>bcd<="000000010000"

。

。

。

。

。

when"01100011"=>bcd<="000010011001";

when"01100100"=>bcd<="000100000000";

。

。

。

。

。

when"11111000"=>bcd<="001001001000";

when"11111001"=>bcd<="001001001001";

when"11111010"=>bcd<="001001010000";

when"11111011"=>bcd<="001001010001";

when"11111100"=>bcd<="001001010010";

when"11111101"=>bcd<="001001010011";

when"11111110"=>bcd<="001001010100";

when"11111111"=>bcd<="001001010101";

whenothers=>bcd<=null;——此都为把二进制翻译为BCD码。

endcase;

endprocess;

endarchitecturefun;

3.2对十进制数分位

原理图如图3-2所示:

图3-2对十进制数分位原理图

具体程序语言如下:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitybcdis

port(din:

instd_logic_vector(11downto0);

y0,y1,y2:

outstd_logic_vector(3downto0)

);

endbcd;

architecturefunofbcdis

begin

process(din)is

begin

casedinis

when"000000000000"=>y0<="0000";y1<="0000";y2<="0000";

when"000000000001"=>y0<="0001";y1<="0000";y2<="0000";

when"000000000010"=>y0<="0010";y1<="0000";y2<="0000";

when"000000000011"=>y0<="0011";y1<="0000";y2<="0000";

when"000000000100"=>y0<="0100";y1<="0000";y2<="0000";

when"000000000101"=>y0<="0101";y1<="0000";y2<="0000";

when"000000000110"=>y0<="0110";y1<="0000";y2<="0000";

when"000000000111"=>y0<="0111";y1<="0000";y2<="0000";

when"000000001000"=>y0<="1000";y1<="0000";y2<="0000";

when"000000001001"=>y0<="1001";y1<="0000";y2<="0000

。

。

。

。

when"001001000110"=>y0<="0110";y1<="0100";y2<="0010";

when"001001000111"=>y0<="0111";y1<="0100";y2<="0010";

when"001001001000"=>y0<="1000";y1<="0100";y2<="0010";

when"001001001001"=>y0<="1001";y1<="0100";y2<="0010";

when"001001010000"=>y0<="0000";y1<="0101";y2<="0010";

when"001001010001"=>y0<="0001";y1<="0101";y2<="0010";

when"001001010010"=>y0<="0010";y1<="0101";y2<="0010";

when"001001010011"=>y0<="0011";y1<="0101";y2<="0010";

when"001001010100"=>y0<="0100";y1<="0101";y2<="0010";

when"001001010101"=>y0<="0101";y1<="0101";y2<="0010";

whenothers=>y0<="0000";y1<="0000";y2<="0000";——以上程序都为把输出的BCD码的个、十、百位分别存入y0、y1、y2中。

endcase;

endprocess;

endarchitecturefun

3.3分别输出十进制数

原理图如图3-3所示:

图3-3对三位分位输出原理图

具体程序语言如下:

libraryieee;;

useieee.std_logic_1164.all;

useieeestd_logic_unsigned.all;

useieeestd_logic_arith.all;

entityseltimeis

port(

clk2:

std_logic;

y0,y1,y2:

INstd_logic_vector(3downto0);

daout:

outstd_logic_ector(3downto0);

sel:

outstd_logic_vector(2downto0));

end;

architecturefunseltimeis

signalcount:

std_logic_vector(2downto0);

begin

sel<=count;

process(clk2)

begin

ifclk2'eventandclk2='1')then

if(count>="010")then

count<="000";

else

count<=count+1;

endif;

endif;

casecountis

when"000"=>daout<=y0;

when"001"=>daout<=y1;

when"010"=>daout<=y2;

whenothers=>daout<="0000";

endcase

endprocess

endfun;

3.4输出到数码管

原理图如图3-4所示:

图3-4输出到二极管原理图

具体程序语言如下:

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entitydeledis

port(num:

INstd_logic_vector(3downto0);

A:

OUTstd_logic;

B:

OUTstd_logic;

C:

OUTstd_logic;

D:

OUTstd_logic;

E:

OUTstd_logic;

F:

OUTstd_logic;

G:

OUTstd_logic;

DP:

OUTstd_logic

);

ENDDELED;

ARCHITECTUREfunOFDELEDIS

signalled:

std_logic_vector(6downto0);

BEGIN

A<=led(6);

B<=led(5);

C<=led(4);

D<=led(3);

E<=led

(2);

F<=led

(1);

G<=led(0);

DP<='0';

led<="1111110"whennum="0000"else

"0110000"whennum="0001"else

"1101101"whennum="0010"else

"1111001"whennum="0011"else

"0110011"whennum="0100"else

"1011011"whennum="0101"else

"1011111"whennum="0101"else

"1110000"whennum="0111"else

"1111111"whennum="1000"else

"1111011"whennum="1001"else

"1110111"whennum="1010"else

"0011111"whennum="1011"else

"1001110"whennum="1100"else

"0111101"whennum="1101"else

"1001111"whennum="1110"else

"1000111"whennum="1111";——把每一位输出用二极管显示

ENDfun;

3.5显示位数

原理图如图3-5所示:

图3-5显示位数原理图

具体程序语言如下:

LIBRARYieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

ENTITYdecode3_8IS

PORT(SEL:

INstd_logic_vector(2downto0);

Q:

OUTstd_logic_vector(7downto0)

);

ENDdecode3_8;

ARCHITECTUREaOFdecode3_8IS

BEGIN

Q<="11111110"whensel=0else

"11111101"whensel=1else

"11111011"whensel=2else

"11111111";

ENDa;

整个设计完成。

4整体设计电路图与仿真结果分析

4.1整体设计电路图

在quartus环境下把以上各个环节连成一个完整的电路,并且进行仿真试验,整个电路的电路原理图如图4-1所示:

图4-1电路原理图

4.2仿真结果

电路经编译后没问题然后进行仿真,在“Name”标签区内双击鼠标左键,弹出添加节点的对话框,把要显示的仿真的节点添加到标签区内仿真结果如图4-2所示:

图4-2仿真结果图

4.3仿真结果分析

对于仿真出来的波形,前七位为输出的十进制数,当输入二进制数时这个输出口都能输出正确的十进制数,中间八位是输入的二进制数,最后八位是正在显示的数的位,在25.5ns时,输入为00000010,即十进制的2,此时个位应该输出2,用七段数码管表示即是1101101,输出完全正确,由此可见,仿真结果正确,整个电路完成。

5小结与体会

经过一个星期的努力终于把整个课程设计给全部完成了,途中经历了各种艰辛,也出现了各种错误,在自己的努力和同学的帮助下也一一克服,更加明白了一个道理,那就是要想做好一件事情,必须真正的付出才行。

本次课程设计主要用到了quartus这个软件,以前基本上没有接触过这个软件,所以刚开始用的时候发现简直就是一个全新的东西,后来查阅了各种参考书,在网上也是查阅了各种资料然后才对quartus有了初步的认识,但是用起来还是手生的很,但是我知道这也没办法,其实也是对我自己接受新事物的一种锻炼,当我不停的使用这个软件时,才越来越发现这个软件的强大之处,不仅仅能通过编程实现各种功能,还有各种芯片可供仿真时使用,对一些芯片进行编程就可以实现其功能,然后进行仿真,就可以看到实际的效果,如果不行可以进行调试,然后再仿真直到成功为止,这样变可以节省成本,对实际的设计制作起着参考作用,如果实际制作东西的时候发现有错误整个电路就都浪费了,这样会对资源造成大量的浪费,而有了quartus这个软件就可以避免这个问题,把一些实验性的东西在电脑端实现,直到实验成功才去实际操作,节约成本的同时也节约了时间,总得来说,quartus对我们电路的实际设计和生产提供了很大的帮助,以后我要尽量多利用这个软件,争取熟练掌握它,为以后的工作提供便利。

刚拿到本次课程设计的题目时,感觉应该挺简单的,2—10进制的转化应该用一些芯片就可以解决了,但是当我真正的深入进去做的时候发现还是有很大的问题的,在quartus环境下一些芯片并没有那么好实现,只能每个过程每个过程的进行编程,在此又遇到另一个问题那就是在quartus环境下只有两种语言可以使用,即verilog和VHDL,但是这两种语言对我来说也是全新的,以前从来没有用到过的语言,所以又得从新学起,又是各种资料满天飞,经过一段时间之后也算终于初步了解了这门语言,虽然编程起来还是会有困难,

但是总也算磕磕绊绊的编了出来,当我把所有的程序都编完的时候心里非常高兴,以为终于可以告一段落了,但是后来编译的时候发现还是有很多错误,然后又经历了漫长而且痛苦的改程序的过程,在不知道改了多少次之后程序终于算是改正确了,然后编译完成,程序完全正确,心里的石头终于算是落下来了,当时的心情真是相当舒畅,说明经过自己的努力后完成的事情还是很值得骄傲的。

本次课程设计过程中也是遇到了各种各样的困难,编程时遇到困难,仿真时遇到困难,也出现了各种各样的错误,这些困难靠自己解决实在是很有难度,所以我就不停的查资料问同学,班里也有几个对这个软件比较熟悉的同学,在他们的帮助下困难都给解决了,在此,也感谢帮助过我的同学,我也深刻的理解到同学之间互相帮助的重要性,团队合作的重要性。

在课程设计过程中,很多次都想着放弃,直接在网上找个抄得了,但是最后都没有让自己放纵,事实证明最终也作出来了,这让我对以后人生的路也更加有信心了,让我明白了没有什么事情是做不成的,只要自己肯努力什么事情都能做的成,什么事情都能完满的完成

总的来说,这次课程设计对我的帮助是相当大的,不仅仅是在知识上和技术上,在思想层面也是一种提升,希望学校以后多开展类似的活动,让同学们多一些锻炼,而不是仅仅停留在纸面上。

参考文献

[1]伍时和.《数字电子技术基础》.清华大学出版社.2009

[2]谭会生、张昌凡.《EDA技术及应用》.西安电子科技大学出版社.2006

[3]康华光.《电子技术基础数字部分》.高等教育出版社.2006

[4]王冠、黄熙.《verilogHDL与数字电路设计》.机械工业出版社.2006

[5]张睿、赵艳华.《基于quartus的FPGA/CPLD的设计与应用》.电子工业出版社.2007

(本资料素材和资料部分来自网络,仅供参考。

请预览后才下载,期待您的好评与关注!

)