EDA实验报告.docx

《EDA实验报告.docx》由会员分享,可在线阅读,更多相关《EDA实验报告.docx(24页珍藏版)》请在冰豆网上搜索。

EDA实验报告

EDA实验报告

实验一:

组合电路的设计

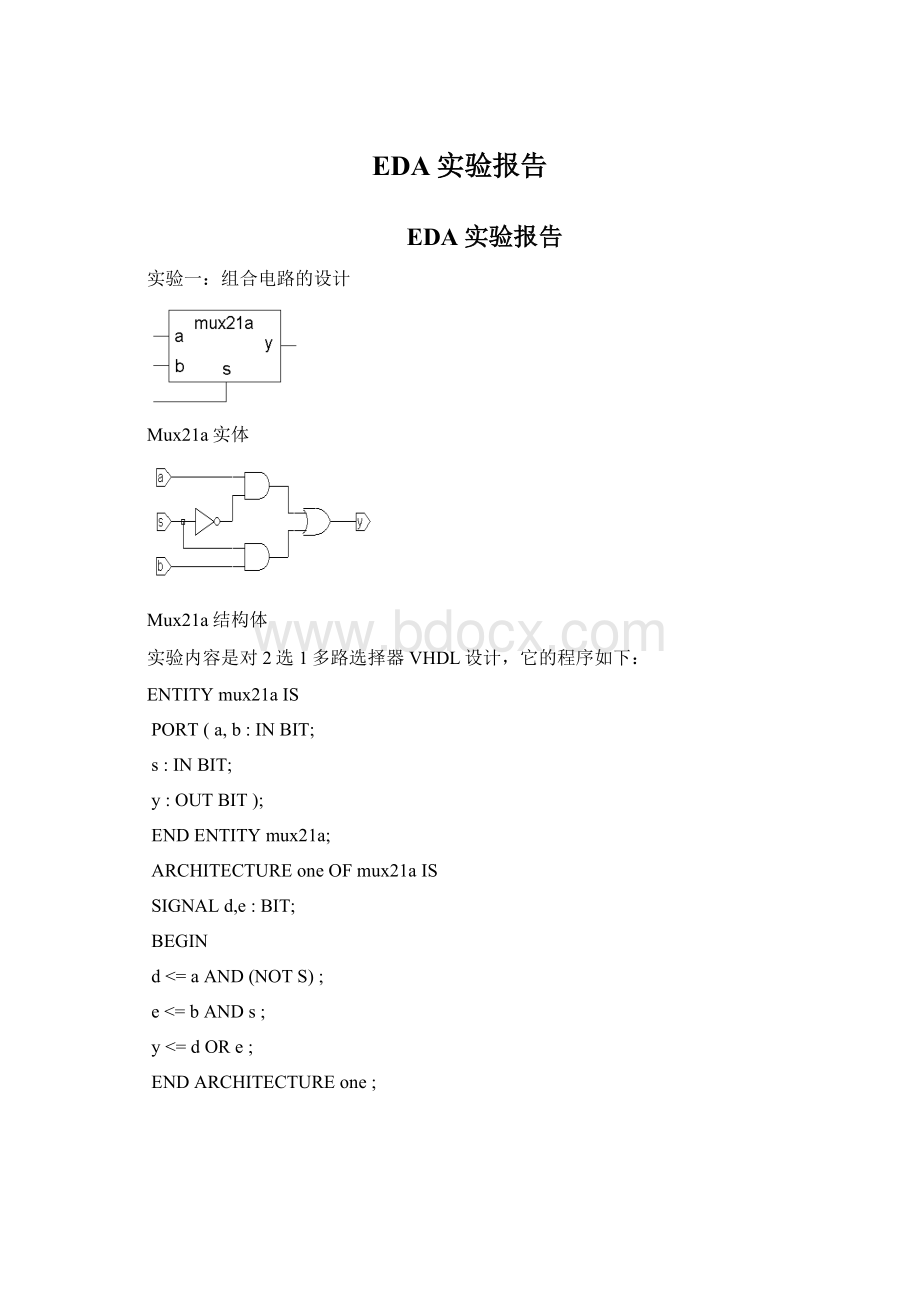

Mux21a实体

Mux21a结构体

实验内容是对2选1多路选择器VHDL设计,它的程序如下:

ENTITYmux21aIS

PORT(a,b:

INBIT;

s:

INBIT;

y:

OUTBIT);

ENDENTITYmux21a;

ARCHITECTUREoneOFmux21aIS

SIGNALd,e:

BIT;

BEGIN

d<=aAND(NOTS);

e<=bANDs;

y<=dORe;

ENDARCHITECTUREone;

Mux21a仿真波形图

以上便是2选1多路选择器的VHDL完整描述,即可以看成一个元件mux21a。

mux21a实体是描述对应的逻辑图或者器件图,图中a和b分别是两个数据输入端的端口名,s为通道选择控制信号输入端的端口名,y为输出端的端口名。

Mux21a结构体可以看成是元件的内部电路图。

最后是对仿真得出的mux21a仿真波形图。

实验二:

时序电路的设计

实验内容D触发器的VHDL语言描述,它的程序如下:

LIBRARYIEEE;

D触发器

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYDFF1IS

PORT(CLK:

INSTD_LOGIC;

D:

INSTD_LOGIC;

Q:

OUTSTD_LOGIC);

END;

ARCHITECTUREbhvOFDFF1IS

BEGIN

PROCESS(CLK)

BEGIN

IFCLK'EVENTANDCLK='1'

THENQ<=D;

ENDIF;

ENDPROCESS;

ENDbhv;

D触发器的仿真波形图

最简单并最具代表性的时序电路是D触发器,它是现代可编程ASIC设计中最基本的时序元件和底层元件。

D触发器的描述包含了VHDL对时序电路的最基本和典型的表达方式,同时也包含了VHDL中许多最具特色的语言现象。

D触发器元件如上图所示,其在max+plus2的仿真得出上面的波形

实验三:

设计含异步清零和同步时钟使能的加法计数器

实验内容一个带有异步复位和同步时钟使能的十进制加法计数器,它的程序如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYCNT10IS

PORT(CLK,RST,EN:

INSTD_LOGIC;

CQ:

OUTSTD_LOGIC_VECTOR(3DOWNTO0);

COUT:

OUTSTD_LOGIC);

ENDCNT10;

ARCHITECTUREbehavOFCNT10IS

BEGIN

PROCESS(CLK,RST,EN)

VARIABLECQI:

STD_LOGIC_VECTOR(3DOWNTO0);

BEGIN

IFRST='1'THENCQI:

=(OTHERS=>'0');--计数器异步复位

ELSIFCLK'EVENTANDCLK='1'THEN--检测时钟上升沿

IFEN='1'THEN--检测是否允许计算(同步使能)

IFCQI<9THENCQI:

=CQI+1;--允许计数,检测是否小于9

ELSECQI:

=(OTHERS=>'0');--大于9,计数值清零

ENDIF;

ENDIF;

ENDIF;

IFCQI=9THENCOUT<='1';--计数大于9,输出进位信号

ELSECOUT<='0';

ENDIF;

CQ<=CQI;--将计数值向端口输出

ENDPROCESS;

ENDbehav;

加法计数器的工作时序

程序说明RST是异步清信号,高电平有效;CLK是锁存信号;D[3..0]是4位数据输入端。

当EN为'1'时,多路选择器将加1器的输出值加载于锁存器的数据端;当EN为'0'时将"0000"加载于锁存器.

实验四:

用原图输入法设计8位全加器

实验内容:

完成半加器和全加器的设计。

实验目的:

熟悉利用max+plus2的原理图输入方法设计简单组合电路,掌握层次化设计的方法。

半加器的原理图如下

半加器的时序仿真波形如下:

将半加器的原理图选择File中的CreateDefaultSymbol项,此时即将当前文件变成了一个包装好的单一元件,并被放置在工程路径指定的目录中以备后用。

H_adder

一位全加器的VHDL描述,它的电路图如下

1位全加器的时序仿真波形如下

一位全加器可以由两个半加器和一个或门连接而成。

8位全加器设计原理图

八位全加器的波形仿真如上图

实验五:

用原理图输入法设计较复杂数字系统

实验目的:

熟悉原理图输入法中74系列等宏功能元件的使用方法,掌握更复杂的原理图层次化设技术和数字系统设计方法。

实验内容:

完成2位十进制频率计的设计,并进行仿真测试,给出仿真波形。

实验原理图:

时序仿真波形图:

实验分析:

F_IN是待测频率信号,CNT_EN是对待测频率脉冲计数允许信号CNT_EN高电平时允许计数,低电平时禁止计数。

仿真波形显示,当CNT_EN为高电平时允许conter8对F_IN计数,低电平时conter8停止计数,由锁存信号LOCK发出的脉冲,将conter8中的二个4位十进制数锁存进74374中,并由74374分高低位通过总线H[6..0]和L[6..0]输给74248译码输出显示,即测得的频率值。

此后由清零信号CLR对计数器conter8清零,以备下一周期计数之用。

实验六:

七段数码显示译码器设计

实验目的:

学习7段数码显示译码器设计,学习VHDL的CASE语句应用及多层次设计方法。

实验内容:

7段数码的程序和其波形方真,它的程序如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYDecL7SIS

PORT(A:

INSTD_LOGIC_VECTOR(3DOWNTO0);

LED7S:

OUTSTD_LOGIC_VECTOR(6DOWNTO0));

END;

ARCHITECTUREoneOFDecL7SIS

BEGIN

PROCESS(A)

BEGIN

CASEA(3DOWNTO0)IS

WHEN"0000"=>LED7S<="0111111";--X"3F"'0

WHEN"0001"=>LED7S<="0000110";--X"06"'1

WHEN"0010"=>LED7S<="1011011";--X"5B"'2

WHEN"0011"=>LED7S<="1001111";--X"4F"'3

WHEN"0100"=>LED7S<="1100110";--X"66"'4

WHEN"0101"=>LED7S<="1101101";--X"6D"'5

WHEN"0110"=>LED7S<="1111101";--X"7D"'6

WHEN"0111"=>LED7S<="0000111";--X"07"'7

WHEN"1000"=>LED7S<="1111111";--X"7F"'8

WHEN"1001"=>LED7S<="1101111";--X"6F"'9

WHEN"1010"=>LED7S<="1110111";--X"77"'10

WHEN"1011"=>LED7S<="1111100";--X"7C"'11

WHEN"1100"=>LED7S<="0111001";--X"39"'12

WHEN"1101"=>LED7S<="1011110";--X"5E"'13

WHEN"1110"=>LED7S<="1111001";--X"79"'14

WHEN"1111"=>LED7S<="1110001";--X"71"'15

WHENOTHERS=>NULL;

ENDCASE;

ENDPROCESS;

END;

7段译码器仿真波形

实验七:

数控分频器的设计

实验目的:

学习数控分频器的设计、分析和测试方法

实验原理:

数控分频器的功能就是当在输入端给定不同输入数据时,将对输入的时钟信号有不同的分频比,数控分频器就是用计数值可并行预置的加法计数器设计完成的,方法是将计数溢出位与预置数加载输入信号相接即可。

当输入输入不同的CLK时钟频率和预置值D时得不同FOUT电平

它的程序如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYDVFIS

PORT(CLK:

INSTD_LOGIC;

D:

INSTD_LOGIC_VECTOR(7DOWNTO0);

FOUT:

OUTSTD_LOGIC);

END;

ARCHITECTUREoneOFDVFIS

SIGNALFULL:

STD_LOGIC;

BEGIN

P_REG:

PROCESS(CLK)

VARIABLECNT8:

STD_LOGIC_VECTOR(7DOWNTO0);

BEGIN

IFCLK'EVENTANDCLK='1'THEN

IFCNT8="11111111"THEN

CNT8:

=D;--当CNT8计数计满时,D被同步预置给计数器CNT8

FULL<='1';--同时使溢出标志信号FULL输出为高电平

ELSECNT8:

=CNT8+1;--否则继续作加1计数

FULL<='0';--且输出溢出标志信号FULL为低电平

ENDIF;

ENDIF;

ENDPROCESSP_REG;

P_DIV:

PROCESS(FULL)

VARIABLECNT2:

STD_LOGIC;

BEGIN

IFFULL'EVENTANDFULL='1'

THENCNT2:

=NOTCNT2;--如果溢出标志信号FULL为高电平,D触发器输出取反

IFCNT2='1'THENFOUT<='1';

ELSEFOUT<='0';

ENDIF;

ENDIF;

ENDPROCESSP_DIV;

END;

上例的时序波形如下:

当给出不同输入值D时,FOUT输出不同频率(CLK周期=50ns)

数控分频器的功能就是当在输入端给定不同输入数据时,将对输入的时钟信号有不同的分频比,本设计中的数控分频器就是用计数值可并行预置的加法计数器设计完成的,方法是将计数溢出位与预置数加载输入信号相接即可。

实验八:

正弦信号发生器设计

实验目的:

进一步熟悉Max+plusII及其LPM_ROM与FPGA硬件资源的使用方法。

实验内容:

设计一个正弦波发生器,并进行仿真测试,给出仿真波形。

实验原理图:

时序波形仿真图:

信号发生器结构包含两个部分:

ROM的地址信号发生器,由6位计数器担任;一个正弦数据ROM,由LPM_ROM模块构成。

实验九:

8位十六进制频率计设计

实验目的:

学习较复杂的数字系统设计方法。

实验内容:

设计一个8位十六进制频率计,并进行仿真测试,给出仿真波形。

LIBRARYIEEE;--测频控制

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYftctrlIS

PORT(CLKK:

INSTD_LOGIC;--1Hz

CNT_EN,RST_CNT,LOAD:

OUTSTD_LOGIC);

ENDftctrl;

ARCHITECTUREbehavOFftctrlIS

SIGNALDIV2CLK:

STD_LOGIC;

BEGIN

PROCESS(CLKK)

BEGIN

IFCLKK'EVENTANDCLKK='1'THENDIV2CLK<=NOTDIV2CLK;

ENDIF;

ENDPROCESS;

PROCESS(CLKK,DIV2CLK)

BEGIN

IFCLKK='0'ANDDiv2CLK='0'THENRST_CNT<='1';

ELSERST_CNT<='0';ENDIF;

ENDPROCESS;

LOAD<=NOTDIV2CLK;CNT_EN<=DIV2CLK;

ENDbehav;

LIBRARYIEEE;--32位锁存器

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYREG32BIS

PORT(LK:

INSTD_LOGIC;

DIN:

INSTD_LOGIC_VECTOR(31DOWNTO0);

DOUT:

OUTSTD_LOGIC_VECTOR(31DOWNTO0));

ENDREG32B;

ARCHITECTUREbehavOFREG32BIS

BEGIN

PROCESS(LK,DIN)

BEGIN

IFLK'EVENTANDLK='1'THENDOUT<=DIN;--时钟到来时,锁存输入数据

ENDIF;

ENDPROCESS;

ENDbehav;

LIBRARYIEEE;--32位计数器

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYcounter32bIS

PORT(ENABL,CLR,FIN:

INSTD_LOGIC;

DOUT:

OUTSTD_LOGIC_VECTOR(31DOWNTO0));

ENDcounter32b;

ARCHITECTUREbehavOFcounter32bIS

SIGNALCQI:

STD_LOGIC_VECTOR(31DOWNTO0);

BEGIN

PROCESS(ENABL,CLR,FIN)

BEGIN

IFCLR='1'THENCQI<=(OTHERS=>'0');--清零

ELSIFFIN'EVENTANDFIN='1'THEN

IFENABL='1'THENCQI<=CQI+1;

ENDIF;

ENDIF;

ENDPROCESS;

DOUT<=CQI;

ENDbehav;

libraryieee;

useieee.std_logic_1164.all;

entitypreqtestis

port(clk1hz:

instd_logic;

fsin:

instd_logic;

dout:

outstd_logic_vector(31downto0));

endpreqtest;

architecturestrucoffreqtestis

componentftctrl

port(clkk:

instd_logic;

cnt_en:

outstd_logic;

rst_cnt:

outstd_logic;

load:

outstd_logic);

endcomponent;

componentcounter32b

port(fin:

instd_logic;

clr:

instd_logic;

enabl:

instd_logic;

dout:

outstd_std_logic_vector(31downto0));

endcomponent;

componentreg32b

port(lk:

instd_logic;

din:

instd_std_logic_vector(31downto0);

dout:

outstd_std_logic_vector(31downto0));

endcomponent;

signaltsten1:

std_logic;

signalclr_cnt1:

std_logic;

sigalload1:

std_logic;

sigaldt01:

std_std_logic_vector(31downto0);

sigalcarry_out1:

std_std_logic_vector(6downto0);

begin

u1:

ftctrlportmap(clkk=>clk1hz,cnt_en=>tsten1,

rst_cnt=>clr_cnt1,load=>load1);

u2:

reg32bportmap(lk=>load1,din=>dto1,dout=>dout);

u3:

counter32bportmap(fin=>fsin,clr=>clr_cnt1,

enabl=>tsten1,dout=>dt01);

endstruc;

时序波形仿真图:

实验十:

序列检测器设计

实验目的:

用状态机实现序列检测器的设计,了解一般状态机的设计与应用。

实验原理:

序列检测器可用于检测一组或多组由二进制码组成的脉冲序列信号,当序列检测器连续收到一组串行二进制码后,如果这组码与检测器中预先设置的码相同,则相同,则输出1,否则输出0。

实验内容:

描述的电路完成对序列数“11100101”的检测,当这一串序列数高位在前(左移)串行进入检测器后,若此数与预置的密码数相同,则输出“A”,否则仍然输出“B”。

它的程序如下:

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYSCHKIS

PORT(DIN,CLK,CLR:

INSTD_LOGIC;--串行输入数据位/工作时钟/复位信号

AB:

OUTSTD_LOGIC_VECTOR(3DOWNTO0));--检测结果输出

ENDSCHK;

ARCHITECTUREbehavOFSCHKIS

SIGNALQ:

INTEGERRANGE0TO8;

SIGNALD:

STD_LOGIC_VECTOR(7DOWNTO0);--8位待检测预置数

BEGIN

D<="11100101";--8位待检测预置数

PROCESS(CLK,CLR)

BEGIN

IFCLR='1'THENQ<=0;

ELSIFCLK'EVENTANDCLK='1'THEN--时钟到来时,判断并处理当前输入的位

CASEQIS

WHEN0=>IFDIN=D(7)THENQ<=1;ELSEQ<=0;ENDIF;

WHEN1=>IFDIN=D(6)THENQ<=2;ELSEQ<=0;ENDIF;

WHEN2=>IFDIN=D(5)THENQ<=3;ELSEQ<=0;ENDIF;

WHEN3=>IFDIN=D(4)THENQ<=4;ELSEQ<=0;ENDIF;

WHEN4=>IFDIN=D(3)THENQ<=5;ELSEQ<=0;ENDIF;

WHEN5=>IFDIN=D

(2)THENQ<=6;ELSEQ<=0;ENDIF;

WHEN6=>IFDIN=D

(1)THENQ<=7;ELSEQ<=0;ENDIF;

WHEN7=>IFDIN=D(0)THENQ<=8;ELSEQ<=0;ENDIF;

WHENOTHERS=>Q<=0;

ENDCASE;

ENDIF;

ENDPROCESS;

PROCESS(Q)--检测结果判断输出

BEGIN

IFQ=8THENAB<="1010";--序列数检测正确,输出"A"

ELSEAB<="1011";--序列数检测错误,输出"B"

ENDIF;

ENDPROCESS;

ENDbehav;

时序波形仿真图:

实验分析:

当序列检测器连续收到一组串行二进制码后,如果这组码与检测器中预先设置的码相同,则输出A,否则输出B。

由于这种检测的关键在于正确码的收到必须是连续的,这就要求检测器必须记住前一次的正确码及正确序列,直到在连续的检测中所收到的每一位码都与预置数的对应码相同。

在检测过程中,任何一位不相等都将回到初始状态重新开始检测。

本实验描述的电路完成对序列数"11100101"的检测,当这一串序列数高位在前(左移)串行进入检测器后,若此数与预置的密码数相同,则输出“A”,否则仍然输出“B”。

实验十一:

乐曲硬件演奏电路设计

实验目的:

学习设计硬件乐曲演奏电路。

实验内容:

主系统由三个模块组成,由顶层设计文件,其内部有三个功能模块:

tonetaba.vhd、notetabs.vhd和speakera.vhd。

实验程序:

硬件演奏电路顶层设计:

libraryieee;

useieee.std_logic_1164.all;

entitysongeris

port(clk12mhz:

instd_logic;

clk8hz:

instd_logic;

code1:

outstd_logic_vector(3downto0);

high1:

outstd_logic;

spkout:

outstd_logic);

end;

architectureoneofsongeris

componentnotetabs

port(clk:

instd_logic;

toneindex:

outstd_logic_vector(3downto0));

endcomponent;

componenttonetaba

port(index:

instd_logic_vector(3downto0);

code:

outstd_logic_vector(3downto0);