基于VHDL的多功能调制解调器的设计.docx

《基于VHDL的多功能调制解调器的设计.docx》由会员分享,可在线阅读,更多相关《基于VHDL的多功能调制解调器的设计.docx(22页珍藏版)》请在冰豆网上搜索。

基于VHDL的多功能调制解调器的设计

一、设计功能与要求

调制解调器被人们称为“猫”,它是在发送端通过调制将数字信号转换为模拟信号,而在接收端通过解调再将模拟信号转换为数字信号的一种装置。

这篇报告将通过这学期所学习的VHDL的相关知识设计一个多功能的调制解调器,下面是设计要求:

1、实现二进制振幅键控(2ASK)的调制与解调;

2、实现二进制频移键控(2FSK)的调制与解调;

3、实现二进制相位键控(2PSK)的调制与解调。

二、设计思路

1、2ASK调制与解调

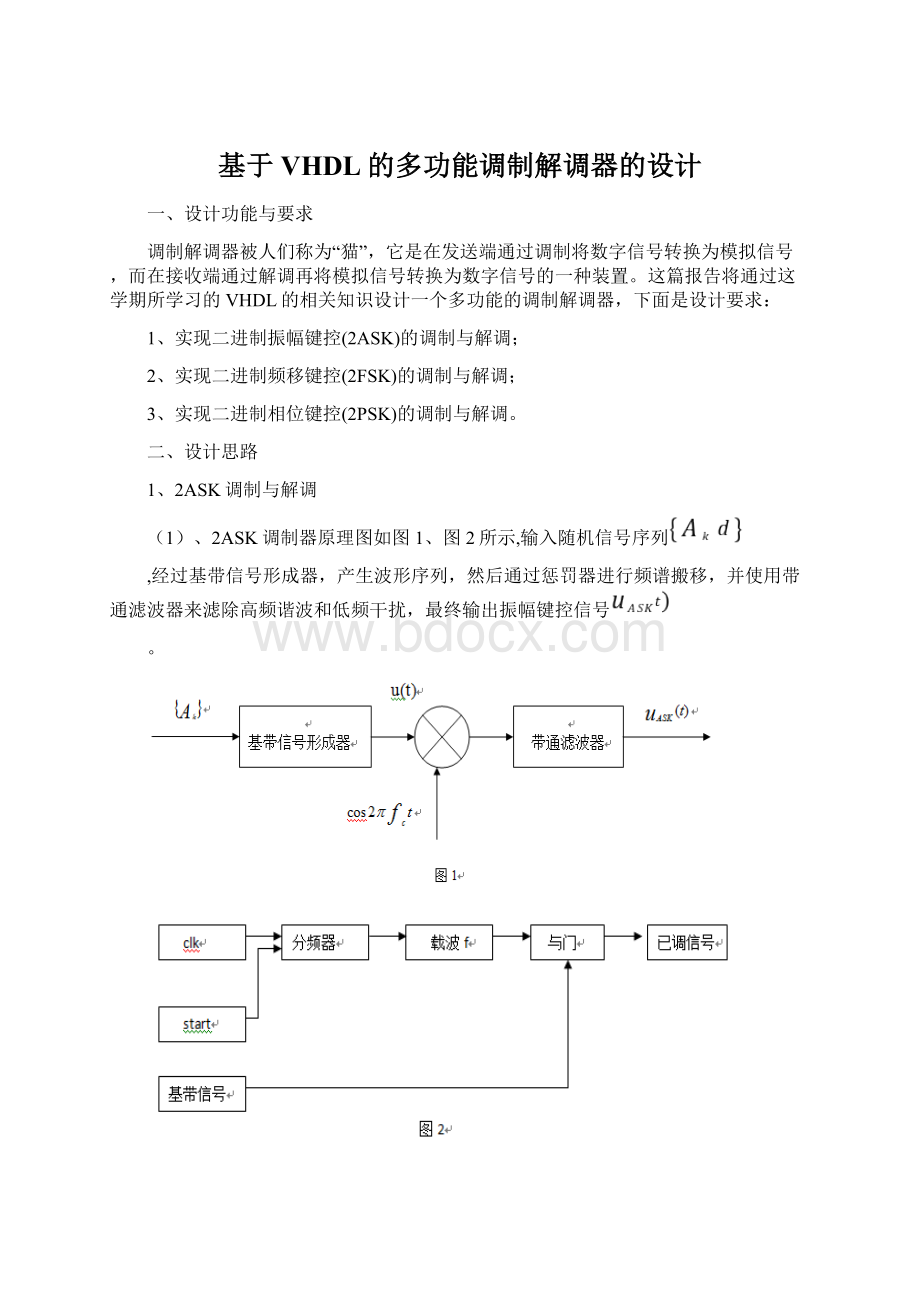

(1)、2ASK调制器原理图如图1、图2所示,输入随机信号序列

经过基带信号形成器,产生波形序列,然后通过惩罚器进行频谱搬移,并使用带通滤波器来滤除高频谐波和低频干扰,最终输出振幅键控信号

。

(2)、2ASK解调器以包络解调为例来说明,原理图如图3所示,其中分频器对时钟信号进行分频得到与发射端数字载波相同的数字载波信号;寄存器在时钟上升沿到来时把数字ASK信号存入寄存器;计数器利用分频输出的载波信号作为计数器的时钟信号,在其上升沿到来时,对寄存器中的ASK载波个数进行计数,当计数值大于3时,输出位1,否则为0;判决器则以数字载波为判决时钟,对计数器输出信号进行抽样判决,并输出解调后的基带信号。

2、2FSK调制与解调

(1)、2FSK调制器的原理图如图4所示,信号通过2个独立的分频器产生不同频率的载波信号,然后通过选通开关选择不同频率的高频信号,从而实现2FSK调制。

(2)、2FSK与2ASK解调相似,也是由分频器、寄存器、计数器和判决器构成,其结构构图如图5所示:

3、2PSK调制与解调

相位键控分为绝对调相(CPSK)与相对调相(DPSK)两种。

CPSK是利用载波的不同相位去直接传送数字信息的一种方式;DPSK则是利用载波相位的相对变化来传送数字信号,即利用前后码之间载波相位的变化表示数字基带信号。

(1)CPSK调制与解调

CPSK调制器结构图如图6所示。

计数器对外部时钟信号进行分频与计数,并输出两路相位不同的数字载波信号;2选1开关在基带信号的控制下,对两路载波信号进行选择,输出信号即为CPSK信号。

CPSK解调器的结构图如图7所示,计数器q输出与发射端同步的0相数字载波;将计数器输出的0相载波与数字CPSK信号中的载波进行与运算,当两比较信号在判决时刻都为1时,输出为1,否则输出为0,从而实现解调。

(2)、DPSK调制与解调

DPSK调制器的结构图如图8所示,CPSK调制器,计数器,异或门和寄存器共同完成绝对码到相对码的变换功能。

DPSK解调器关键则是实现相对码到绝对码的转换,其结构图如图9所示,DPSK解调采用CPSK解调器与相对码到绝对码转换电路即可实现,其中,相对码到绝对码的转换是以在以计数器输出信号为时钟控制下完成的。

三、原理图说明

1、顶层模块的原理图

利用选择译码器输出矢量的每一位分别作为调制解调器的工作使能输入信号,从而实现不同条件下多种调制解调方式间的选择,对于PSK调制与解调以CPSK为例来输入原理图。

2、利用仿真程序生成2ASK调制器的RTL视图及电路符号

3、利用仿真程序生成2ASK解调器的RTL视图及电路图

4、利用仿真程序生成2FSK调制器的RTL视图及电路图

5、利用仿真程序生成2FSK解调器的RTL视图及电路图

6、利用仿真程序生成2CPSK调制器的RTL视图及电路图

7、利用仿真程序生成2CPSK解调器的RTL视图及电路图

8、利用仿真程序生成2DPSK调制器绝对码转换为相对码的RTL视图及电路图

9、利用仿真程序生成2DPSK解调器相对码转换为绝对码的RTL视图及电路图

四、VHDL源代码的实现

1、选择译码器的程序

libraryieee;

useieee.std_logic_1164.all;

entityselecteris

port(

sel:

instd_logic_vector(2downto0);

Q:

outstd_logic_VECTOR(5downto0)

);

endselecter;

architecturertlofselecteris

begin

process(sel)

begin

caseselis

when"000"=>Q<="000001";

when"001"=>Q<="000010";

when"010"=>Q<="000100";

when"011"=>Q<="001000";

when"100"=>Q<="010000";

when"101"=>Q<="100000";

whenothers=>null;

endcase;

endprocess;

endrtl;

2、2ASK调制器的程序

libraryieee;

useieee.std_logic_arith.all;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityPL_ASKis

port(clk:

instd_logic;--系统时钟

start:

instd_logic;--开始调制信号

x:

instd_logic;--基带信号

y:

outstd_logic);--调制信号

endPL_ASK;

architecturebehavofPL_ASKis

signalq:

integerrange0to3;--分频计数器

signalf:

std_logic;--载波信号

begin

process(clk)

begin

ifclk'eventandclk='1'then

ifstart='0'thenq<=0;

elsifq<=1thenf<='1';q<=q+1;--改变q后面数字的大小,就可以改变载波信号的占空比

elsifq=3thenf<='0';q<=0;--改变q后面数字的大小,就可以改变载波信号的频率

elsef<='0';q<=q+1;

endif;

endif;

endprocess;

y<=xandf;--对基带码进行调制

endbehav;

3、2ASK解调器的程序

libraryieee;

useieee.std_logic_arith.all;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityPL_ASK2is

port(clk:

instd_logic;--系统时钟

start:

instd_logic;--同步信号

x:

instd_logic;--调制信号

y:

outstd_logic);--基带信号

endPL_ASK2;

architecturebehavofPL_ASK2is

signalq:

integerrange0to11;--计数器

signalxx:

std_logic;--寄存x信号

signalm:

integerrange0to5;--计xx的脉冲数

begin

process(clk)--对系统时钟进行q分频,

begin

ifclk'eventandclk='1'thenxx<=x;--clk上升沿时,把x信号赋给中间信号xx

ifstart='0'thenq<=0;--if语句完成q的循环计数

elsifq=11thenq<=0;

elseq<=q+1;

endif;

endif;

endprocess;

process(xx,q)--此进程完成ASK解调

begin

ifq=11thenm<=0;--m计数器清零

elsifq=10then

ifm<=3theny<='0';--if语句通过对m大小,来判决y输出的电平

elsey<='1';

endif;

elsifxx'eventandxx='1'thenm<=m+1;--计xx信号的脉冲个数

endif;

endprocess;

endbehav;

4、2FSK调制器的程序

libraryieee;

useieee.std_logic_arith.all;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityPL_FSKis

port(

clk:

instd_logic;--系统时钟

start:

instd_logic;--开始调制信号

x:

instd_logic;--基带信号

y:

outstd_logic--调制信号

);

endPL_FSK;

architecturertlofPL_FSKis

signalq1:

integerrange0to11;--载波信号f1的分频计数器

signalq2:

integerrange0to3;--载波信号f2的分频计数器

signalf1,f2:

std_logic;--载波信号f1,f2

begin

process(clk)--此进程通过对系统时钟clk的分频,得到载波f1

begin

ifclk'eventandclk='1'then

ifstart='0'thenq1<=0;

elsifq1<=5then

f1<='1';

q1<=q1+1;--改变q1后面的数字可以改变载波f1的占空比

elsifq1=11then

f1<='0';

q1<=0;--改变q1后面的数字可以改变载波f1的频率

else

f1<='0';

q1<=q1+1;

endif;

endif;

endprocess;

process(clk)--此进程通过对系统时钟clk的分频,得到载波f2

begin

ifclk'eventandclk='1'then

ifstart='0'thenq2<=0;

elsifq2<=0then

f2<='1';

q2<=q2+1;--改变q2后面的数字可以改变载波f2的占空比

elsifq2<=1then

f2<='0';

q2<=0;--改变q2后面的数字可以改变载波f2的频率

else

f2<='0';

q2<=q2+1;

endif;

endif;

endprocess;

process(clk,x)--此进程完成对基带信号的FSK调制

begin

ifclk'eventandclk='1'then

ifx='0'then

y<=f1;--当输入的基带信号x=’0’时,输出的调制信号y为f1

else

y<=f2;--当输入的基带信号x=’1’时,输出的调制信号y为f2

endif;

endif;

endprocess;

endrtl;

5、2FSK解调器的程序

libraryieee;

useieee.std_logic_arith.all;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityPL_FSK2is

port(

clk:

instd_logic;--系统时钟

start:

instd_logic;--同步信号

x:

instd_logic;--调制信号

y:

outstd_logic--基带信号

);

endPL_FSK2;

architecturebehavofPL_FSK2is

signalq:

integerrange0to11;--分频计数器

signalm:

integerrange0to5;--计数器

signalxx:

std_logic;--寄存器

begin

process(clk)--对系统时钟进行q分频

begin

ifclk'eventandclk='1'then

xx<=x;--在clk信号上升沿时,x信号对中间信号xx赋值

ifstart='0'then

q<=0;--if语句完成Q的循环计数

elsifq=11then

q<=0;

else

q<=q+1;

endif;

endif;

endprocess;

process(q,xx)--此进程完成FSK解调

begin

ifq=11then

m<=0;--m计数器清零

elsifq=10then

ifm<=3then

y<='0';--if语句通过对m大小,来判决y输出的电平

else

y<='1';

endif;

elsifxx'eventandxx='1'then

m<=m+1;

endif;

endprocess;

endbehav;

6、2CPSK调制器的程序

libraryieee;

useieee.std_logic_arith.all;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityPL_CPSKis

port(clk:

instd_logic;--系统时钟

start:

instd_logic;--开始调制信号

x:

instd_logic;--基带信号

y:

outstd_logic);--已调制输出信号

endPL_CPSK;

architecturebehavofPL_CPSKis

signalq:

std_logic_vector(1downto0);--2位计数器

signalf1,f2:

std_logic;--载波信号

begin

process(clk)--此进程主要是产生两重载波信号f1,f2

begin

ifclk'eventandclk='1'then

ifstart='0'thenq<="00";

elsifq<="01"thenf1<='1';f2<='0';q<=q+1;

elsifq="11"thenf1<='0';f2<='1';q<="00";

elsef1<='0';f2<='1';q<=q+1;

endif;

endif;

endprocess;

process(clk,x)--此进程完成对基带信号x的调制

begin

ifclk'eventandclk='1'then--上升沿触发

ifq(0)='1'then

ifx='1'theny<=f1;--基带信号x为‘1’时,输出信号y为f1

elsey<=f2;--基带信号x为‘0’时,输出信号y为f2

endif;

endif;

endif;

endprocess;

endbehav;

7、2CPSK解调器的程序

libraryieee;

useieee.std_logic_arith.all;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityPL_CPSK2is

port(clk:

instd_logic;--系统时钟

start:

instd_logic;--同步信号

x:

instd_logic;--调制信号

y:

outstd_logic);--基带信号

endPL_CPSK2;

architecturebehavofPL_CPSK2is

signalq:

integerrange0to3;

begin

process(clk)--此进程完成对CPSK调制信号的解调

begin

ifclk'eventandclk='1'then

ifstart='0'thenq<=0;

elsifq=0thenq<=q+1;--在q=0时,根据输入信号x的电平来进行判决

ifx='1'theny<='1';

elsey<='0';

endif;

elsifq=3thenq<=0;

elseq<=q+1;

endif;

endif;

endprocess;

endbehav;

8、2DPSK调制器绝对码转换为相对码的程序

libraryieee;

useieee.std_logic_arith.all;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityPL_DPSKis

port(clk:

instd_logic;--系统时钟

start:

instd_logic;--开始转换信号

x:

instd_logic;--绝对码输入信号

y:

outstd_logic);--相对码输出信号

endPL_DPSK;

architecturebehavofPL_DPSKis

signalq:

integerrange0to3;--分频器

signalxx:

std_logic;--中间寄存信号

begin

process(clk,x)--此进程完成绝对码到相对码的转换

begin

ifclk'eventandclk='1'then

ifstart='0'thenq<=0;xx<='0';

elsifq=0thenq<=1;xx<=xxxorx;y<=xxxorx;--输入信号与前一个输出信号进行异或

elsifq=3thenq<=0;

elseq<=q+1;

endif;

endif;

endprocess;

endbehav;

9、2DPSK解调器相对码转换为绝对码的程序

libraryieee;

useieee.std_logic_arith.all;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

entityPL_DPSK2is

port(clk:

instd_logic;--系统时钟

start:

instd_logic;--开始转换信号

x:

instd_logic;--相对码输入信号

y:

outstd_logic);--绝对码输出信号

endPL_DPSK2;

architecturebehavofPL_DPSK2is

signalq:

integerrange0to3;--分频

signalxx:

std_logic;--寄存相对码

begin

process(clk,x)--此进程完成相对码到绝对码的转换

begin

ifclk'eventandclk='1'then

ifstart='0'thenq<=0;

elsifq=0thenq<=1;

elsifq=3thenq<=0;y<=xxxorx;xx<=x;--输入信号x与前一输入信号xx进行异或

elseq<=q+1;

endif;

endif;

endprocess;

endbehav;

五、仿真结果与说明

1、选择译码器的仿真波形如下图所示

对应于不同的输入选择信号,输出信号的特定输出高电平,其余为低电平。

2、2ASK调制器的仿真波形如下图所示

当start信号为高电平时,进行ASK调制;载波信号f通过系统时钟进行4分频获得。

3、2ASK解调器的仿真波形如下图所示

当start信号为高电平时,进行ASK解调;在q=11时,m清零;根据m的大小,进行对输出基带信号y的电平的判决;在q为其他时,m计xx的脉冲数;输出的基带信号y滞后输入的调制信号x十个时钟周期。

4、2FSK调制器的仿真波形如下图所示

当start信号为高电平时,进行FSK调制;载波f1,f2分别是通过对clk信号进行12分频和2分频得到的;基带码长是载波信号f1的两个周期,载波信号f2的六个周期;输出的调制信号则在时间上滞后于载波信号一个时钟周期,滞后于输入时钟脉冲两个周期。

5、2FSK解调器的仿真波形如下图所示

当start信号为高电平时,进行FSK解调;当q=11时,m清零;当q=10时,根据m的大小,进行对输出基带信号y的电平判决;当q为其他值是,计数器m记下xx的脉冲数;输出信号y滞后于输入信号x十个时钟周期。

6、2CPSK调制器的仿真波形如下图所示

当start信号为高电平时,进行CPSK调制;载波信号f1、f2是通过输入时钟脉冲clk分频得到的,且滞后输入时钟一个时钟周期;调制输出信号y滞后载波一个时钟周期,滞后输入时钟两个时钟周期。

7、2CPSK解调器的仿真波形如下图所示

当start信号为高电平时,进行CPSK解调;当q=0时,根据x的电平来进行判决;输出信号y滞后输入信号x一个时钟周期。

8、2DPSK调制器绝对码转换为相对码的仿真波形如下图所示

当q=0时,输出信号y是输入信号x与中间寄存信号xx异或,输出信号y滞后于输入信号x一个时钟周期。

9、2DPSK解调器相对码转换为绝对码的仿真波形如下图所示

当q=3时,输出信号y是信号x与xx的异或;输出信号y滞后于输入信号x一个基带码长即4个输入时钟周期。