计算机组成原理参考试题.docx

《计算机组成原理参考试题.docx》由会员分享,可在线阅读,更多相关《计算机组成原理参考试题.docx(18页珍藏版)》请在冰豆网上搜索。

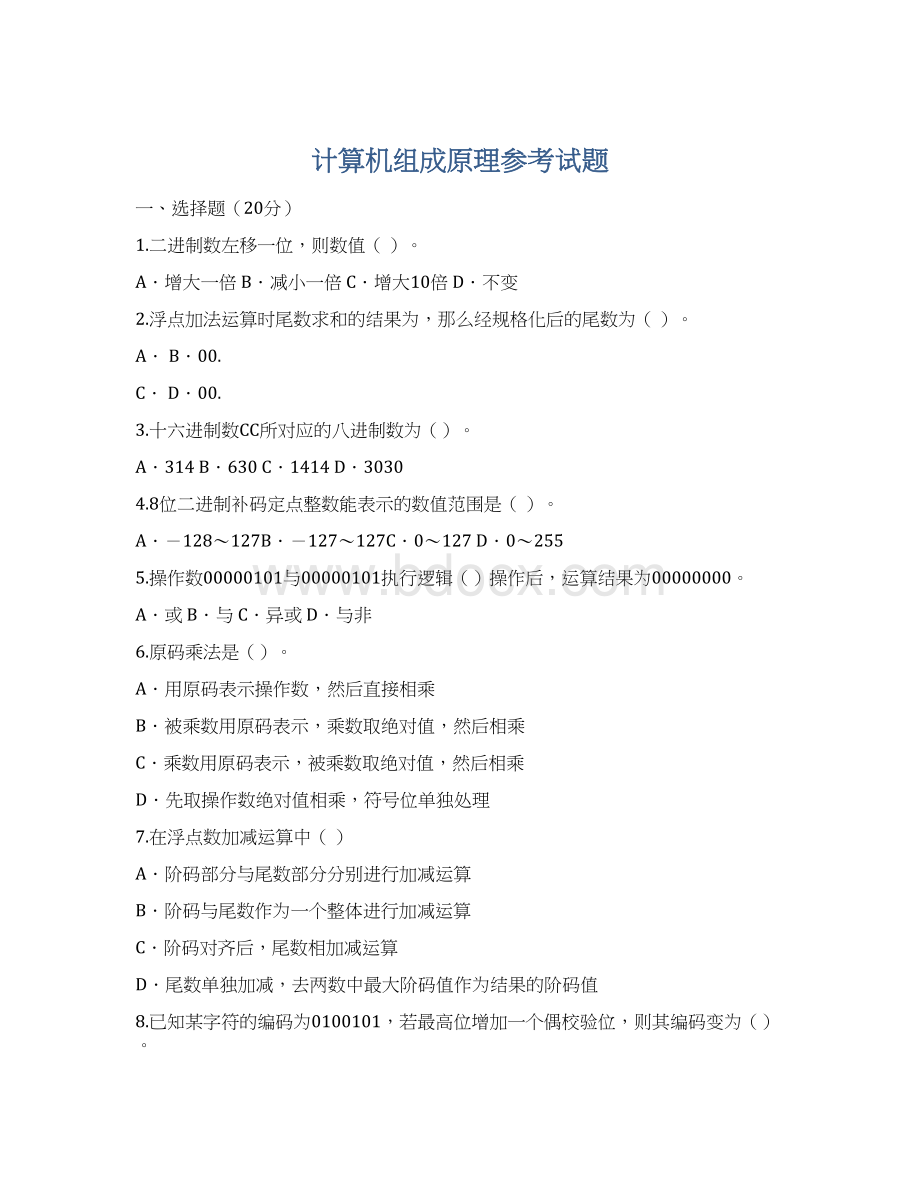

计算机组成原理参考试题

一、选择题(20分)

1.二进制数左移一位,则数值()。

A.增大一倍B.减小一倍C.增大10倍D.不变

2.浮点加法运算时尾数求和的结果为,那么经规格化后的尾数为()。

A.B.00.

C.D.00.

3.十六进制数CC所对应的八进制数为()。

A.314B.630C.1414D.3030

4.8位二进制补码定点整数能表示的数值范围是()。

A.-128~127B.-127~127C.0~127D.0~255

5.操作数00000101与00000101执行逻辑()操作后,运算结果为00000000。

A.或B.与C.异或D.与非

6.原码乘法是()。

A.用原码表示操作数,然后直接相乘

B.被乘数用原码表示,乘数取绝对值,然后相乘

C.乘数用原码表示,被乘数取绝对值,然后相乘

D.先取操作数绝对值相乘,符号位单独处理

7.在浮点数加减运算中()

A.阶码部分与尾数部分分别进行加减运算

B.阶码与尾数作为一个整体进行加减运算

C.阶码对齐后,尾数相加减运算

D.尾数单独加减,去两数中最大阶码值作为结果的阶码值

8.已知某字符的编码为0100101,若最高位增加一个偶校验位,则其编码变为()。

A.B.C.01000110D.01010101

9.计算机各功能部件之间的合作关系如下图所示。

10.

11.假设图中虚线表示控制流,实线表示数据流,那么a、b和c分别表示()。

A.控制器、内存储器和运算器

B.控制器、运算器和内存储器

C.内存储器、运算器和控制器

D.内存储器、控制器和运算器

12.CPU从内存中读取指令时,需要先将程序计数器(PC)的内容输送到()总线上。

A.数据B.地址C.控制D.接口

13.若存储器按字节编址且指令长度为16位,则程序顺序执行时,每执行一条指令,程序计数器的值增加()。

A.1B.2C.3D.4

14.计算机加电自检以后,引导程序首先装入(),否则,计算机不能做任何事情。

A.操作系统B.编译程序

C.Office系列软件D.应用软件

15.外部总线是用来连接()。

A.CPU内部各部件

B.CPU与存储器、I/O系统之间的连线

C.主机系统板上的各个芯片

D.系统中的各个功能模块或设备

16.在指令系统中,采用扩展操作码的目的是()。

A.增加地址码数量B.增加寻址空间

C.增加指令数量D.减少程序中指令操作码的平均长度

17.如果计算机断电,则()中的数据会丢失。

A.ROMB.EPROMC.RAMD.CDROM

18.存储速度最快的是()。

A.CPU内部寄存器B.计算机的高速缓存Cache

C.计算机的内存D.大容量磁盘

19.32位微处理器的32是指()。

A.系统总线的宽度为32位B.处理的数据长度只能为32位

C.CPU字长为32位D.通用寄存器数目为32个

20.()不属于存储器的速度性能指标。

A.存储周期B.存取时间C.主频D.存储器带宽

21.以下关于基址寻址方式的叙述,正确的是()。

A.基址寻址方式常用于解决成批数据的处理

B.基址寻址方式可用于扩大寻址空间

C.基址寄存器主要用于物理地址到逻辑地址的变换

D.基址寄存器可由用户程序修改

22.以科学计算为主的计算机,对()要求较高。

A.外存储器的读写速度B.主机的运算速度

C.I/O设备的速度D.显示分辨率

23.下列指令中属于非数值处理指令的是()。

A.定点运算指令B.浮点运算指令

C.字符串处理指令D.比较两数大小的指令

24.转移指令的主要操作是()。

A.改变程序计数器PC的值

B.改变地址寄存器的值

C.改变PC,并将下一条顺序执行的指令地址(返回指令地址)保存于堆栈中

D.从堆栈中恢复程序计数器PC的值

25.运算器中的累加器()。

A.没有加法器功能,也没有寄存器功能

B.没有加法器功能,有寄存器功能

C.有加法器功能,也有寄存器功能

D.有加法器功能,没有寄存器功能

26.在总线结构的CPU中,各个部件连接到总线上,在某一时间()。

A.只有一个部件可以向总线发送信息,并且只有一个部件能从总线上接收信息。

B.只有一个部件可以向总线发送信息,但可以有多个部件同时从总线上接收信息。

C.可以有一个以上部件向总线发送信息,但只有一个部件可从总线上接收信息。

D.可以有一个以上部件向总线发送信息,并且可以有多个部件同时从总线上接收信息。

27.在微程序控制方式中,机器指令和微指令的关系是()。

A.每一条机器指令由一条微指令来解释执行

B.每一条机器指令由一段(或一个)微程序来解释执行

C.一段机器指令组成的工作程序可由一条微指令来解释执行

D.一条微指令由若干条机器指令组成

28.存储器存储容量单位GB的意义是()。

A.28字节B.210字节C.220字节D.230字节

29.存储器如果按存取方式分类的话,可分为()。

A.CPU控制的存储器和外部设备控制的存储器两类

B.只读存储器和只写存储器两类

C.直接存取存储器和间接存取存储器两类

D.随机存取存储器、只读存储器、顺序存取存储器和直接取存储器

30.在下面几种数据传送的控制方式中,不能实现CPU和输入输出设备并行工作的是()。

A.程序直接控制方式B.程序中断方式

C.DMA输入输出方式D.通道控制方式

31.多体交叉存储器主要解决的问题是()。

A.扩充主存储器容量B.提高存储器的可靠性

C.提高存储器数据传输率D.以上全不对

32.以下关于CPU与主存之间增加高速缓存(Cache)的叙述中,错误的是()。

A.Cache扩充了主存储器的容量

B.Cache可以降低由于CPU与主存之间的速度差异造成的系统性能影响

C.Cache的有效性是利用了对主存储器访问的局部性特性

D.Cache中通常保存着主存储器中部分内容的一份副本

33.虚拟存储器管理系统的基础是程序的局部性原理,因此虚存的目的是为了给每个用户提供比主存容量()编程空间。

A.小得多的逻辑B.大得多的逻辑

C.小得多的物理D.大得多的物理

34.内存的段式存储管理有许多优点。

下面描述中,()不是段式存储管理的优点。

A.支持程序的模块化设计和并行编程的要求

B.各段程序的修改互不影响

C.地址变换速度快、内存碎片(零头)小

D.便于多道程序共享内存的某些段

35.以下叙述正确的是()。

A.主存的存取速度可以与CPU匹配

B.主存由ROM构成

C.辅存中的程序调入主存后才能运行

D.汇编语言程序设计不需要了解计算机的硬件结构

36.与英寸软盘相比,U盘的优点是()。

A.体积小、容量小、速度快B.体积大、容量小、速度慢

C.体积小、容量大、速度慢D.体积小、容量大、速度快

37.在多重中断情况下,CPU现场信息可保存到()。

A.通用寄存器B.控制存储器C.堆栈D.外设接口

38.以下叙述中正确的是()。

A.中断方式一般用于处理随机出现的服务请求

B.外部设备发出中断应立即得到CPU的响应

C.中断方式可用于CPU向外部设备的请求

D.DMA也可用于在主存与主存之间传送数据

39.在直接存储器存取的I/O方式中,控制数据传输的部件是()。

A.CPUB.DMA控制器C.存储器D.总线

40.在外设接口中,状态寄存器的作用是()。

A.存放CPU给外设的操作命令

B.存放外设给CPU的操作信号

C.存放外设的工作状态

D.存放CPU的工作状态

41.若指令系统中设置了专用I/O操作指令,则I/O接口()。

A.与内存单元必须统一编址

B.可以独立编址

C.必须采用DMA方式与内存交换数据

D.必须采用中断方式与内存交换数据

42.并行性的含义不包括()。

A.时间重叠B.资源重复C.资源共享D.数据共用

43.代码10101逻辑右移一位后得()。

A.10010B.10011C.01011D.01010

44.在计算机中,适合于二进制数做加减法运算的数字编码是()。

A.原码B.补码C.BCD码D.ASCII码

45.在()表示中,数值0是唯一表示的。

A.原码B.反码C.补码D.原码和反码

46.若用8位机器码表示二进制数-111,则补码表示的十六进制形式为()。

A.F9B.F0C.89D.80

47.以下底数为2的浮点数表示中,尾数是补码表示,符合规格化要求的是(0<=n<1/2)。

A.×2-4B.×2-4

C.×2-4D.×2-4

48.8个二进制位至多可表示()个数据。

A.8B.64C.255D.256

49.微处理器中的ALU可执行算术运算和()操作

A.浮点B.定点C.逻辑D.控制

50.计算机内数据采用二进制表示是因为二进制数()。

A.最精确B.最容易理解

C.最便于硬件实现D.运算最快

51.若8位二进制数能被4整除,则其最低2位()。

A.不可能是01、00B.只能是10

C.可能是01、00D.只能是00

52.以下关于计算机中数据表示的叙述中,错误的是()。

A.计算机中的数值数据采用二进制表示,非数值性数据不使用二进制表示

B.正整数的原码和补码表示形式相同,而负整数的原码和补码表示形式不同

C.数值中的小数点在硬件中不明确表示,而是采用约定位置的方式

D.码长相同时,补码比原码可以多表示一个数

53.两个带符号的数进行运算时,在()的情况下有可能产生溢出。

A.同符号数相加B.同符号数相减

C.异符号数相加D.异符号数相“或”

54.两个n位数(包括1位符号位)相乘,乘积一般为2n-2位。

一个采用原码一位乘法实现这两个数相乘的运算器,其加法器的位数一般为()。

A.2n位B.2n-2位C.n位D.n+2位

55.在原码一位乘、除法中,求乘积或商的符号的逻辑运算是()。

A.逻辑加B.逻辑乘C.与非运算D.异或运算

56.用ASCII码表示的大写英文字母B﹙42H﹚加偶校验后的二进制编码为(01000010)。

A.B.C.D.01000010

57.状态寄存器保存着算术逻辑运算指令执行(或测试)后形成的各种状态位标志。

这些标志中不包括()。

A.运算结果进位标志B.运算结果错误标志

C.运算结果为零标志D.运算结果溢出标志

58.计算机的用途不同,对其部件的性能指标要求也有所不同。

以科学计算为主的计算机,应该重点考虑()。

A.CPU的主频和字长,以及内存容量

B.硬盘读写速度和字长

C.CPU的主频和显示分辨率

D.硬盘读写速度和显示分辨率

59.主存储器容量大小反映了该计算机()。

A.每秒钟所能执行的指令条数B.存储器读写速度

C.即时存储信息的能力D.保存大量信息的能力

60.在堆栈数据结构及堆栈存储结构的计算机中,所需的操作数默认在堆栈内,因此,入栈和出栈操作常用()。

A.零地址指令格式B.一地址指令格式

C.二地址指令格式D.三地址指令格式

61.在指令系统中,采用扩展操作码的目的是()。

A.增加地址码数量B.增加寻址空间

C.增加指令数量D.减少程序中指令操作码的平均长度

62.与外存储器相比,内部存储器的特点是()。

A.容量大、速度快、成本低B.容量大、速度慢、成本高

C.容量小、速度快、成本高D.容量小、速度慢、成本低

63.CPU执行程序时,为了从内存中读取指令,需要先将()的内容输送到地址总线上。

A.指令寄存