我的数电课程设计.docx

《我的数电课程设计.docx》由会员分享,可在线阅读,更多相关《我的数电课程设计.docx(10页珍藏版)》请在冰豆网上搜索。

我的数电课程设计

题目名称:

数字时钟的设计与制作

姓名:

班级:

学号:

日期:

2011-12-31

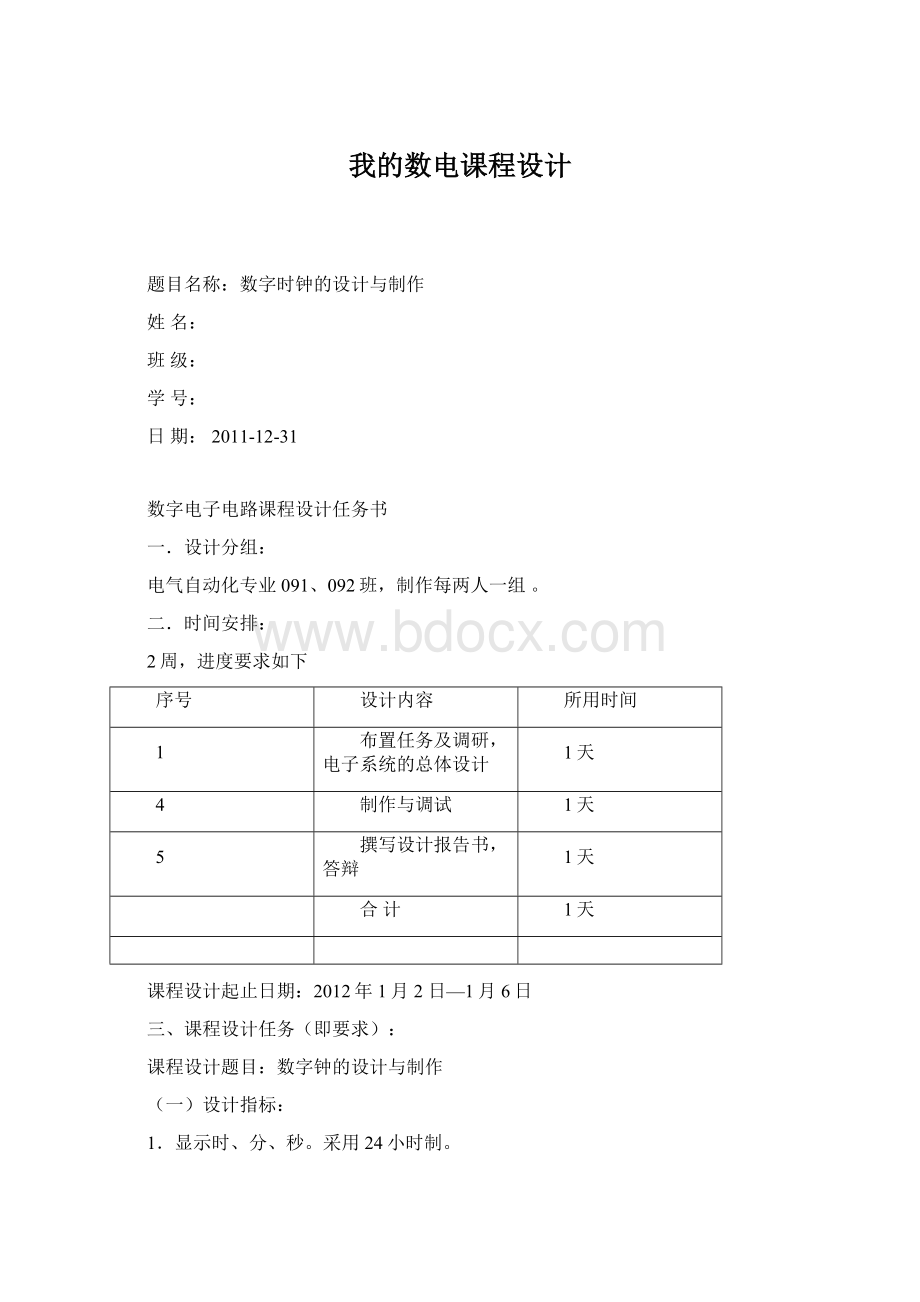

数字电子电路课程设计任务书

一.设计分组:

电气自动化专业091、092班,制作每两人一组。

二.时间安排:

2周,进度要求如下

序号

设计内容

所用时间

1

布置任务及调研,电子系统的总体设计

1天

4

制作与调试

1天

5

撰写设计报告书,答辩

1天

合计

1天

课程设计起止日期:

2012年1月2日—1月6日

三、课程设计任务(即要求):

课程设计题目:

数字钟的设计与制作

(一)设计指标:

1.显示时、分、秒。

采用24小时制。

2.制作、调试出一个具有直流电源、简易信号源及用来计“时”“分”“秒”的数字钟系统。

并按照直流电源、简易信号源、及“秒”、“分”进位和“时”循环进位是否正常给予不同记分。

3.具有校时功能,可以对小时和分单独校时,对分校时的时候,停止分向小时进位。

校时时钟源可以手动输入或借用电路中的时钟。

(二)具体要求:

1.制作、调试数字钟实物;要求焊接、调试出一个具有直流电源、简易信号源及用来计“时”“分”“秒”的数字钟系统。

2.按设计任务书的要求的格式,撰写或打印课程设计报告书。

3.设计总结和答辩。

(三)实验仪器、工具:

1.共阳(共阴)七段数码管/计数器/译码驱动集成电路。

2.导线/电阻/电容/石英晶体/变压器等。

3.示波器、万用表。

四.设计报告要求:

格式要求:

(见附录)

内容要求:

1.画出设计的原理框图,并要求说明该框图的工作过程及每个模块的功能。

2.画出各功能模块的电路图,加以原理说明(如10进制到6进制转换的原理,个位到十位的进位信号选择和变换等)。

3.描述设计制作的数字钟及其运行结果。

说明测试中出现的故障及其排除方法

4.总结:

设计过程中遇到的问题及解决办法;课程设计中的心得体会;对课程设计内容、方式、要求等各方面的建议。

5.附录1:

画出总布局接线图(集成块按实际布局位置画,关键的连接单独应画出,计数器到译码器的数据线、译码器到数码管的数据线可以简化画法,但集成块的引脚须按实际位置画,并注明名称。

)(或附上实物照片)

6.附录2:

元器件清单。

五、课程设计参考资料

1.彭介华主编:

《数字电子电路课程设计指导》,高等教育出版社,2002年出版。

2.郑步生.Multisim2001电路设计及仿真入门与应用.电子工业出版社.2002

3.高吉祥主编.数字电子电路基础实验与课程设计.北京:

电子工业出版社,2002

4.扬志亮.Protel99SE电路原理图设计技术.西北工业大学出版社.2002

5.

6.

2011年12月30日

数字电子电路课程设计说明书

一设计指标:

1.显示时、分、秒。

采用24小时制。

2.制作、调试出一个具有直流电源、简易信号源及用来计“时”“分”“秒”的数字钟系统。

并按照直流电源、简易信号源、及“秒”、“分”进位和“时”循环进位是否正常给予不同记分。

3.具有校时功能,可以对小时和分单独校时,对分校时的时候,停止分向小时进位。

校时时钟源可以手动输入或借用电路中的时钟。

4.制作、调试数字钟实物;要求焊接、调试出一个具有直流电源、简易信号源及用来计“时”“分”“秒”的数字钟系统。

二数字钟的基本原理

数字电子钟由信号发生器、“时、分、秒”计数器、LED数码管、校时电路、整点报时电路等组成。

工作原理为时钟源用以产生稳定的脉冲信号,作为数字种的时间基准,要求震荡频率为1HZ,为标准秒脉冲。

将标准秒脉冲信号送入“秒计数器”,该计数器采用60进制计数器,每累计60秒发出一个“分脉冲”信号,该信号将作为“分计数器”的时钟脉冲。

“分计数器”也采用60进制计数器,每累计60分,发出一个“时脉冲”信号,该信号将被送到“时计数器”。

“时计数器”采用24进制计数器,可以实现24小时的累计。

LED数码管将“时、分、秒”计数器的输出状态显示。

校时电路是来对“时、分、秒”显示数字进行校对调整。

三总体及分布设计

1总体设计方案:

图2-1数字电子钟原理框图

数字电子钟原理如图2-1所示。

一个具有计时、校时、报时、显示等基本功能的数字钟主要由振荡器、分频器、计数器、译码器、显示器、校时电路、报时电路等七部分组成。

石英晶体振荡器产生的信号经过分频器得到秒脉冲,秒脉冲送入计数器计数,计数结果通过“时”、“分”、“秒”译码器译码,并通过显示器显示时间。

2.单元电路设计

CD4511CD4511是一个用于驱动共阴极LED显示器的译码器,具有BCD转换、消隐和锁存控制、七段译码及驱动功能的CMOS电路能提供较大的拉电流,可直接驱动LED显示器

CD4511具有锁存、译码、消隐功能,通常以反相器作输出级,通常用以驱动LED。

各引脚的名称:

其中7、1、2、6分别表示A、B、C、D;5、4、3分别表示LE、BI、LT;13、12、11、10、9、15、14分别表示a、b、c、d、e、f、g。

左边的引脚表示输入,右边表示输出,还有两个引脚8、16分别表示的是VDD、VSS

用CD4511实现LED与单片机的并行接口方法如下图:

CD4511引脚图

74LS161

74LS161是常用的四位二进制可预置的同步加法计数器,他可以灵活的运用在各种数字电路,以及单片机系统种实现分频器等很多重要的功能,:

<74ls161引脚图>管时钟CP和四个数据输入端P0~P3清零/MR使能CEP,CET

置数PE数据输出端Q0~Q3以及进位输出TC.(TC=Q0•Q1•Q2•Q3•CET)

SN74LS247功能

ABCD译码地址输入端/BI,/RBO消隐输入脉冲消隐输入

/LT灯测试输入端/RBI脉冲消隐输入端a---g这些都是低电平有效

2.2.1秒计数电路

秒的个位部分为逢十进一,十位部分为逢六进一,从而共同完成60进制计数器。

当计数到59时清零并重新开始计数。

秒的个位部分的设计:

利用十进制计数器CD40110设计10进制计数器显示秒的个位。

个位计数器由0增加到9时产生进位,连在十位部计数器脉冲输入端CP,从而实现10进制计数和进位功能。

利用74LS161和74LS00设计6进制计数器显示秒的十位,当十位计数器由0增加到5时利用74LS00与门产生一个高电平接到个位、十位的CD4511的清零端,同时产生一个脉冲给分的个位。

2.2.2分计数电路

分的个位部分为逢十进一,十位部分为逢六进一,从而共同完成60进制计数器。

当计数到59时清零并重新开始计数。

秒的个位部分的设计:

来自秒计数电路的进位脉冲使分的个位加1,利用十进制计数器CD4511设计10进制计数器显示秒的个位。

个位计数器由0增加到9时产生进位,连在十位部计数器脉冲输入端CP,从而实现10进制计数和进位功能。

利用74LS161和74L00设计6进制计数器显示秒的十位,当十位计数器由0增加到5时利用74LS00与门产生一个高电平接到个位、十位的CD4511的清零端,同时产生一个脉冲给时的个位。

60进制--分计数电路

2.2.3时计数电路

来自分计数电路的进位脉冲使时的个位加,个位计数器由0增加到9是产生进位,连在十位计数器脉冲输入端CP,当十位计到2且个位计到3是经过74LS00与门产生一个清零信号,将所有CD4511清零。

24进制--时计数电路

2.2.4显示电路

由CD40110产生十进制数字,再由数码管显示出来。

这里的LED数码管是采用共阴连接的。

3总体设计图

三.制作调试:

连接注意事项:

1不能短路,防止虚焊,焊为小锥形状,所以芯片都要接电源和地

2因为用的是CD4511所以CD45115角接低电平

3数码管的3和8和5接低电平,3和8接低的原因是因为是共阴极(发现3和8焊一个角也可以,因为他们是连在一起的),而5接低电平原因是因为不让数码管的小数点亮,因为是整数进位,没有小数

4右边四个与非门是一个74LS00,左边两个与非门是一个74LS00

5六个非门用一个74ALS04

6最左边放电源(地)最右边放地(电源)

7图的最下面两个74LS74和CD4060B不接,在数字电路课程设计电路板上.

8布线要合理否则最后板子焊接失败

9.电阻在连接的时候最后选在一条通路上,这样就可以减少很多焊点。

四.总结:

通过本次实验,我对数电的计数器部分的知识有了更深的了解,明白了学习电子技术基础的意义。

在课程设计中,我们小组也遇到了很多挫折,不过我们经过各种调试,最终解决了小毛病,这个过程每一个环节无不提现团队合作的重要性。

。

。

。

。

。

。

。

。

。

。

。

。

。

。

。

五.参考文献

参考文献:

[1]彭介华.数字电子电路课程设计指导.北京:

高等教育出版社,2002.

[2]康华光.数字电子电路基础-数字部分.北京:

高等教育出版社,2002.

[3]

[4]

成果附图: