soc实验报告.docx

《soc实验报告.docx》由会员分享,可在线阅读,更多相关《soc实验报告.docx(67页珍藏版)》请在冰豆网上搜索。

soc实验报告

《SOC微体系结构设计》

班级:

031011

学号:

0310100703101017

姓名:

张志红刘剑

实验一8位串行全加器设计

一.实验目的

1.掌握ISE开发工具的使用,掌握FPGA开发的基本步骤;

2.掌握8位串行全加器电路设计的一般办法;

3.掌握程序下载的办法;

4.初步了解开发板资源,掌握开发板的使用方法,重点掌握按键,开关,LCD,LED的使用方法。

二.实验内容

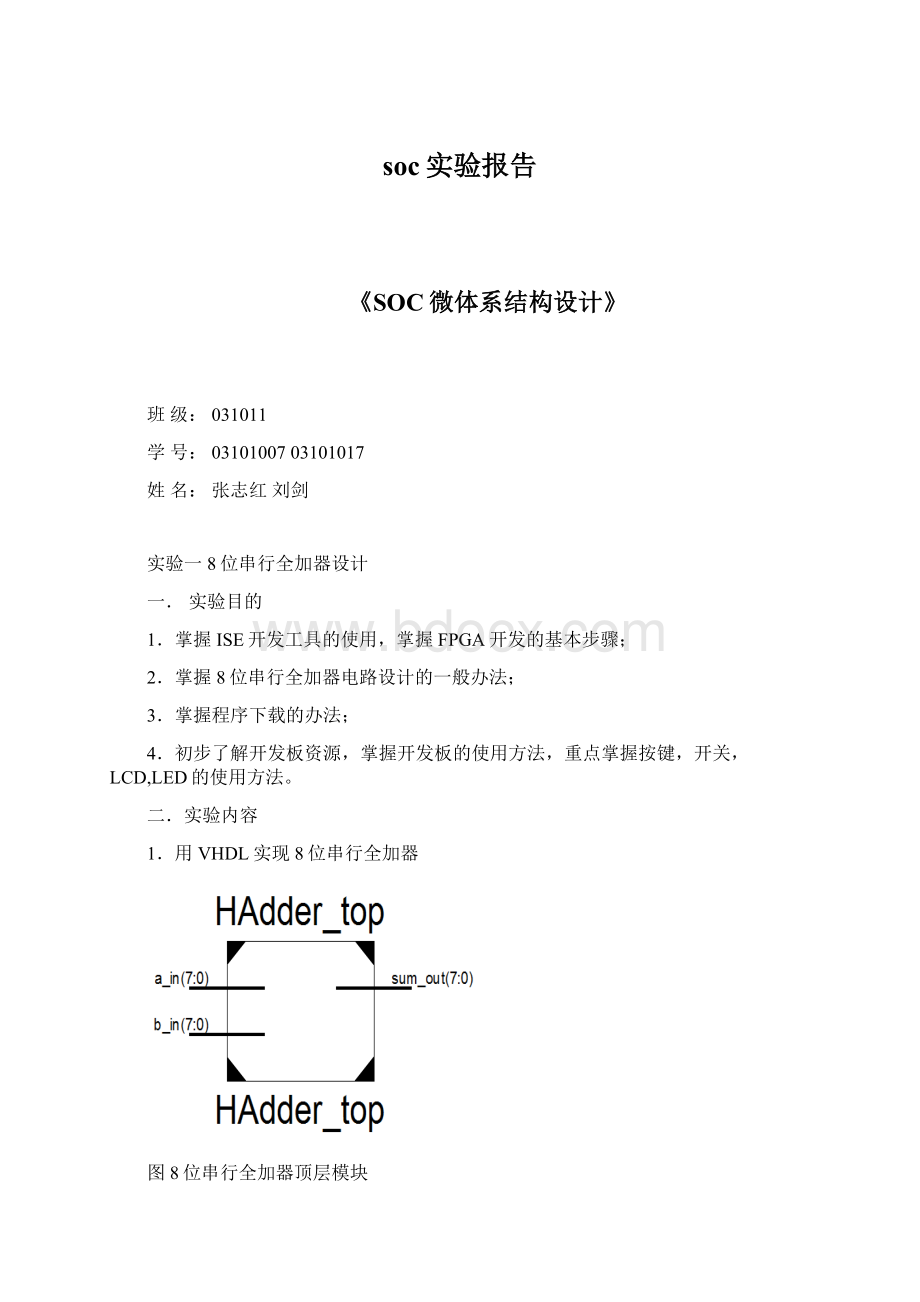

1.用VHDL实现8位串行全加器

图8位串行全加器顶层模块

中a_in,b_in:

数据输入,使用板上开关(S0~S15);sum_out:

运算结果输出,使用LED显示运算结果。

2.将程序下载到FPGA并进行检验资源使用要求,用开关(S0~S15)输入加数,被加数用LED(D8~D15)显示运算结果。

三.实验步骤

1.启动ISE,新建工程文件;

2.编写8位串行全加器模块Hadder,其原理图如上图所示。

3.编写完加法器模块之后,在顶层文件上实现映射;

4.新建UCF文件,输入位置约束;

5.完成综合,实现,生成下载文件;

6.连接开发板USB下载线,开启开发板电源;

7.下载FPGA;

8.输入数据,验证结果。

四.关键代码

entityadd_oneis---一位加

Port(a_in:

inSTD_LOGIC;

b_in:

inSTD_LOGIC;

cin:

inSTD_LOGIC;

si:

outSTD_LOGIC;

cout:

outSTD_LOGIC);

endadd_one;

architectureBehavioralofadd_oneis

begin

si<=(a_inxorb_in)xorcin;

cout<=(a_inandb_in)or(cinanda_in)or(cinandb_in);

endBehavioral;

entityadd_eightis---八位加

Port(a:

inSTD_LOGIC_VECTOR(7downto0);

b:

inSTD_LOGIC_VECTOR(7downto0);

sum:

outSTD_LOGIC_VECTOR(7downto0);

c_out:

outSTD_LOGIC);

endadd_eight;

architectureBehavioralofadd_eightis

componentadd_one

port(a_in,b_in,cin:

inSTD_LOGIC;

si,cout:

outSTD_LOGIC);

endcomponent;

signalc:

STD_LOGIC_VECTOR(7downto0);

signalc_in:

STD_LOGIC:

='0';

begin

u0:

add_oneportmap(a(0),b(0),c_in,sum(0),c(0));

u1:

add_oneportmap(a

(1),b

(1),c(0),sum

(1),c

(1));

u2:

add_oneportmap(a

(2),b

(2),c

(1),sum

(2),c

(2));

u3:

add_oneportmap(a(3),b(3),c

(2),sum(3),c(3));

u4:

add_oneportmap(a(4),b(4),c(3),sum(4),c(4));

u5:

add_oneportmap(a(5),b(5),c(4),sum(5),c(5));

u6:

add_oneportmap(a(6),b(6),c(5),sum(6),c(6));

u7:

add_oneportmap(a(7),b(7),c(6),sum(7),c_out);

endBehavioral;

实验二8位并行全加器设计

一.实验目的

1.掌握ISE开发工具的使用,掌握FPGA开发的基本步骤;

2.2.掌握4位并行全加器电路设计的一般办法;

3.掌握程序下载的办法;

4.初步了解开发板资源,掌握开发板的使用方法,重点掌握按键,开关,LCD,LED的使用方法。

二.实验内容

1.用VHDL实现4位并行全加器

图14位全加器顶层模块

其中,a_in,b_in:

输入4位加数和被加数。

sel_in:

数码管片选端;c_in,c_out:

进位输入,进位输出;sum_out:

运算结果的输出。

2.将程序下载到FPGA并进行检验资源使用,要求用开关(s0~s7)输入加数,被加数,(s8~s11)控制用哪个数码管显示数据,s12用于进位输入。

用D8显示结果进位。

三.实验步骤

1.启动ISE,新建工程文件;

2.编写4位并行全加器模块ParAdder,其原理图如上图。

要求:

4位全加器采用并行进位算法。

3.编写完加法器模块之后,在顶层文件上实现映射;

4.新建UCF文件,输入位置约束;

5.完成综合,实现,生成下载文件;

6.连接开发板USB下载线,开启开发板电源;

7.下载FPGA;

8.输入数据,验证结果。

四.关键代码

entityaddis

Port(a:

inSTD_LOGIC_VECTOR(7downto0);

b:

inSTD_LOGIC_VECTOR(7downto0);

cin:

inSTD_LOGIC;

s:

outSTD_LOGIC_VECTOR(7downto0);

cout:

outSTD_LOGIC);

endadd;

architectureBehavioralofaddis

signalc:

STD_LOGIC_VECTOR(7downto0);

signalp,g:

STD_LOGIC_VECTOR(7downto0);

begin

g(0)<=a(0)andb(0);

g

(1)<=a

(1)andb

(1);

g

(2)<=a

(2)andb

(2);

g(3)<=a(3)andb(3);

g(4)<=a(4)andb(4);

g(5)<=a(5)andb(5);

g(6)<=a(6)andb(6);

g(7)<=a(7)andb(7);

p(0)<=a(0)xorb(0);

p

(1)<=a

(1)xorb

(1);

p

(2)<=a

(2)xorb

(2);

p(3)<=a(3)xorb(3);

p(4)<=a(4)xorb(4);

p(5)<=a(5)xorb(5);

p(6)<=a(6)xorb(6);

p(7)<=a(7)xorb(7);

c

(1)<=g(0)or(p(0)andcin);

c

(2)<=g

(1)or(p

(1)andg(0))or(p

(1)andp(0)andcin);

c(3)<=g

(2)or(p

(2)andg

(1))or(p

(2)andp

(2)andg(0))or(p

(2)andp

(1)andp(0)andcin);

c(4)<=g(3)or(p(3)andg

(2))or(p(3)andp

(2)andg

(1))or(p(3)andp

(2)andp

(1)andg(0))

or(p(3)andp

(2)andp

(1)andp(0)andcin);

c(5)<=g(4)or(p(4)andg(3))or(p(4)andp(3)andg

(2))or(p(4)andp(3)andp

(2)andg

(1))

or(p(4)andp(3)andp

(2)andp

(1)andg(0))or(p(4)andp(3)andp

(2)andp

(1)andp(0)andcin);

c(6)<=g(5)or(p(5)andg(4))or(p(5)andp(4)andg(3))or(p(5)andp(4)andp(3)andg

(2))

or(p(5)andp(4)andp(3)andp

(2)andg

(1))or(p(5)andp(4)andp(3)andp

(2)andp

(1)andg(0))

or(p(5)andp(4)andp(3)andp

(2)andp

(1)andp(0)andcin);

c(7)<=g(6)or(p(6)andg(5))or(p(6)andp(5)andg(4))or(p(6)andp(5)andp(4)andg(3))

or(p(6)andp(5)andp(4)andp(3)andg

(2))or(p(6)andp(5)andp(4)andp(3)andp

(2)andg

(1))

or(p(6)andp(5)andp(4)andp(3)andp

(2)andp

(1)andg(0))or(p(6)andp(5)andp(4)andp(3)andp

(2)andp

(1)andp(0)andcin);

cout<=g(7)or(p(7)andg(6))or(p(7)andp(6)andg(4))or(p(7)andp(6)andp(5)andg(4))

or(p(7)andp(6)andp(5)andp(4)andg(3))or(p(7)andp(6)andp(5)andp(4)andp(3)andg

(2))

or(p(7)andp(6)andp(5)andp(4)andp(3)andp

(2)andg

(1))or(p(7)andp(6)andp(5)andp(4)andp(3)andp

(2)andp

(1)andg(0))

or(p(7)andp(6)andp(5)andp(4)andp(3)andp

(2)andp

(1)andp(0)andcin);

s(0)<=p(0)xorcin;

s

(1)<=p

(1)xorc

(1);

s

(2)<=p

(2)xorc

(2);

s(3)<=p(3)xorc(3);

s(4)<=p(4)xorc(4);

s(5)<=p(5)xorc(5);

s(6)<=p(6)xorc(6);

s(7)<=p(7)xorc(7);

endBehavioral;

实验三数码管显示程序设计

一.实验目的

1.掌握ISE开发工具的使用,掌握FPGA开发的基本步骤;

2.掌握数码管扫描显示的基本原理和设计方法;

3.掌握ISE仿真调试的基本方法;

二.实验内容

1.用VHDL实现16个七段数码管扫描显示模块

七段数码管扫描显示模块电路如图1.1到图1.3所示所示,主要包括顶层的测试模块,数码管扫描显示模块,以及输入数据向七段数码管进行译码的模块。

使用VHDL实现由扩展板上的拨码开关输入显示数值,在16个数码管的扫描显示功能,并使