北京理工大学数字系统设计与实验报告.pdf

《北京理工大学数字系统设计与实验报告.pdf》由会员分享,可在线阅读,更多相关《北京理工大学数字系统设计与实验报告.pdf(19页珍藏版)》请在冰豆网上搜索。

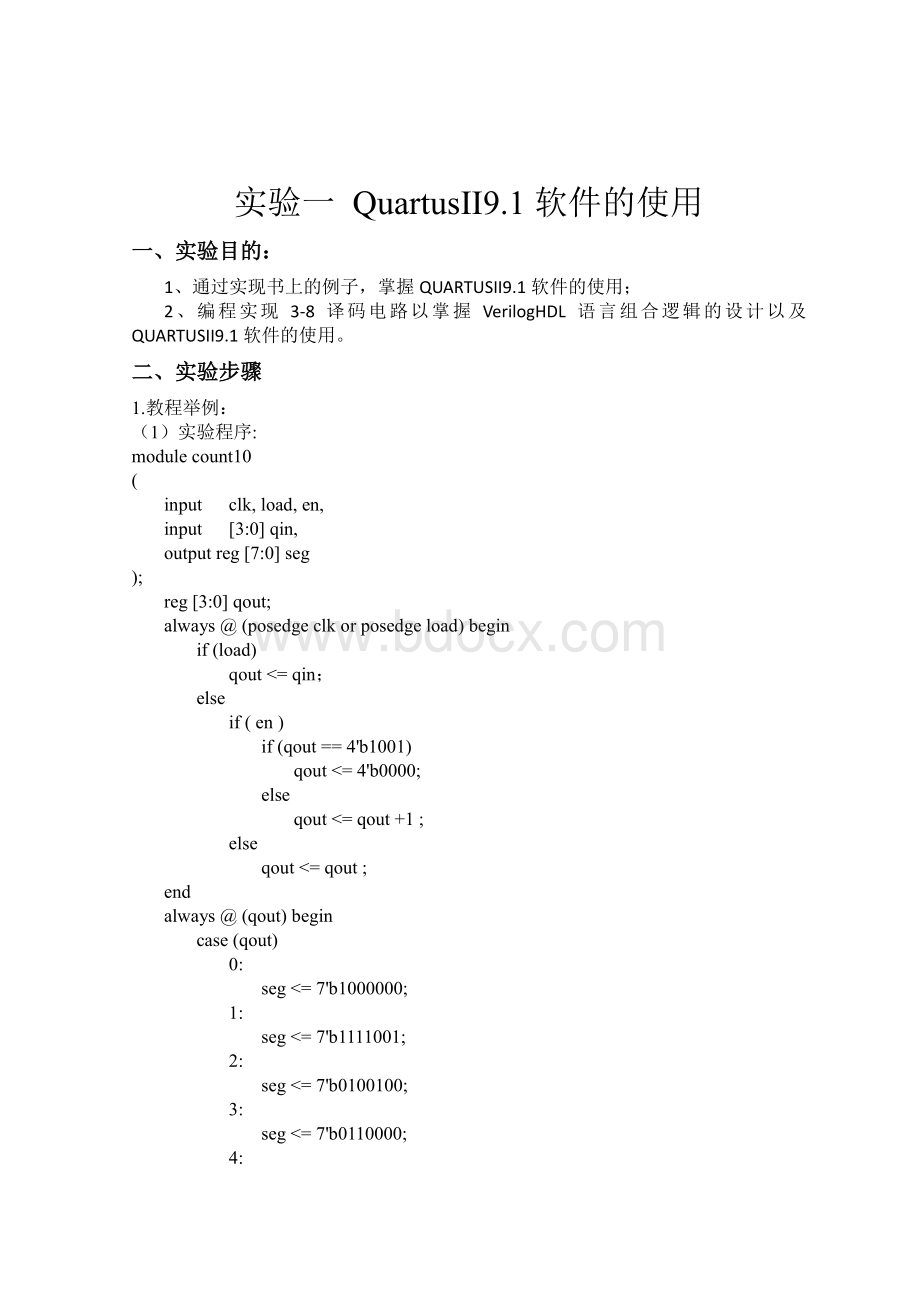

实验一QuartusII9.1软件的使用一、一、实验目的:

实验目的:

1、通过实现书上的例子,掌握QUARTUSII9.1软件的使用;2、编程实现3-8译码电路以掌握VerilogHDL语言组合逻辑的设计以及QUARTUSII9.1软件的使用。

二、二、实验步骤实验步骤1.教程举例:

(1)实验程序:

modulecount10(inputclk,load,en,input3:

0qin,outputreg7:

0seg);reg3:

0qout;always(posedgeclkorposedgeload)beginif(load)qout=qin;elseif(en)if(qout=4b1001)qout=4b0000;elseqout=qout+1;elseqout=qout;endalways(qout)begincase(qout)0:

seg=7b1000000;1:

seg=7b1111001;2:

seg=7b0100100;3:

seg=7b0110000;4:

seg=7b0011001;5:

seg=7b0010010;6:

seg=7b0000010;7:

seg=7b1111000;8:

seg=7b0000000;9:

seg=7b0010000;default:

segNew,淡出对话框后选择VerilogHDLFile,然后进行编写代码。

(二)全编译与功能仿真1、对VerilogHDLFile编译:

从菜单栏中选择ProcessingStartStartAnalysis&Synthesis,选取菜单中ProcessingStartCompilation进行全编译。

2、指定功能仿真模式选择菜单中Assignmentssettings或快捷按钮3、通过建立波形文件进行仿真在QuartusII主界面菜单栏中选择FileNew,在OtherFiles页选中VectorWaveformFile项,如图所示。

点击OK按钮打开空白波形编辑窗口,其默认文件名为“Waveforml.vwf”。

选择菜单栏中EditInsertNodeorBus,选择其中的nodefinder再点击弹出窗口中的List按钮在左侧NodesFound窗口中选取clk、qout、data_in、en、load、seg,然后点击按钮将选中信号选取至右侧SelectedNodes窗口中,最后点击OK回到插入节点窗口运行菜单ProcessingGenerateFunctionalSimulationNetlist命令产生用于功能仿真的网表文件。

选取ProcessingStartSimulation或快捷按钮执行模拟仿真(三)时序仿真选择菜单中Assignmentssettings或快捷按钮,在左侧Category栏中选中SimulatorSettings,然后在右侧Simulationmode的下拉菜栏中选中Timing,确定。

然后点击ProcessingStartSimulation或快捷按钮执行模拟仿真功能仿真设置:

功能仿真结果:

时序仿真设置:

时序仿真结果:

2、38译码器

(1)设计思路随着时钟信号clk上升沿的到来,输入D2D1D0从000加到111,每个输入D2D1D0对应着一个输出Q7Q6Q5Q4Q3Q2Q1Q0,对应关系如真值表所示:

输入输出D2D1D0Q7Q6Q5Q4Q3Q2Q1Q000000000001001000000100100000010001100001000100000100001010010000011001000000111100000003-8译码器真值表如果输入错误,则输出Q7Q6Q5Q4Q3Q2Q1Q0=11111111。

(2)实验代码moduleym3_8(inputclk,outputreg7:

0Q);reg2:

0D;always(posedgeclk)beginD=D+1;endalways(D)begincase(D)0:

Q=8b00000001;1:

Q=8b00000010;2:

Q=8b00000100;3:

Q=8b00001000;4:

Q=8b00010000;5:

Q=8b00100000;6:

Q=8b01000000;7:

Q=8b10000000;default:

Q2-5-6-1-9-4-8-7-3-0的顺序输出;使用此输出作为驱动输入到7段译码器的显示逻辑。

三、三、设计与实现设计与实现1、设计思路

(1)、时钟信号clk作为分频器的输入,分频器的设计思路为设计一个模十六计数器,cp0(Q0)输出即为二分频信号,cp1(Q1)输出即为四分频信号,cp2(Q2)输出即为八分频信号,cp3(Q3)输出即为十六分频信号。

分频器的输出由4选1多路选择器的选择输入端select选择2分频、4分频、8分频和16分频其中之一作为状态机的时钟输入,当select为0时,输出为二分频信号;为1时,输出为四分频信号;为2时,输出为八分频信号;为3时,输出为十六分频信号。

(2)、reset为高有效,则若reset信号为1时,qout置为0,则now_state为0。

若reset信号为0时,qout自加,并作为状态机的输入驱动,让状态机按照0-2-5-6-1-9-4-8-7-3-0的顺序输出。

(3)、状态机按照0-2-5-6-1-9-4-8-7-3-0的顺序输出,并使用此输出作为驱动输入到7段译码器的显示逻辑。

2、实验代码modulecountten(input1:

0select,inputclk,reset,outputreg3:

0cp,outputreg6:

0seg,outputregfp,outputreg9:

0now_state);reg3:

0qout;always(posedgeclkorposedgereset)beginif(reset)cp=0;elsecp=cp+1;endalways(select)case(select)0:

fp=cp0;1:

fp=cp1;2:

fp=cp2;3:

fp=cp3;default:

fp=0;endcasealways(posedgefporposedgereset)beginif(reset)qout=0;elseif(qout=4b1001)qout=4b0000;elseqout=qout+1;endalways(qout)case(qout)0:

now_state=10b0000000001;1:

now_state=10b0000000100;2:

now_state=10b0000100000;3:

now_state=10b0001000000;4:

now_state=10b0000000010;5:

now_state=10b1000000000;6:

now_state=10b0000010000;7:

now_state=10b0100000000;8:

now_state=10b0010000000;9:

now_state=10b0000001000;default:

now_state=10b1111111111;endcasealways(qout)case(qout)0:

seg=7b1000000;1:

seg=7b0100100;2:

seg=7b0010010;3:

seg=7b0000010;4:

seg=7b1111001;5:

seg=7b0010000;6:

seg=7b0011001;7:

seg=7b0000000;8:

seg=7b1111000;9:

seg=7b0110000;default:

seg=7b1111111;endcaseendmodule3、仿真结果功能仿真设置:

功能仿真结果:

(1)总体仿真结果

(2)reset高有效和二分频仿真结果(3)四分频仿真结果(4)八分频仿真结果(5)十六分频仿真结果四、实验心得四、实验心得通过本次实验,设计频率可选的模十状态机以及7段译码电路,学会了以代码形式实现频率多路选择器的功能,巩固了模十状态机的实现方式,进一步掌握VerilogHDL硬件描述语言。

实验三数字钟的设计与仿真一、一、实验目的:

实验目的:

通过设计实现的数字钟的设计与仿真,以熟悉VerilogHDL语言编程。

二、二、实验流程:

实验流程:

输入引脚有3+16根,其中三位分别为时钟(提供整个系统的时钟信号)、复位(系统复位信号)和置位信号(用于将时间设置到需要观察的位置)。

十六位分别为分钟个位和十位、秒个位和十位。

输出引脚有16根,分别位分钟个位和十位、秒个位和十位。

三、设计与实现三、设计与实现1、设计思路与分析:

本实验设计数字钟的实质为设计60*60的计数器。

数字钟为上升沿触发,三个输入管脚为提供整个系统的时钟信号clk,系统复位信号clr(高有效)和置位信号load(高有效),复位信号clr用于将输出的分钟个位min_l、十位min_h和秒个位sec_l、十位sec_h清0,置位信号load将输出的分钟个位min_l、十位min_h和秒个位sec_l、十位sec_h设置到需要观察的位置。

十六位分别为分钟个位min_l0、十位min_h0和秒个位sec_l0、十位sec_h0,为load信号变为高电平时的预置信号,此时输出结果为预置信号。

在load=0,clr=0时,随着clk的上升沿到来,秒个位sec_l进行自加,加到9时下一个clk上升沿到来时秒个位sec_l变为0,sec_h加1。

当时钟为59秒是,下一个clk上升沿到来时,秒清0,分钟低位min_l加1。

当时钟为9分59秒时,下一个clk上升沿到来时,分钟低位min_l,秒高位sec_h,秒低位sec_l清0,分钟高位min_h加1。

当时钟为59分59秒是,下一个clk上升沿到来时,分钟个位min_l、十位min_h和秒个位sec_l、十位sec_h均清0。

2、实验代码moduleclock(inputclk,clr,load,input3:

0min_h0,input3:

0min_l0,input3:

0sec_h0,input3:

0sec_l0,outputreg3:

0min_h,outputreg3:

0min_l,outputreg3:

0sec_h,outputreg3:

0sec_l);always(posedgeclrorposedgeclk)beginif(clr)beginmin_h=0;min_l=0;sec_h=0;sec_l=0;endelseif(load)beginmin_h=min_h0;min_l=min_l0;sec_h=sec_h0;sec_l=sec_l0;endelsebeginif(sec_l=9)beginsec_l=0;if(sec_h=5)beginsec_h=0;if(min_l=9)beginmin_l=0;if(min_h=5)beginmin_h=0;endelsebeginmin_h=min_h+1;endendelsebeginmin_l=min_l+1;endendelse