《EDA技术实用教程(第四版)》题答案.doc

《《EDA技术实用教程(第四版)》题答案.doc》由会员分享,可在线阅读,更多相关《《EDA技术实用教程(第四版)》题答案.doc(29页珍藏版)》请在冰豆网上搜索。

《EDA技术实用教程<第四版>》习题

1习题

1-1EDA技术与ASIC设计和FPGA开发有什么关系?

FPGA在ASIC设计中有什么用途?

P3~4

1-2与软件描述语言相比,VHDL有什么特点?

P6

l-3什么是综合?

有哪些类型?

综合在电子设计自动化中的地位是什么?

P5

1-4在EDA技术中,自顶向下的设计方法的重要意义是什么?

P7~10

1-5IP在EDA技术的应用和发展中的意义是什么?

P22~14

1-6叙述EDA的FPGA/CPLD设计流程,以与涉与的EDA工具与其在整个流程中的作用.

2习题

2-1OLMC〔输出逻辑宏单元〕有何功能?

说明GAL是怎样实现可编程组合电路与时序电路的.P34~36

2-2什么是基于乘积项的可编程逻辑结构?

P33~34,40什么是基于查找表的可编程逻辑结构?

P40~41

2-3FPGA系列器件中的LAB有何作用?

P43~45

2-5解释编程与配置这两个概念.P58

2-6请参阅相关资料,并回答问题:

按本章给出的归类方式,将基于乘积项的可编程逻辑结构的PLD器件归类为CPLD;将基于查找表的可编程逻辑结构的PLD器什归类为FPGA,那么,APEX系列属于什么类型PLD器件?

MAXII系列又属于什么类型的PLD器件?

为什么?

P54~56

3习题

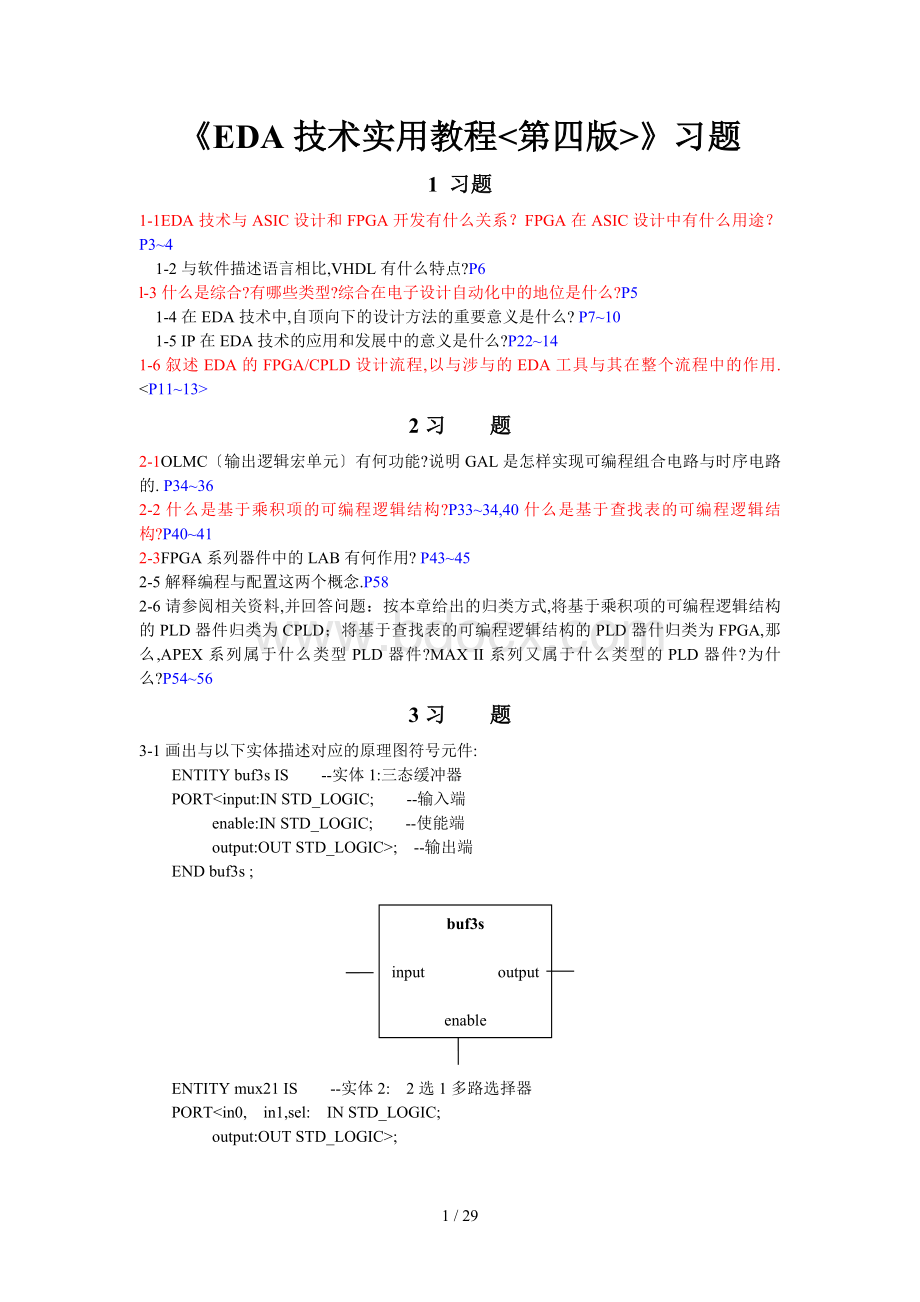

3-1画出与以下实体描述对应的原理图符号元件:

ENTITYbuf3sIS--实体1:

三态缓冲器

PORTINSTD_LOGIC;--输入端

enable:

INSTD_LOGIC;--使能端

output:

OUTSTD_LOGIC>;--输出端

ENDbuf3s;

buf3s

inputoutput

enable

ENTITYmux21IS--实体2:

2选1多路选择器

PORTINSTD_LOGIC;

output:

OUTSTD_LOGIC>;

mux21

in0

output

in1

sel

3-2图3-16所示的是4选1多路选择器,试分别用IF_THEN语句和CASE语句的表达方式写出此电路的VHDL程序,选择控制信号s1和s0的数据类型为STD_LOGIC_VECTOR;当s1=’0’,s0=’0’;s1=’0’,s0=’1’;s1=’1’,s0=’0’和s1=’1’,s0=’1’时,分别执行y<=a、y<=b、y<=c、y<=d.

图3-164选1多路选择器

--解1:

用IF_THEN语句实现4选1多路选择器

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYmux41IS

PORTINSTD_LOGIC;

s0:

INSTD_LOGIC;

s1:

INSTD_LOGIC;

y:

OUTSTD_LOGIC>;

ENDENTITYmux41;

ARCHITECTUREif_mux41OFmux41IS

SIGNALs0s1:

STD_LOGIC_VECTOR<1DOWNTO0>;--定义标准逻辑位矢量数据

BEGIN

s0s1<=s1&s0;--s1相并s0,即s1与s0并置操作

PROCESS

BEGIN

IFs0s1="00"THENy<=a;

ELSIFs0s1="01"THENy<=b;

ELSIFs0s1="10"THENy<=c;

ELSEy<=d;

ENDIF;

ENDPROCESS;

ENDARCHITECTUREif_mux41;

--解2:

用CASE语句实现4选1多路选择器

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYmux41IS

PORTINSTD_LOGIC;

s0:

INSTD_LOGIC;

s1:

INSTD_LOGIC;

y:

OUTSTD_LOGIC>;

ENDENTITYmux41;

ARCHITECTUREcase_mux41OFmux41IS

SIGNALs0s1:

STD_LOGIC_VECTOR<1DOWNTO0>;--定义标准逻辑位矢量数据类型

BEGIN

s0s1<=s1&s0;--s1相并s0,即s1与s0并置操作

PROCESS

BEGIN

CASEs0s1IS--类似于真值表的case语句

WHEN"00"=>y<=a;

WHEN"01"=>y<=b;

WHEN"10"=>y<=c;

WHEN"11"=>y<=d;

WHENOTHERS=>NULL;

ENDCASE;

ENDPROCESS;

ENDARCHITECTUREcase_mux41;

3-3图3-17所示的是双2选1多路选择器构成的电路MUXK,对于其中MUX21A,当s=’0’和s=’1’时,分别有y<=‘a’和y<=’b’.试在一个结构体中用两个进程来表达此电路,每个进程中用CASE语句描述一个2选1多路选择器MUX21A.

图3-17含2选1多路选择器的模块

--解:

用CASE语句实现图4-18所示的是双2选1多路选择器构成的电路

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYmux31IS

PORTINSTD_LOGIC;

outy:

OUTSTD_LOGIC>;

ENDENTITYmux31;

ARCHITECTUREcase_mux31OFmux31IS

SIGNALy:

STD_LOGIC;

BEGIN

u1:

PROCESS

BEGIN

CASEs0IS--类似于真值表的case语句

WHEN'0'=>y<=a2;

WHEN'1'=>y<=a3;

WHENOTHERS=>NULL;

ENDCASE;

ENDPROCESS;

u2:

PROCESS

BEGIN

CASEs1IS--类似于真值表的case语句

WHEN'0'=>outy<=a1;

WHEN'1'=>outy<=y;

WHENOTHERS=>NULL;

ENDCASE;

ENDPROCESS;

ENDARCHITECTUREcase_mux31;

3-4将例3-20程序的计数器改为十二进制计数器,程序用例3-21的方式表述,并且将复位RST改为同步清零控制,加载信号LOAD改为异步控制方式.讨论例3-20与例3-21的异同点.

--解:

十二进制计数器VHDL程序设计.

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYT12IS

PORTINSTD_LOGIC;

DATA:

INSTD_LOGIC_VECTOR<3DOWNTO0>;--4位预置数

DOUT:

OUTSTD_LOGIC_VECTOR<3DOWNTO0>;--计数值输出

COUT:

OUTSTD_LOGIC>;--计数进位输出

ENDT12;

ARCHITECTUREbehavOFT12IS

SIGNALQ:

STD_LOGIC_VECTOR<3DOWNTO0>;

BEGIN

REG:

PROCESS

BEGIN

IFLOAD='0'THENQ<=DATA;--允许加载

ELSIFCLK'EVENTANDCLK='1'THEN--检测时钟上升沿

IFRST='0'THENQ<='0'>;--计数器异步复位

ELSE

IFEN='1'THEN--检测是否允许计数或加载〔同步使能〕

IFLOAD='0'THENQ<=DATA;--允许加载

ELSE

IFQ<12THENQ<=Q+1;--允许计数,检测是否小于9

ELSEQ<='0'>;--大于等于9时,计数值清零

ENDIF;

ENDIF;

ENDIF;

ENDIF;

ENDIF;

ENDPROCESS;

:

PROCESS

BEGIN

IFQ=12THENCOUT<='1';--计数大于9,输出进位信号

ELSECOUT<='0';

ENDIF;

DOUT<=Q;--将计数值向端口输出

ENDPROCESS;

ENDbehav;

3-5设计含有异步清零和计数使能的16位二进制加减可控计数器.

--解:

用VHDL实现含有异步清零和计数使能的16位二进制加减可控计数器.

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

USEIEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITYADD_SUB_16IS

PORTINSTD_LOGIC;

CQ:

OUTSTD_LOGIC_VECTOR<15DOWNTO0>;

COUT:

OUTSTD_LOGIC>;

ENDENTITYADD_SUB_16;

ARCHITECTUREA_S_16OFADD_SUB_16IS

BEGIN

PROCESS

VARIABLECQI:

STD_LOGIC_VECTOR<15DOWNTO0>;

BEGIN

IFRST='1'THENCQI:

='0'>;--计数器异步复位

ELSIFCLK'EVENTANDCLK='1'THEN--检测时钟上升沿

IFADD_EN='1'THEN--检测是否允许计数<同步他能>

IFCQI<16#FFFF#THENCQI:

=CQI+1;--允许计数,检测是否小于65535

ELSECQI:

='0'>;--大于65535,计数值清零

ENDIF;

IFCQI=16#FFFF#THENCOUT<='1';--计数大于9,输出进位信号

ELSECOUT<='0';

ENDIF;

ENDIF;

IFSUB_EN='1'THEN--检测是否允许计数<同步他能>

IFCQI>0THENCQI:

=CQI-1;--允许计数,检测是否小于65535

ELSECQI:

='1'>;--大于65535,计数值清零

ENDIF;

IFCQI=0THENCOUT<='1';--计数大于9,输出进位信号

ELSECOUT<='0';

ENDIF;

ENDIF;

ENDIF;

CQ<=CQI;--将计数值向端口输出

ENDPROCESS;

ENDARCHITECTUREA_S_16;

3-6图3-18是一个含有上升沿触发的D触发器的时序电路,试写出此电路的VHDL设计文件.

图3-18时序电路

--解:

实现图4-19电路的VHDL程序t4_19.vhd

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYt4_19IS

PORTINSTD_LOGIC;

OUT1:

OUTSTD_LOGIC>;

ENDENTITYt4_19;

ARCHITECTUREsxdlOFt4_19IS----时序电路sxdl

SIGNALQ:

STD_LOGIC;

BEGIN

PROCESS

BEGIN

IFCLK0'EVENTANDCLK0='1'THEN--检测时钟上升沿

Q<=NOT;

ENDIF;

ENDPROCESS;

OUT1<=NOTQ;

ENDARCHITECTUREsxdl;

3-7给出1位全减器的VHDL描述;最终实现8位全减器.要求:

1>首先设计1位半减器,然后用例化语句将它们连接起来,图4-20中h_suber是半减器,diff是输出差,s_out是借位输出,sub_in是借位输入.c

yin

xin

diff_out

b

a

图3-191位全加器

--解<1.1>:

实现1位半减器h_suber

LIBRARYIEEE;--半减器描述<1>:

布尔方程描述方法

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYh_suberIS

PORTINSTD_LOGIC;

diff,s_out:

OUTSTD_LOGIC>;

ENDENTITYh_suber;

ARCHITECTUREhs1OFh_suberIS

BEGIN

Diff<=xXOR;

s_out<=ANDy;

ENDARCHITECTUREhs1;

--解<1.2>:

采用例化实现图4-20的1位全减器

LIBRARYIEEE;--1位二进制全减器顺层设计描述

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYf_suberIS

PORTINSTD_LOGIC;

sub_out,diff_out:

OUTSTD_LOGIC>;

ENDENTITYf_suber;

ARCHITECTUREfs1OFf_suberIS

PONENTh_suber--调用半减器声明语句

PORTINSTD_LOGIC;

diff,s_out:

OUTSTD_LOGIC>;

ENDPONENT;

SIGNALa,b,c:

STD_LOGIC;--定义1个信号作为内部的连接线.

BEGIN

u1:

h_suberPORTMAPxin,y=>yin,diff=>a,s_out=>b>;

u2:

h_suberPORTMAPa,y=>sub_in,diff=>diff_out,s_out=>c>;

sub_out<=cORb;

ENDARCHITECTUREfs1;

<2>以1位全减器为基本硬件,构成串行借位的8位减法器,要求用例化语句来完成此项设计<减法运算是x-y-sun_in=difft>.

xinsub_out

yinu0

sub_indiff_out

x0

y0

sin

diff0

xinsub_out

yinu1

sub_indiff_out

x1

y1

diff1

xinsub_out

yinu7

sub_indiff_out

x7

y7

sout

diff7

……………….

……………….

串行借位的8位减法器

a0

a1

a6

--解<2>:

采用例化方法,以1位全减器为基本硬件;实现串行借位的8位减法器<上图所示>.

LIBRARYIEEE;

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYsuber_8IS

PORTINSTD_LOGIC;

y0,y1,y2,y3,y4,y5,y6,y7,sin:

INSTD_LOGIC;

diff0,diff1,diff2,diff3:

OUTSTD_LOGIC;

diff4,diff5,diff6,diff7,sout:

OUTSTD_LOGIC>;

ENDENTITYsuber_8;

ARCHITECTUREs8OFsuber_8IS

PONENTf_suber--调用全减器声明语句

PORTINSTD_LOGIC;

sub_out,diff_out:

OUTSTD_LOGIC>;

ENDPONENT;

SIGNALa0,a1,a2,a3,a4,a5,a6:

STD_LOGIC;--定义1个信号作为内部的连接线.

BEGIN

u0:

f_suberPORTMAPx0,yin=>y0,diff_out=>diff0,sub_in=>sin,sub_out=>a0>;

u1:

f_suberPORTMAPx1,yin=>y1,diff_out=>diff1,sub_in=>a0,sub_out=>a1>;

u2:

f_suberPORTMAPx2,yin=>y2,diff_out=>diff2,sub_in=>a1,sub_out=>a2>;

u3:

f_suberPORTMAPx3,yin=>y3,diff_out=>diff3,sub_in=>a2,sub_out=>a3>;

u4:

f_suberPORTMAPx4,yin=>y4,diff_out=>diff4,sub_in=>a3,sub_out=>a4>;

u5:

f_suberPORTMAPx5,yin=>y5,diff_out=>diff5,sub_in=>a4,sub_out=>a5>;

u6:

f_suberPORTMAPx6,yin=>y6,diff_out=>diff6,sub_in=>a5,sub_out=>a6>;

u7:

f_suberPORTMAPx7,yin=>y7,diff_out=>diff7,sub_in=>a6,sub_out=>sout>;

ENDARCHITECTUREs8;

3-8给出一个4选1多路选择器的VHDL描述.选通控制端有四个输入:

S0、S1、S2、S3.当且仅当S0=0时:

Y=A;S1=0时:

Y=B;S2=0时:

Y=C;S3=0时:

Y=D.

--解:

4选1多路选择器VHDL程序设计.

LIBRARYIEEE;--图3-20RTL图的VHDL程序顶层设计描述

USEIEEE.STD_LOGIC_1164.ALL;

ENTITYmux41aIS

PORTINSTD_LOGIC;

S0,S1,S2,S3:

INSTD_LOGIC;

Y:

OUTSTD_LOGIC>;

ENDENTITYmux41a;

ARCHITECTUREoneOFmux41aIS

SIGNALS