第11章PADSLayout的元器件的布线.docx

《第11章PADSLayout的元器件的布线.docx》由会员分享,可在线阅读,更多相关《第11章PADSLayout的元器件的布线.docx(27页珍藏版)》请在冰豆网上搜索。

第11章PADSLayout的元器件的布线

第11章PADSLayout的元器件的布线

PADSLayout采用自动和交互式的布线方法,采用先进的目标连接与嵌入(OLE)自动化功能,有机地集成了前后端的设计工具,包括最终的测试、准备和生产制造过程。

PADSLayout布线有自动布线和手工布线两种方式。

本章将从布线规则开始,对如何利用PADS2007软件实现元件布线进行详细的介绍。

.1布线规则(RoutingRules)介绍

设计规则(Designrules)允许将设计中的约束(Constraints)直接输入到PADS-Layout中去。

设计规则(Designrules)包括:

(1)安全间距规则(ClearanceRules):

设置设计目标之间最小的空间距离。

(2)布线规则(RoutingRules):

设置过孔类型、长度最短化类型和当前层。

(3)高速电路规则(HighSpeedRules):

设置高级规则,如平行、延时、电容和阻抗值。

这些规则能在原理图中设置,也能在PCB中设置再反向传送到原理图中。

下面主要从过孔类型的设置、长度最短化和当前层的设置三个方面来介绍一下布线的规则。

布线规则的设置步骤如下:

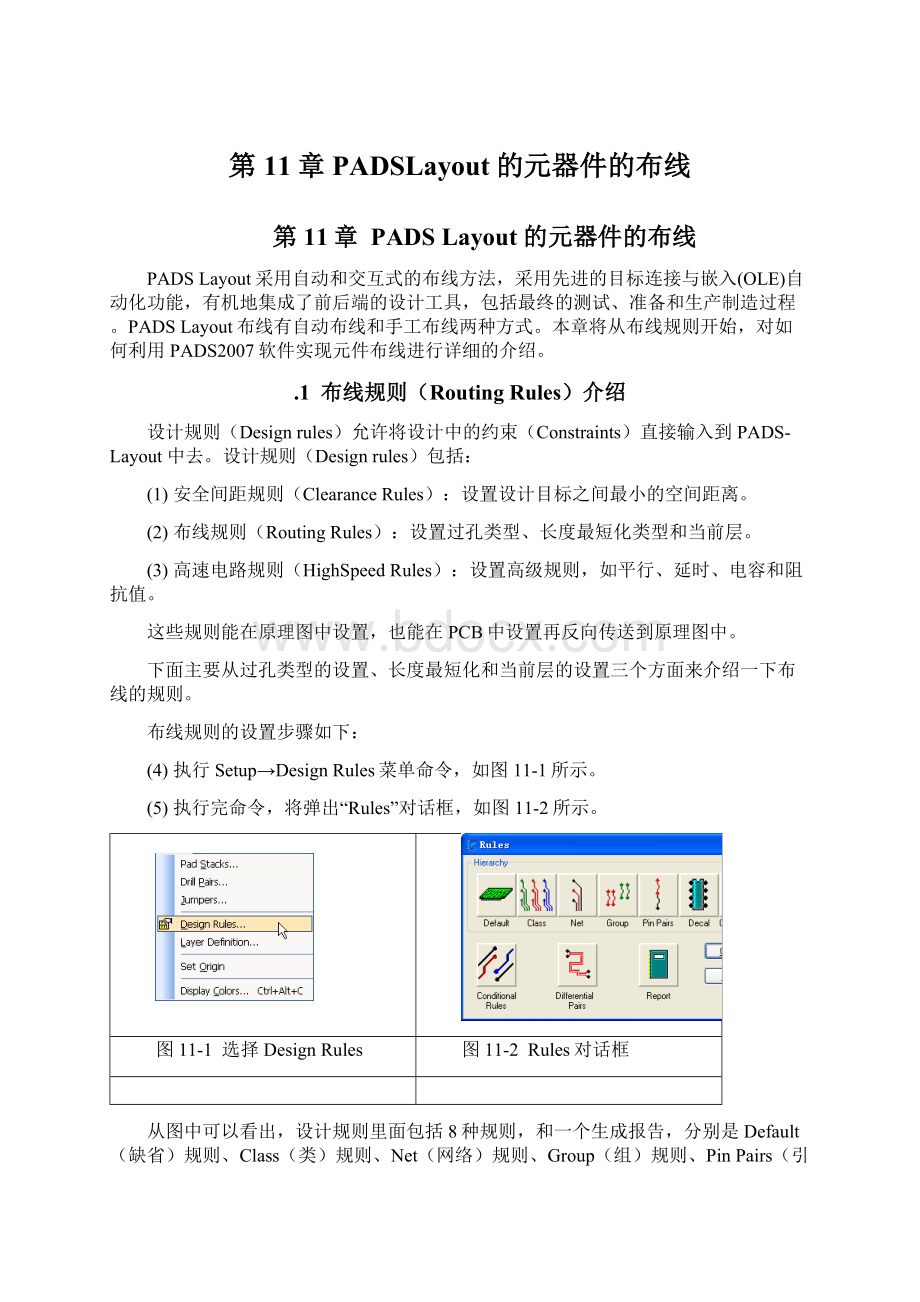

(4)执行Setup→DesignRules菜单命令,如图11-1所示。

(5)执行完命令,将弹出“Rules”对话框,如图11-2所示。

图11-1选择DesignRules

图11-2Rules对话框

从图中可以看出,设计规则里面包括8种规则,和一个生成报告,分别是Default(缺省)规则、Class(类)规则、Net(网络)规则、Group(组)规则、PinPairs(引脚对)规则、Decal(封装)规则、Component(元件)规则、ConditionalRules(条件规则)、DifferentialPairs(不同管脚对)规则,和一个Report(生成报告)。

应该注意的是:

(6)当没有指定任何规则时,默认的是Default(缺省)规则。

(7)其中Class(类)规则、ConditionalRules(条件规则)、DifferentialPairs(不同管脚对)规则,这三种规则组成了(ExtendedRuleSet)扩展规则集。

(8)单击Default图标

时,将出现“DefaultRules”对话框,如图11-3所示。

图11-3DefaultRules对话框

从上图可以看出DefaultRules包括:

Clearance(安全间距)规则,Routing(布线)规则,HiSpeed(高速电路)规则,Fanout(扇出)规则,PadEntry(焊盘接入)规则和Report(生成报告)。

(9)单击Routing图标

,将出现“RoutingRules:

DefaultRules”对话框,如图11-4所示。

图11-4DefaultRules对话框

由上图可以看到:

∙在TopologyType这一栏中点选了SerialSource,表示如果有多个源管脚(ECL)的时候以串行方式放置。

∙在RoutingOptions:

这一栏中,勾选了CopperSharing下的Via和Trace表示布线允许连接到铜皮上。

勾选AutoRoute表示允许布线布到一个已经布好的连线上。

勾选AllowRipup表示允许布线和重新布线。

勾选AllowShoveProtected表示允许交互布线时推挤被固定或保护的网络。

∙在Priority的后面选择的是3,表示设置自动布线时网络布线的优先级是3。

∙AvailableLayers表示显示设计中有效的层,上图中有效层设置的是GroundPlane和PowerPlane。

∙SelectedLayers表示选择希望布线的层,上图中希望布线的层是PrimaryComponentSide和SecondaryComponentSide。

∙在Vias这一栏中,SelectedVias下的STANDARDVIA表示希望选用标准的过孔。

∙在Maximumnumberofvias这一栏中点选Unlimitedvias表示对使用过孔的数量没有限制。

∙单击OK,设置完成,并关闭对话框。

在完成上面RoutingRules的基本设置以后,下面来介绍一下过孔类型的设置。

因为在布线规则中,过孔类型的设置也是一个很重要的设置。

在PADSLayout中可以定义任意种过孔类型。

在交互布线期间,可以指定使用哪一种过孔类型,或者说明某些网络使用某些指定的过孔类型。

过孔类型的设置过程如下:

(10)执行Setup→PadStack菜单命令,如图11-5所示。

(11)执行完命令,就会弹出“PadStacksProperties–STANDARDVIA”对话框,如图11-6所示。

图11-5选择焊盘形状

图11-6STANDARDVIA对话框

∙在PadStackType列表处选择过孔(Via),缺省的名字STANDARDVIA将出现在封装名字(DecalName)区域。

∙在SH:

SZ:

列表处首先选择开始CNN55,并且在参数(Parameters)区域设置它的焊盘直径为55,修改当前标准的过孔定义,然后选择中间层,并把焊盘尺寸(PadSize)改为55,最后选择结束层并且改变焊盘尺寸(PadSize)为55。

∙在Drill.列表处把过孔的钻孔尺寸(DrillSize)设置为37。

∙设置完成,点击OK,保存已经改变的焊盘形状的(PadStacks)设置,关闭对话框。

下面简单的介绍一下布线规律:

(12)布线时要尽量的布短线,尤其是小信号。

(13)当同一层布线改变方向时,应该走斜线。

(14)从焊接面看,组件的排列方位要尽可能与原理图保持一致,布线方向最好与电路图走线方向保持一致,这样做便于生产中的检查,调试及检修,因为在生产过程中通常需要在焊接面进行各种参数的检测。

(15)在印刷电路中不允许有交叉电路,对于可能交叉的线条,可用“钻”、“绕”两种办法来解决。

所谓“钻”就是让某引线从别的电阻、电容、三极管脚下的空隙处“钻”过去,所谓“绕”就是从可能交叉的某条引线的一端“绕”过去,如果在电路很复杂的情况下,可以用导线跨接的方式简化设计,解决交叉电路问题。

(16)同一级电路的接地点应该尽量的靠近,本级晶体管的基极、发射极的接地点不能离得太远,否则会因两个接地点间的铜箔太长会引起干扰与自激,相比接地点离的远的电路,采用“一点接地法”的电路,工作较稳定,不易自激。

(17)总地线必须严格按“高频-中频-低频”一级一级地按弱电到强电的顺序排列,切不可随便翻来覆去的乱接,一级与一级之间宁可接线长点,也要遵守这一规定。

特别是变频头、再生头、调频头的接地线的安排要求更为严格,如有不当就会产生自激导致无法工作。

随意调频头等高频电路常采用大面积包围式地线,以保证有良好的屏蔽效果。

(18)强电流引线如:

公共地线,功放电源引线等,应尽可能宽些,用来降低布线电阻及其电压降,可减小寄生耦合而产生的自激。

(19)保持阻抗高的走线尽量短,阻抗低的走线可长一些,因为阻抗高的走线容易发笛和吸收信号,引起电路不稳定。

电源线、地线、无反馈组件的基极走线、发射极引线等均属低阻抗走线,射极跟随器的基极走线、收录机两个声道的地线必须分开,各自成一路,一直到功效末端再合起来,如两路地线连来连去,极易产生串音,使分离度下降。

(20)在多层印制板布线时,由于在信号线层,剩下的没有布完的线已经不多,如果把这些剩下的线布在一个新的层上不但会增加一定的工作量,而且会造成很多不必要的麻烦和浪费。

为解决这个矛盾,我们可以考虑在电源层或地线层上进行布线。

为了保留地层的完整性最好是在电源层上布线。

.2手动布线

在PADSLayout中,布线的方式有两种,手动布线和自动布线。

手动布线就是使用者以手工的方式将图纸里的鼠线布成铜箔走线。

就当今的电脑技术而言,手动布线仍然是PADSLayout工作最基本、最主要的手段。

在手动布线方式中交互式布线是一个比较重要的布线方式。

所谓交互式布线就是把工程师的布线经验和电脑的布线算法有效地结合在一起,来实现工作设计人员和电脑的交互式布线功能。

在布线过程中只需定义几个关键节点,其余的走线部分由软件根据空间尺寸及最短路径原则自动设计,并优化45°走线拐角;当布线空间有限时,可以用当前走线推挤沿途的布线及过孔,支持平移、垂直的推挤方向,所有被推开布线的形状和拐角都能自动优化。

这种智能的交互式布线功能可以大幅度减轻手工调线的工作量,提高复杂的高密度互连的设计效率。

通常,在进行手动布线之前,首先,参照原理图进行预连线,看一下项目的可连通性怎样,布线是否符合电路模块要求,并根据原理图及实际情况进行器件调整,使其更加有利于走线。

一、交互布线

(21)在PADSLogic界面上打开文件“\PADSProjects\Samples\PREVIEW”,如图11-7所示。

图11-7打开文件

(22)单击按钮

,工作界面就导入了电路图,如图11-8所示。

(23)执行Tools/PADSLayout菜单命令,如图11-9所示。

(24)执行完命令,就会弹出“ConnecttoPADSLayout”对话框,如图11-10所示。

(25)单击按钮

将会弹出“PADSLayoutLink”对话框,如图11-11所示。

(26)选择Design这一项,单击

按钮,发送网络列表。

如图11-12所示。

图11-8打开的PREVIEW的界面

图11-9选择PADSLayout命令

图11-10ConnecttoPADSLayout对话框

图11-11PADSLayoutLink对话框

图11-12PADSLayout的链接对话框

(27)单击按钮

,将进入PADSLayout的界面,如图11-13所示。

图11-13PADSLayout的界面

(28)在PADSLayout的工作界面中元件是叠放在一起的,为了把他们分开先把它们全部选中,如图11-14所示。

(29)全部选中后,执行Tools/DisperseComponents菜单命令,如图11-15所示。

图11-14被选中的元件

图11-15分离元件命令

(30)执行完命令将弹出“PADSLayout”对话框,如图11-16所示。

图11-16开始分离

(31)单击按钮

,所有的元件将被分开,如图11-17所示。

图11-17已经分离好的元件布局

(32)在未选择任何对象的状态下点击鼠标右键,选择SelectTraces/Pins/Unroutes命令,如图11-18所示。

图11-18选择SelectTraces/Pins/Unroutes命令

(33)在PADSLayout工具栏的层组合LayerCombo框中,选中主元件面PrimaryComponentSide,设置它作为当前层。

如图11-19所示。

图11-19选定当前层

(34)设置好当前层后,给界面上的元器件加个边框,直接单击工具栏上的边框图标

,如图11-20所示。

图11-20选中图标

(35)