PLa.docx

《PLa.docx》由会员分享,可在线阅读,更多相关《PLa.docx(20页珍藏版)》请在冰豆网上搜索。

PLa

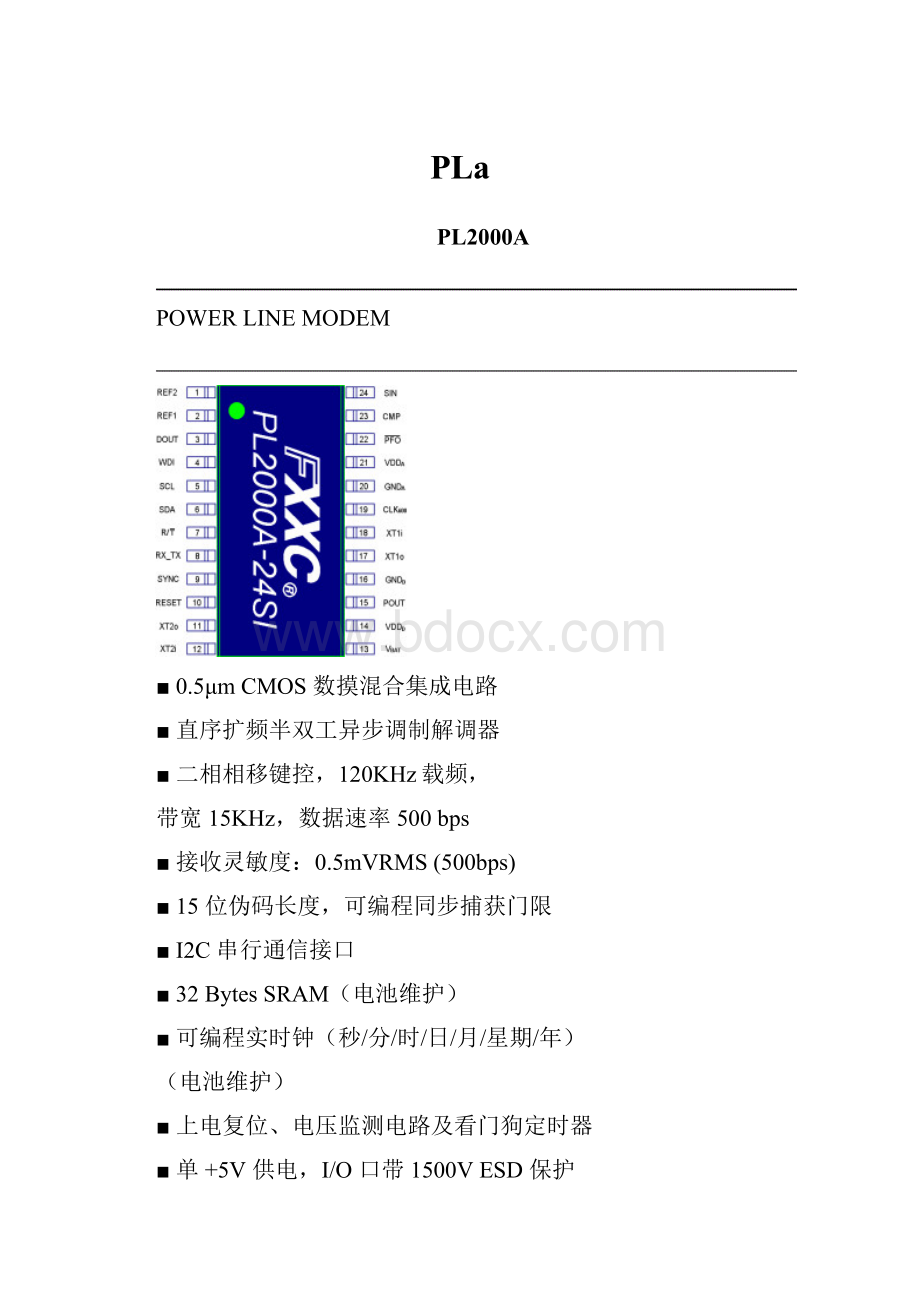

PL2000A

POWERLINEMODEM

■0.5μmCMOS数摸混合集成电路

■直序扩频半双工异步调制解调器

■二相相移键控,120KHz载频,

带宽15KHz,数据速率500bps

■接收灵敏度:

0.5mVRMS(500bps)

■15位伪码长度,可编程同步捕获门限

■I2C串行通信接口

■32BytesSRAM(电池维护)

■可编程实时钟(秒/分/时/日/月/星期/年)

(电池维护)

■上电复位、电压监测电路及看门狗定时器

■单+5V供电,I/O口带1500VESD保护

■工业级温度标准:

-40ºC~+85ºC

■SOP24封装

概述

PL2000A是专为电力线通讯网络设计的半双工异步调制解调器,是PL2000的升级产品。

它仅由单一的+5V电源供电,以及一个外部的接口电路与电力线耦合。

PL2000A除具备原有系统基本的通讯控制功能外,还内置了五种常用的功能电路:

实时钟电路,32BytesSRAM,电压监测,看门狗定时器及复位电路,它们通过标准的I2C接口与外部的微处理器相联,其中实时钟与32BytesSRAM在主电源掉电的情况下可由3V备用电池供电继续保持工作。

PL2000A是特别针对中国电力网恶劣的信道环境所研制开发的低压电力线载波通信芯片,低信噪比数据传输性能比PL2000有了大幅度的提高,同时将数据传输速率提升一倍。

由于采用了直接序列扩频、数字信号处理、直接数字频率合成等新技术,以及大规模数字/模拟混合0.5μmCMOS工艺制作,所以在抗干扰及抗衰落性能以及国内外同类产品性能价格比等方面有着更加出众的表现。

管脚描述

VCCA

模拟部分电源,+4.8–5.0V

VCCD

数字部分电源,+5.0V

VBAT

备用电源,+3.0–3.6V

GNDA

模拟地

GNDD

数字地

Sin

滤波信号输入。

当混频信号经过带通滤波后由此管脚进入内部限幅放大器

CMP

内部电源掉电监测比较器输入端

PFO

电源掉电指示输出端。

PL2000A除提供内部电源电压监测/复位电路外还额外提供一个模拟电压比较器,它的一个输入端接片内的1.7V电压基准源,另一个输入端即CMP,它的输出端即PFO

CLK600

600KHz本振输出端。

该管脚输出600KHz方波信号,作为外接模拟混频器MC3357/MC3361的本振输入信号

Dout

内部限幅放大器输出端(片内与数字部分的A/D相连)

XT1o

9.6MHz主晶体振荡器输出端

XT1i

9.6MHz主晶体振荡器输入端

WDI

看门狗计数器清零输入端。

当WDI持续436mS以上无高低电平变化,将导致看门狗计数器溢出复位

RESET

上电复位及看门狗计数器溢出复位输出端(高电平有效,持续时间218mS)。

当电源电压低于4.65V时,RESET脚持续输出高电平

SCL

I2C串行总线时钟输入端

SDA

I2C串行总线数据输入/输出端。

R/〒

半双工收发控制输入端。

(高电平收/低电平发)

RX_TX

半双工数据收发输入/输出端

Ref1

参考电压基准1

Ref2

参考电压基准2

XT2o

32.768KHz晶体振荡器输出端

XT2i

32.768KHz晶体振荡器输入端

SYNC

数据同步端(HEAD)

PSK_OUT

数字信号发送输出端。

说明:

1、XT1i,XT1o:

9.6MHz主晶体振荡器输入/输出端。

XT1i、XT1o分别为片内反相放大器的输入端和输出端,外接晶体可以组成晶体振荡器。

PL2000A主振荡器所需时钟频率为9.6MHz。

电路连接如图所示,为使振荡器工作更加可靠,电容C1、C2一般用10-30pF之间选择。

若使用外部时钟,可直接从XT1i输入9.6MHz的时钟信号。

2、XT2i/XT2o:

32.768KHz实时钟晶体振荡器输入/输出端。

XT2i、XT2o分别为片内反相放大器的输入端和输出端,外接晶体可以组成晶体振荡器。

为使振荡器工作频率更加稳定可靠,可通过调节外接电容的容值来获得。

一般取值可在2-10pF之间选择。

若使用外部时钟,可直接从XT2i输入32.768KHz的时钟信号。

I2C接口时序:

1.管脚说明

1SDA串行地址/数据输入/输出端

这是一个双向传输端,用于传输地址和数据进入PL2000A,以及从PL2000A发送数据至外部MCU或其它控制器件。

对于一般的数据传输,仅在SCL为低期间SDA才可以变化。

在SCL为高期间变化,留给指示START(开始)和STOP(停止)条件。

②SCL串行时钟端

此为时钟输入端,用于同步进入PL2000A和从PL2000A发出的数据。

2.I2C时序描述

PL2000A支持双向两线总线和数据传输协议。

当器件处于传送数据到总线状态时,我们称之为发送器,当器件处于接受数据状态时则称为接受器。

总线必须由一个主器件控制,主器件可以是MCU或其它设备,它产生串行时钟(SCL),控制总线存取,并且产生开始位(START)和停止位(END),而PL2000A作为从器件工作。

主器件和从器件都能工作于发送器或者接受器的状态,但何种方式有效由主器件决定。

为明确起见,除非另作说明以后所指的从器件均代表PL2000A。

1总线数据传输开始/停止

●总线不忙(A)—数据和时钟线保持高

●开始传送数据(B)—当时钟(SCL)为高,SDA线由高到底的变化将产生起始位(StartBit),所有的命令必须在产生起始位以后进行。

●停止数据传送—当时钟(SCL)为高,SDA线由低到高的变化将产生停止位(EndBit),所有的命令必须在产生停止位以前结束。

2

数据有效

●在起始位后,时钟信号的高电平周期期间,当数据线是稳定时,数据线的状态表示数据线有效。

●数据线上的数据改变必须发生在时钟信号为低电平周期期间,每位数据需一个时钟。

●每次数据的传输必须在起始位后开始,在停止位前结束。

在开始和停止条件之间数据字节的传输数目由主器件决定。

3输出应答

●在每一个字节被接收后,接受器件必须产生一个确认位(ACK)当接受器准备接收下一字节,或否定位(NACK)当接受器准备结束接收状态。

●主器件必须产生一个与此确认位相应的额外时钟脉冲。

●通过在相对应于确认位时钟脉冲的高电平期间拉SDA线为稳定的低电平,可产生确认位(或置SDA线为稳定的高电平,产生否定位)。

●若不在从器件输出的最后一个字节中产生确认位,主器件必须发一个数据结束信号给从器件(即产生否定位)。

在这种情况下,从器件会保持数据线为高电平,使得主器件能产生停止位以便结束本次总线数据传输。

④从器件代码

●产生起始位以后,总线主器件必须对PL2000A发送七位器件代码(1011000)组成的从器件地址,以便选中PL2000A并使得总线上的其它从器件处于非选中状态并让出总线控制权。

●从器件地址的第八位R/W位的状态决定主器件对PL2000A进行何种操作(读或写)。

●PL2000A一直监视总线上与它相应的从器件地址,如果从器件地址相符并且器件不忙,则PL2000A产生一个确认位。

操作

器件码

读/写

读

写

1011000

1011000

1

0

START

READ/WRITE

SLAVEADDRESS

R/W

A

1

0

1

1

0

0

0

⑤地址字节

●地址字节是由主器件发出的八位地址码,用来寻址PL2000A内部的存储寄存器。

●PL2000A内部寄存器地址空间的分配如下

地址字节内容

说明

00000000—00011111(00H-1FH)

SRAM

01000000(40H)

秒

01000001(41H)

分

01000010(42H)

时

01000011(43H)

日

01000100(44H)

月

01000101(45H)

星期

01000110(46H)

年

01001000(48H)

捕获门限

01001111(4FH)

写保护

PL2000A内部寄存器地址空间从00H-FFH共计256个字节,除上表所列的以外其余均为无效地址,对无效地址写入的数据将会被丢弃,从无效地址读出的数据没有实际意义。

为保持程序代码的兼容性,我们建议不要使用无效地址(因为它可能会被PL210X系列的其它版本芯片使用),以便软件可以被不加修改的直接移植到PL210X系列的其它系统中。

⑥写保护

●PL2000A上电复位后,写操作是被禁止的(4FH字节的bit7被自动清零),整个地址空间内除写保护字节可读/写寻址外,其余地址只能做读寻址。

●若要打开写保护,需使写入写保护地址字节的数据最高位为1。

3.写操作

1写单字节数据

●在主器件发出起始位以后,主器件发送七位器件代码,以及一位低电平的读写位到总线上,这指示PL2000A将被寻址,一个地址字节将跟在第九个时钟周期由PL2000A产生的确认位之后。

由主器件发送的地址字节会被写入到PL2000A的地址指针寄存器。

●主器件接收来自PL2000A的另一个确认信号以后,将数据字节发送到总线上,PL2000A接收它并将其写入到被地址指针寻址的寄存器中。

●PL2000A再次发出确认信号,然后主器件产生停止位结束本次操作。

●任何时候,如果从器件在应该发出确认信号时没有给出确认应答,则表示PL2000A没有正确接收到起始位并进入命令准备状态,这需要主器件重新发送操作命令。

4写多个字节数据

●用与写单字节数据相同的方式把七位器件代码,以及一位低电平的读写位发送到总线上,随后是地址字节和第一个数据字节,但代替产生停止条件,主器件可以连续发送最多达256个数据字节到PL2000A,这些字节将会被写入到相应的寄存器中。

●PL2000A每接收一个数据字节以后,地址指针在内部会自动增1。

●如果主器件在产生停止位以前要发送的数据超过有效的地址空间,数据将会被丢弃。

当PL2000A内部的地址指针寄存器累加到255(0FFH)后,会自动回零。

4.读操作

1读当前地址内容

●PL2000A内部的地址指针寄存器保持被存取的最后一个数据字节的地址,并在片内自动加1。

如果以前存取(读或写操作均可)的地址为n,下一个读操作从n+1地址中读出数据。

但对于地址指针寄存器的加1操作相对与读/写时序是不同的,当主器件做连续读操作时是先读后加,连续写操作时是先加后写(第一个被写入的数据字节在写周期前没有地址加操作)。

●当PL2000A接收到R/W位为1的情况下,PL2000A发送一个确认位并随后送出8位数据字节,然后主器件不确认传递(产生NACK),再发送停止位结束本次操作。

2读随机地址内容

●这种方式可以让主器件读取PL2000A片内任意地址的寄存器内容,要完成这种方式的读操作需要首先设置片内地址指针寄存器,这可通过将地址字节作为写操作的一部分送给PL2000A来完成。

●发送了地址字节后,主器件在确认位后面立即产生一个起始位,用这种方式结束写操作并开始另一个读操作。

●主器件再次发出器件代码,并使R/W位为“1”,PL2000A将发出确认位并随后发送由上次地址写操作设置的地址指针寻址的8位数据字节,然后主器件不确认传递(产生NACK),再产生一个停止位结束本次操作。

3

读顺序地址的内容

●读顺序地址内容的方式与读随意地址内容的方式以相同的方式启动,PL2000A发送完第一个数据字节以后,主器件发出一个确认位(ACK),这样PL2000A将会发送下一个顺序地址的8位数据字节,直至主器件发出NACK或停止位。

●为提供这种读方式,PL2000A包含的地址指针寄存器在每次操作完成以后自动加1。

●利用这一特性,可以在一次操作期间连续顺序地读出整个存储器的内容。

但不在有效地址空间内的数据字节会被FFH取代。

片内寄存器地址/功能描述:

SRAM:

(00H-1FH)共计32个字节,在主电源掉电后可由备用电池继续供电,保持数据不丢失。

实时钟:

秒 (40H) 二进制(BIN)表示,0-59表示零秒至五十九秒。

分 (41H) 二进制(BIN)表示,0-59表示零分至五十九分。

时 (42H) 二进制(BIN)表示,0-23表示零点至二十三点。

日 (43H) 二进制(BIN)表示,1-31表示一号至三十一号。

月 (44H) 二进制(BIN)表示,1-12表示一月至十二月。

星期(45H) 二进制(BIN)表示,1-6表示周一至周六,0表示星期日。

年 (46H) 二进制(BIN)表示,0-99表示2000年至2099年。

特殊寄存器:

捕获门限(48H)扩频伪码同步捕获门限,上电复位缺省值为30H。

写保护(4FH)写保护字节的最高位为“0”使能写保护,禁止对整个地址空间(除写保护字节本身)的写操作,写保护字节的最高位为“1”取消写保护。

其它位保留供功能扩展使用。

写保护字节上电复位缺省值为30H。

极限参数:

最高结温:

…………………150℃工作温度:

…………-40℃~+85℃

电源电压:

……………………7V焊接温度(3S):

………+300℃

数字输入:

……………-0.7V~VCC储存温度:

…………-65℃~+165℃

最高时钟频率:

……………20MHz最大耗散功率:

………………0.65W

电特性

表1电特性

特性

符号

条件

-20≤TA≤80℃)

规范值

单位

最小

最大

V

输出高电平

VOH

VDD=4.5VIOH=-20μA

VIH=3.15VIL=0.8V

4.2

-

VDD=5.5VIOH=-4.0mA

VIH=3.15VIL=0.8V

3.5

-

输出低电平

VOL

VDD=4.5VIOH=20μA

VIH=3.15VIL=0.8V

-

0.2

VDD=5.5VIOH=4.0mA

VIH=3.15VIL=0.8V

-

0.45

输入高电平

VIH

VDD=5.5V

3.15

输入低电平

VIL

VDD=4.5V

0.8

输入漏电流

II

VI=VDD或GND

-

±10.0

μA

静态电源电流

IDD

VI=VDD或GND,IO=0μA

-

800

输入电容

CI1)

TA=25℃

-

10

PF

输出电容

CO1)

-

10

温度范围

Blank=Commercial=0°Cto+70°C

I=Industrial=-40°Cto+85°C

封装类型

P=24-LeadPlasticDIP

S=24-LeadSOC

Q=44-LeadPQFP

PL2000A典型应用图:

PL2000A应用例程及说明

1、以2051单片机的管脚为例进行定义:

R/〒BITP1.6;对应PL2000A芯片的第7脚

RX_TXBITP1.7;对应PL2000A芯片的第8脚

SYNCBITP3.3;对应PL2000A芯片的第9脚,单片机为

INT1

2、PL2000A上电复位后,捕获门限寄存器值为根据电力线状况的优选默认数据值:

40H;

捕获门限寄存器数据可以通过I2C总线读写,读写方式与标准I2C器件相同,或参见PL2000A说明书,PL2000A器件地址参PL2000A说明书;捕获门限地址寄存器地址为48H;

建议:

可以采用读捕获门限地址寄存器地址内容是否等于40H来判断是否需要初始化。

3、对PL2000A芯片的数据发送操作步骤:

a、R/〒置为“0”、发射态;

b、在SYNC对应引脚产生中断时,将发送数据的比特移位到RX_TX管脚;

c、等待下一次SYNC中断,返回b步骤

d、直到发送数据发送结束;

e、置R/〒为“1”、恢复接收态;

4、对PL2000A芯片的数据接收操作步骤:

a、置R/〒为“1”、接收态;

b、在SYNC对应引脚产生中断时,将RX_TX管脚比特数据移位到C(寄存器)并保存;

c、等待下一次SYNC中断,返回b步骤

d、直到按规约接收一次完整帧;

e、进行数据处理;

5同步接收数据过程:

R/〒为“1”、接收态,SYNC发生下降沿产生中断后,将RX_TX状态读入缓冲字节;

在16Bit的滑动窗口中搜索同步帧,当搜索到0x09、0xaf同步帧头后,表示已经进入同步状态;

随后数据为通讯数据体,接收数据每8Bit依次还原为一个有效字节数据,由规约进行解释,直至接收完成。

试验数据:

通道1为PL2000ADEMO板耦合线圈输入信号(未施加干扰源)。

通道1为PL2000ADEMO板耦合线圈输入信号(施加宽带干扰源)。

通道1为SYNC,通道2为接收端伪码输出,我们可以清楚地看到后三个同步后的输出。

通道1为SYNC,通道2为数据解调输出。