微处理器与接口技术A答案.docx

《微处理器与接口技术A答案.docx》由会员分享,可在线阅读,更多相关《微处理器与接口技术A答案.docx(16页珍藏版)》请在冰豆网上搜索。

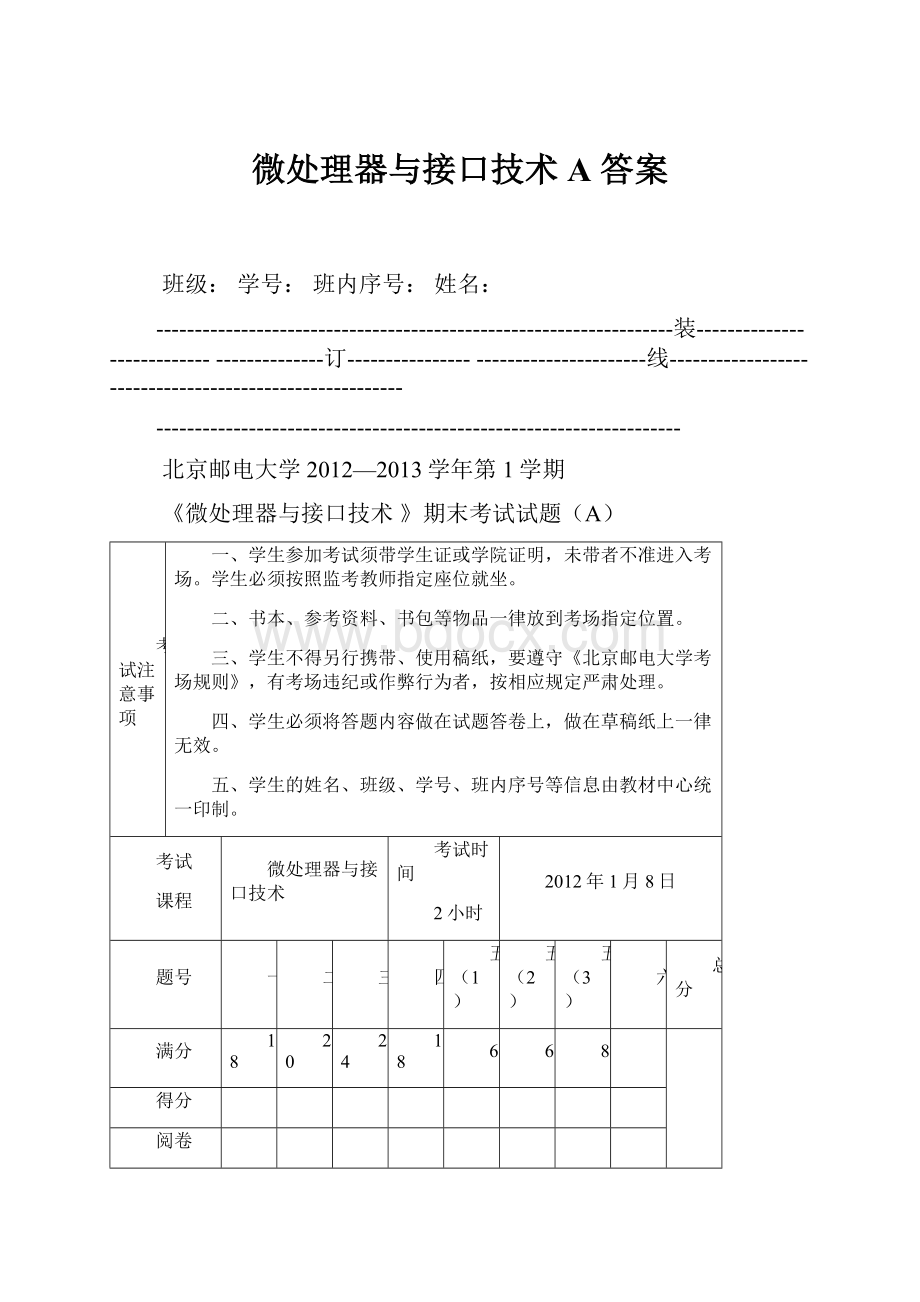

微处理器与接口技术A答案

班级:

学号:

班内序号:

姓名:

-------------------------------------------------------------------装-----------------------------------------订--------------------------------------线--------------------------------------------------------

--------------------------------------------------------------------

北京邮电大学2012—2013学年第1学期

《微处理器与接口技术》期末考试试题(A)

考试注意事项

一、学生参加考试须带学生证或学院证明,未带者不准进入考场。

学生必须按照监考教师指定座位就坐。

二、书本、参考资料、书包等物品一律放到考场指定位置。

三、学生不得另行携带、使用稿纸,要遵守《北京邮电大学考场规则》,有考场违纪或作弊行为者,按相应规定严肃处理。

四、学生必须将答题内容做在试题答卷上,做在草稿纸上一律无效。

五、学生的姓名、班级、学号、班内序号等信息由教材中心统一印制。

考试

课程

微处理器与接口技术

考试时间

2小时

2012年1月8日

题号

一

二

三

四

五

(1)

五

(2)

五(3)

六

总分

满分

18

20

24

18

6

6

8

得分

阅卷

教师

一、填空题(每空1分,共18分)

1.假设AL中存放二进制数01011101B,若执行指令NEGAL后再执行CBW,则AX的内容为0FFA3H,如果认为结果是补码,则按十进制大小是-93。

2.8086在执行MOVAL,[2001H]时,需要一个总线周期,ALE在该总线周期内要持续1个时钟周期有效,此时BHE为0/低电平,A0为1/高电平。

3.某8位数据总线的微处理器系统中由6片16K×4的芯片组成ROM内存,若该内存的末地址为0FFFFFH,则其首地址为0F4000H(填写物理地址)。

4.计算机内的堆栈存取采用后进先出/先进后出原则,有一个堆栈区,地址为1250H:

0000H~1250H:

0100H,(SP)=0052H,则栈顶的物理地址是1250H:

0052H/12552H,栈底的物理地址是1250H:

0100H/12600H。

5.已定义“VAR1DB01H,10H,00H,02H”,且AX=0210H,则指令“DIVVAR1+1”的源操作数是10H,执行该指令后不会(会/不会)发生除法溢出中断。

6.标志寄存器中,TF标志没有相应的指令来修改,可以通过以下命令来对其置位,请补充完整。

PUSHF

POPAX

ORAX,0100H

PUSHAX

POPF

7.D/A转换器的分辨率是指其所能分辨的最小电压。

8.8086的INTR中断响应时会发出两个低电平的中断响应周期,其中在第

2个中断响应周期,8259会通过数据总线向CPU提供中断类型号,该类型号的低3位由8259的中端输入引脚的编号提供。

9.8253的工作方式中,方式1和5(要填写所有符合条件的方式)要通过GATE端来触发启动计数,在计数过程中如果需要读取计数值,应该向8253发出一个锁存命令。

二、判断题,正确的在括号内打√,否则打×(每小题2分,共20分)

1.8086的指令执行部件EU负责指令的执行,所以读写存储器的MOV指令产生的读写控制信号由EU负责产生。

(×)

2.在8086总线周期的T1状态,若引脚

/S7输出低电平,表示高8位数据总线AD15~AD8上的数据有效。

(√)

3.若Y是数据段中的变量,指令ADDY,OFFSETY是正确的。

(√)

4.PC总线使用8086的最大模式,所以8288总线控制器产生的读写控制信号在PC总线中都可以找到。

(×)

5.采用虚拟存储技术可以解决主存储器的空间和速度不足的问题。

(×)

6.由于8086在中断服务程序执行前,自动设置IF=TF=0,所以返回时系统要将其置位。

(×)

7.采用存储器映像的I/O寻址方式的系统,存储器地址增加,则I/O端口地址就减少,且I/O端口可以有较多的寻址方式。

(√)

8.8237DMA数据块传送模式的特点是:

一次请求传送一个数据块,但在整个DMA传送期间如果有中断请求,CPU不能响应它。

(√)

9.在多级8259的情况下,对于主从8259需要分别初始化,而且总是会使用初始化命令字ICW4。

(√)

10.DRAM以MOS晶体管的栅极电容来存储二进制信息,需要定时刷新。

(√)

三、选择题(每小题2分,共24分)

1.CPU中程序计数器(IP)中存放的是(B)。

A.指令

B.指令地址

C.操作数

D.操作数地址

2.当8086/8088访问100H端口时,采用(C)寻址方式。

A.直接

B.立即

C.寄存器间接

D.相对

3.设BL=05H,要使结果BL=0AH,应执行的指令是(C)。

A.NOTBL

B.ANDBL

C.XORBL,0FH

D.ORBL,0FH

4.在同一程序段中,定义有下面的伪指令,使用正确的是(B)。

A.PORT1EQUALPORT1EQU2000H

B.PORT2=3500HAND0FFH

C.POPDD‘ABCD’

D.PORT4PROC…RETEND

5.已知(SP)=1310H,执行IRET指令后(SP)为(D)。

A.1304H

B.1314H

C.1312H

D.1316H

6.某微机接口电路中,要设置10个只读寄存器、8个只写寄存器和6个可读可写寄存器,一般应为它至少提供(C)个端口地址。

A.24B.14C.16D.18

7.主存储器和CPU之间增加高速缓冲存储器的目的是(A)。

A.解决CPU和主存之间的速度匹配问题

B.扩大主存储器的容量

C.扩大CPU中通用寄存器的数量

D.既扩大主存储器的容量又解决CPU和主存之间的速度匹配问题

8.如果有多个中断同时发生,系统将根据中断优先级响应优先级最高的中断请求。

若要调整中断事件的响应次序,可以利用(B)。

A.中断响应B.中断屏蔽C.中断向量D.中断嵌套

9.8088系统中,15H号中断的中断向量存放在内存储器的(A)单元中。

A.0000:

0054H-0000:

0057HB.0000:

0060H-0000:

0063H

C.FFF0:

0054H-FFF0:

0057HD.FFF0:

0060H-FFF0:

0063H

10.PC系列机中,确定外部硬中断的服务程序入口的地址是(D)。

A.主程序中的调用指令B.主程序中条件转移指令

C.中断控制器中的中断服务寄存器D.中断控制器发出的中断向量号

11.设串行异步通信的数据格式是:

1位停止位,7位数据位,1位校验位,1位起始位。

若传输率为2400位/秒,则每秒传输的最大字符个数为(D)。

A.10个B.110个C.120个D.240个

12.8237A的地址是双向的,因为(D)。

A.8237A可以传输输入/输出的地址

B.8237A内部的地址是双向的

C.8237A作为系统总线时应该是双向的

D.8237A既可以是系统总线的主控者,也可以是从设备

四、简答题(每题4分,共24分)

1、说明堆栈的概念,用途,给出定义堆栈段(1024Byte)和初始化相关寄存器的代码。

堆栈是后进先出方式组织的一块存储区域。

主要用来保存返回地址和临时变量。

stksegmentstack

skeepdb1024dup(?

)

stkends

movax,segstk

movss,ax

movspsizeskeep

2、说明什么是立即寻址、直接寻址以及CPU是如何取得要执行的指令的。

操作数包含在指令中,是立即寻址。

操作数的地址包含在指令中,是直接寻址。

取指令的寻址方式是寄存器间接寻址。

3、总线周期的含义是什么?

8086/8088的基本总线周期由几个时钟周期组成?

如果一个CPU的时钟频率为4.77MHz,那么,它的一个时钟周期是多少?

一个基本总线周期为多少?

一个总线周期是CPU通过总线与外部(MEM/IO口)进行一次通讯所需要的时间。

4个。

0.21us(1/4.77)。

0.84us(4/4.77)。

4、说明A/D转换的逐次逼近法原理。

逐次逼近法的转换时间与哪些因素有关?

逐次逼近法是在AD内部使用逐次逼近寄存器,将该寄存器的值与模拟信号比较,从高位开始逐位设置和调整寄存器内容,最终确定变换结果。

转换时间是A/D的位数乘以一次转换和比较的时间。

5、说明IO端口的两种编址方式,各自对指令系统和硬件有什么要求?

与内存统一编址和独立编制。

独立编址需要单独的IO指令,总线需要独立的IO访问控制或指示信号。

统一编址没有这些要求。

6、说明DMA的工作原理,简述外设、DMAC、CPU的交互过程。

DMA由DMAC控制系统,直接在内存和IO设备之间进行数据传递。

外设向DMAC发出请求(DRQ),DMAC向CPU发出HOLD,CPU回应HLDA,DMAC向外设发出DACK。

五、接口综合题(共20分)

1.接口电路如图,请回答如下问题(6分):

(1)题目中,8259A的地址范围是多少?

写出对应的全部地址空间。

(2分)

000C0H,000C2H

000C1H,000C3H

000C4H,000C6H

000C5H,000C7H

(2)主程序片段如下,则IR2上的某外设中断源对应的中断向量号多少?

(2分)

4AH

STAR:

MOVDX,ADDR1;ADDR1为使8259A的引脚A0=0的地址

MOVAL,13H;ICW1赋值

OUTDX,AL

MOVDX,ADDR2;ADDR2为使8259A的引脚A0=1的地址

MOVAL,48H;ICW2赋值

OUTDX,AL

MOVAL,00000001(01H),或00000101(05H)(A);ICW4赋值

OUTDX,AL

(3)对应于上述主程序,IR2上的中断源对应的中断程序如下,请补充填写其中的程序语句,完成数据输入功能。

(2分)

my_intprocfar

pushax

sti

…

<中断服务程序主体>

popax

moval,20h

outADDR1,al;写OCW2

iret

my_intendp

附:

ICW1、ICW2、ICW4、OCW2说明

2.PC总线和A/D转换接口电路如下图,图中信号均是PC(8位)总线信号。

请回答下面问题:

(6分)

其中:

AEN:

地址允许信号,输出,高电平有效。

AEN=1,表明处于DMA控制周期;AEN=0,表示非DMA周期。

(1)中断控制器8259A和并行接口8255A各有几个端口地址?

各芯片内地址有无重叠?

(2分)

8259A和8255A各有4个端口地址;8259A内部有地址重叠,重叠两次;而8255A没有地址重叠。

(2)图中并行接口8255A的C口低4位应工作在什么方式?

(1分)

C口低4位工作于方式0的输出方式。

(3)如何控制A/D转换开始?

若8255A的口地址是20H~23H,编写一段完成A/D转换开始的程序。

(2分)

CPU先在数据线D2~D0上发送一个IN0~IN7中某个通道的地址,选择一个模拟通道,再让8255A的C口的PC2、PC3输出高电平即可使A/D开始转换。

程序如下:

MOVAL,1XXX0X0B;X表示0和1都可以。

OUT23H,AL;写入方式字

MOVAL,0CH;(00001100B)使PC2、PC3为高电平

OUT22H,AL;把0CH写入C口。

可使A/D转换开始

(4)CPU如何知道A/D转换结束?

CPU何时以及如何读取转换好的数据?

(1分)

从图中可知A/D转换结束信号为EOC,该信号接到8259A的IR2,所以CPU发现中断请求后就可知道A/D转换结束。

CPU在中断响应后,转入IR2的中断服务程序既可读取A/D转换好的数据。

附:

8255A方式选择控制字

3.根据以下连接示意图回答问题。

(8分)

注:

图中

(a)8086系统总线的地址信号

经过或非门后的输出接至74LS138的

端;

(b)图中有一特殊外设,其发送的数据送到8255的PA引脚端,但其发送数据有如下要求:

需由人手动控制,即只有在开关K每次从合上到断开后才允许其发送一个8位的数据给8255;另外当START端有下降沿出现时,启动该设备发送数据,当RDY端为高电平时,表明8255的PA端含有该外设新发的数据。

若需将该特殊外设发来的数据填满所指定的BUF缓冲区,某人编写了如下程序:

DATASEGMENT

BUFDB10DUP(?

)

DATAENDS

CODESEGMENT

ASSUMECS:

CODE,DS:

DATA

PORT8259EVEQU__

(1)18H;8259端口地址之一

;(当其引脚A0=0时)

PORT8259ODEQU__

(2)1AH;8259端口地址之一

;(当其引脚A0=1时)

PORT8255PAEQU__(3)04H;8255端口A地址

PORT8255PCEQU__(4)06H;8255端口C地址

PORT8255CTRLEQU__(5)07H;8255控制端口地址

INITINTPROCNEAR

CLI

…;初始化8259(IR端上升沿触发等),不屏蔽IR5

;填写中断向量(INTSRV)等等(具体代码此处略去)

RET

INITINTENDP

START:

MOVAX,DATA

MOVDS,AX

MOVAL,91H;8255端口A及C方式0,A口输入

;C口高4位输出,低4位输入

OUT__(6)PORT8255CTRL,AL;初始化8255

CALLINITINT

MOVAL,0FH

OUTPORT8255CTRL,AL

MOVSI,OFFSETBUF

MOVCX,10

STI

LCONT:

CMPCX,0

JNZLCONT

INAL,PORT8259OD

ORAL,20H

OUTPORT8259OD,AL;屏蔽IR5中断

MOVAH,4CH

INT21H;返回DOS

INTSRVPROCFAR

CALLRECVDATA;(7)

MOVAL,20H

OUTPORT8259EV,AL;发送EOI(中断结束)命令

IRET

INTSRVENDP

CODEENDS

ENDSTART

(1)上述程序

(1)

(2)(3)(4)(5)(6)处缺写的内容分别是什么?

(3分)

见题目中

(2)完整编写出在上述程序(7)处所调用的子程序(RECVDATA)。

(5分)

子程序:

RECVDATAPROCNEAR;属性也可为FAR

CMPCX,0

JNZCHECK

RET;前三条语句不写也算对

CHECK:

MOVAL,0EH

OUTPORT8255CTRL,AL

MOVAL,0FH

OUTPORT8255CTRL,AL;产生启动信号给外设

INAL,PORT8255PC

TESTAL,01H;检测PC0是否为1(是否准备好)

JZCHECK;未准备好则等待

INAL,PORT8255PA;数据从A口读入

MOV[SI],AL

INCSI;修改指针,指向下一个字符

DECCX;字符数减一

RET

RECVDATAENDP