verilog总复习.docx

《verilog总复习.docx》由会员分享,可在线阅读,更多相关《verilog总复习.docx(34页珍藏版)》请在冰豆网上搜索。

verilog总复习

1.Verilog的主要应用包括:

a)ASIC和FPGA工程师编写可综合的RTL代码

b)使用高抽象级描述仿真系统,进行系统结构开发

c)测试工程师用于编写各种层次的测试程序

d)用于ASIC和FPGA单元或更高层次的模块的模型开发

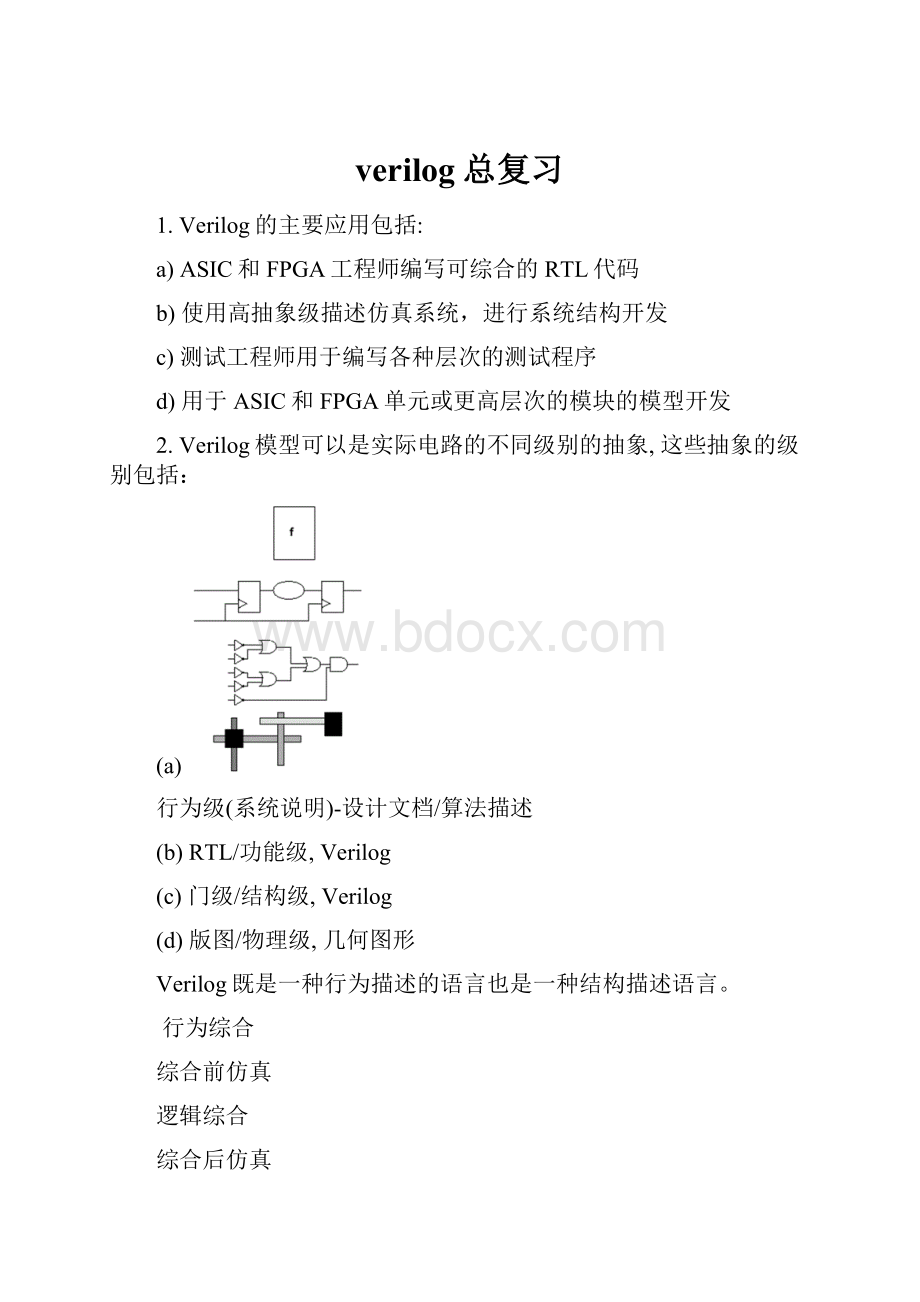

2.Verilog模型可以是实际电路的不同级别的抽象,这些抽象的级别包括:

(a)

行为级(系统说明)-设计文档/算法描述

(b)RTL/功能级,Verilog

(c)门级/结构级,Verilog

(d)版图/物理级,几何图形

Verilog既是一种行为描述的语言也是一种结构描述语言。

行为综合

综合前仿真

逻辑综合

综合后仿真

版图

3.Verilog可以在三种抽象级上进行描述:

a.行为级(Behaviorallevel)

1.用功能块之间的数据流对系统进行描述

2.在需要时在函数块之间进行调度赋值。

b.RTL级/功能级(RTLlevelorFunctionallevel)

1.用功能块内部或功能块之间的数据流和控制信号描

2.基于一个已定义的时钟的周期来定义系统模型

c.结构级/门级(StructurallevelorGatelevel)

1.用基本单元(primitive)或低层元件(component)的连接来描述系统以得到更

高的精确性,特别是时序方面。

2.在综合时用特定工艺和低层元件将RTL描述映射到门级网表

4.二选一多路选择器用RTL和门级电路分别来描述。

5.基本词法:

空白符、注释、常量、字符串、标识符

编译指令

基本语法:

-模块结构

-端口定义(input、output、inout)

-数据类型(net、register、parameter)

-功能描述(assign语句、always语句)

6.基本构件module(Verilog程序包含:

端口定义,I/O说明,内部信号声明,功能定义)

moduleDFF(

//端口说明

Outputregq,

wireqb,

inputwired,//inputdata

clk,/*inputclock*/

clr

);

7.模块实例化的实现:

引用现成元件和模块的方法。

P22

8.单行注释:

//……多行注释:

/*……*/

9.常量的表达(默认位宽:

32位)P29

Verilog中,常量可是整数也可以是实数

整数的大小可以定义也可以不定义。

整数表示为:

'

其中size:

十进制数表示的二进制位数(bit),缺省为32位

base:

数基,可为b、o、d、h进制,缺省为10进制

value:

是所选数基内任意有效数字,包括X(表不定值)、Z(表高阻值)。

实数常量可以用十进制或科学表示法表示。

12无符号十进制数(32位)二进制整数(b或B)

'H83a无符号16进制数(32位)十进制整数(d或D)

8'b1100_00018位二进制数十六进制整数(h或H)

64'hff0164位16进制数八进制整数(o或O)

9'O179位8进制数

32'bz01x32位2进制数

3'b1010_11013位2进制数,截为3’b101

6.3十进制实数

32e-4科学法表示0.0032

4.1E3科学法表示4100

整数的大小可以定义也可以不定义。

整数表示为:

数字中(_)忽略,便于查看

没有定义大小(size)整数缺省为32位

缺省数基为十进制

数基(base)和数字(16进制)中的字母无大小写之分

当数值value大于指定的位数时,截去高位。

如2'b1101表示的是2'b01;小于指定的位数

实数常量

–实数可用科学表示法或十进制表示

–科学表示法表示方式:

<尾数><指数>,表示:

尾数×10指数

负数一个数字可以被定义为负数,只需在位宽前加个减号,必须在最前面。

下画线不可用在位宽和进制处,只能用在具体的数字之间。

10.字符串,格式控制符

Verilog中,字符串大多用于显示信息

Verilog没有字符串数据类型

注意点:

字符串要在一行中用双引号括起来,不能跨行。

字符串中可以使用一些C语言转义(escape)符,如\t\n

可以使用一些C语言格式符(如%b)在仿真时产生格式化输出.

”Thisisanormalstring”

”Thisstringhasa\ttabandendswithanewline\n”

”Thisstringformatsavalue:

val=%b”

格式符:

格式符%0d表示没有前导0的十进制数

%h%o%d%b%c%s%v%m%t

HexoctdecbinACSIIstringstrengthmoduletime

转义符:

\t\n\\\”

Tab换行反斜杠双引号

标识符:

a.标识符是用户在描述时给Verilog对象起的名字

b.标识符必须以字母(a-z,A-Z)或(_)开头,后面可以是字母、数字、($)或(_)

c.最长可以是1023个字符

d.标识符区分大小写,sel和SEL是不同的标识符

e.模块、端口和实例的名字都是标识符.

无效标识符举例:

34net//开头不是字母、“_”

a*b_net//包含了非字母、数字、“$”、“_”

n@238//包含了非字母、数字、“$”、“_”

Verilog区分大小写,所有Verilog关键词使用小写字母。

11.系统任务和函数($)P91

$符号指示这是系统任务和函数;

系统函数有很多,如:

-返回当前仿真时间$time

-显示/监视信号值($display,$monitor)

-停止仿真$stop

-结束仿真$finish

-产生随机数$random(%b.定义的范围—b+1:

b—1)

位并接{}:

{%random}%b范围为:

0~b—1

#delay—延迟声明

(`)—编译指令:

`resetall复位所有的编译指令为缺省值,应该在其它编译指令之前使用

•这些编译指令使仿真编译器进行一些特殊的操作

•编译指令一直保持有效直到被覆盖或解除

`define—文本替换:

`define,替换

`definenot_delay#1(不需要分号)

`defineand_delay#2sig1变量名

`defineor_delay#1‘sig1宏名

moduleMUX2_1(out,a,b,sel);

outputout;

inputa,b,sel;

not`not_delaynot1(sel_,sel);//此处编译是就用#1替换not_delay,提高可读性

`include—文本包含:

a.include在文件中保存全局的或经常用到的一些定义,如文本宏

b.在模块内部include一些任务(tasks),提高代码的可维护性.

`timescale—说明时间单位及精度(`timescale必须在模块之前出现)P112

格式:

`timescale/

如:

`timescale1ns/100ps

time_unit:

延时或时间的测量单位

time_precision:

延时值超出精度要先舍入后使用

注意点:

1.time_precision不能大于time_unit

2.time_precision和time_unit的表示方法:

integerunit_string

3.precision的时间单位应尽量与设计的实际精度相同(timescale1s/1ps,则仿真器在1秒内要扫描其事件序列1012次;而`timescale1s/1ms则只需扫描103)

4.如果没有timescale说明将使用缺省值,一般是s.

5.$time输出的总是整数(需先四舍五入后再输出)

6.$time显示时刻受时间尺度比例的影响。

$realtime输出的是实型数。

7.所有timescale中的最小值决定仿真时的最小时间单位,这是因为仿真器必须对整个设计进行精确仿真。

12.端口和它的数据类型P27

三种端口:

inputoutputinout

格式:

[信号位宽—1:

0]

三种数据类型:

net(连线):

表示器件之间的物理连接(wire,tri…)真值表见P32

register(寄存器):

表示抽象存储元件

parameter(参数):

运行时的常数(run-timeconstants)

寄存器的类型:

reg可定义的无符号整数变量

(二进制补码)integer32位有符号整数变量,通常用作不会由硬件实现的的数据处理

real双精度的带符号浮点变量

time64位无符号整数变量,用于仿真时间的保存与处理

realtime与real内容一致,但可以用作实数仿真时间的保存与处理。

rega;//一个标量寄存器

wandw;//一个标量wand类型net

reg[3:

0]v;//从MSB到LSB的4位寄存器向量

reg[7:

0]m,n;//两个8位寄存器

tri[15:

0]busa;//16位三态总线

wire[0:

31]w1,w2;//两个32位wire,MSB为bit0

13.Verilog采用4值逻辑0,1,X,Z

‘0’表示ZeroLow‘1’表示One,High‘Z’表示高阻状态,也就是没有任何驱动

‘X’表示信号状态时表示未知;当表示条件判断时(casex或casez中)表示不关心

14.参数(重载)

用参数声明一个可变常量,常用于定义延时及宽度变量。

parameter<赋值语句列表>;

参数的定义是局部的,只在当前模块中有效。

可一次定义多个参数,用逗号隔开

在使用常数的地方都可以使用参数

参数定义可使用以前定义的整数和实数参数

参数重载(overriding):

defparam语句(现在综合工具还不支持)

1.可用defparam语句在编译时重载参数值

2.defparam语句引用参数的层次化名称

3.使用defparam语句可单独重载任何参数值

15.Register数组:

1.声明一个寄存器数组:

integerNUMS[7:

0];//8个整数变量的数组

P34timet_vals[3:

0];//4个time变量的数组

2.数据类型为reg的数组通常称为一个memory:

reg[15:

0]MEM[0:

1023];//1Kx16-bitmemoryarray

reg[7:

0]PREP[‘hFFFE:

’hFFFF];//2x8-bitmemoryarray

3.可以使用parameters建模memorysize

16.块语句:

用来将多个语句组织在一起,使得他们在语法上如同一个语句P45

分为两类:

顺序块:

语句置于关键字begin和end之间,块中的语句以顺序方式执行

并行块:

关键字fork和join之间的是并行块语句,块中的语句并行执行

顺序块的特点:

1.块内语句是按顺序执行的。

P452.每一条语句的延迟是相对于前一条语句的仿真时间而言的。

3.直到最后一条语句执行完毕,程序流程控制才跳出该语句块。

并行块的特点:

1.块内语句是同时执行的。

2.块内每条语句的延迟时间是相对于程序控制进入到块内的仿真时间的。

3.延迟时间是用来给赋值语句提供执行程序的。

4.当按时间时序排序在最后的语句执行完后或一个disable语句执行时,程序流程控制跳出该程序块

过程语句有两种:

initial:

只执行一次always:

循环执行

所有过程在时间0执行一次。

过程块之间、assign语句之间、过程块与assign语句均为并行执行

always(时序控制)1.在过程块中的赋值称为过程赋值

begin/fork2.表达式左边的信号必须是寄存器类型(如reg类型)

过程赋值语句;3.等式右边可以是任何有效的表达式,数据类型也没有限制

系统任务和函数;4.如果信号没有声明则缺省为wire类型,使用过程

高级描述语句;赋值语句给wire赋值会产生错误

if语句;

case语句;

循环语句;

end/join

17.操作符的优先级:

18.持续赋值(continuousassignment)被赋值对象是寄存器数据类型的

描述的是组合逻辑,在过程块外部使用,用于net驱动,可以是显式或隐含

在等式左边可以有一个简单延时说明(只限于在表达式左边用#delay形式)

[#delay][strength]=;wireout;

assignout=a&b;//显式

wireinv=~in;//隐含

19.结构描述—用门及门的连接描述器件的功能

基本单元—Verilog语言已定义的具有简单逻辑功能的功能模型(models)模块

•结构描述等价于逻辑图,它们都是连接简单元件来构成更为复杂的元件;Verilog使用其连接特性完成简单元件的连接;

•在描述中使用元件时,通过建立这些元件的实例来完成;

•上面的例子中MUX是没有反馈的组合电路,使用中间或内部信号将门连接起来;描述中忽略了门的实例名,并且同一种门的所有实例可以在一个语句中实例化;

•上面的锁存器(latch)是一个时序元件,其输出反馈到输入上;它没有使用任何内部信号;它使用了实例名并且对两个nor门使用了分开的实例化语句;

•基本单元引脚的数目由连接到门上的net的数量决定,因此当基本单元输入或输出的数量变化时用户不需要重定义一个新的逻辑功能;

•所有门(除了not和buf)可以有多个输入,但只能有一个输出;

•not和buf门可以有多个输出,但只能有一个输入;

20.基本单元实例化:

•在端口列表中,先说明输出端口,然后是输入端口

•实例化时实例的名字是可选项

and(out,in1,in2,in3,in4);//unnamedinstance

bufb1(out1,out2,in);//namedinstance

延时说明是可选项,所说明的延时是固有延时。

输出信号经过所说明的延时才变化。

没有说明时延时为0。

notif0#3.1n1(out,in,cntrl);//delayspecified

信号强度说明是可选项。

not(strong1,weak0)n1(inv,bit);//strengthspecified

module实例化:

模块实例化时实例必须有一个名字

使用位置映射时,端口次序与模块的说明相同

使用名称映射时,端口次序与位置无关

没有连接的输入端口初始化值为x

实例数组:

实例名字后有范围说明时会创建一个实例数组。

在说明实例数组时,实例必须有一个名字(包括基本单元实例)。

其说明语法为:

<模块名字><实例名字><范围>(<端口>);bufif0u[2:

0](out,in,en);

bufif0u2(out[2],in[2],en);bufif0u1(out[1],in[1],en);bufif0u0(out[0],in[0],en);

如果范围中MSB与LSB相同,则只产生一个实例;一个实例名字只能有一个范围。

21.操作符的运算

(1)算术操作符:

modulearithops();注意:

integer和reg类型在算术运算时的差别。

parameterfive=5;integer是有符号数,而reg是无符号数。

integerans,int;

reg[3:

0]rega,regb;

reg[3:

0]num;

initialbegin

rega=3;

regb=4'b1010;

int=-3;//int=1111……1111_1101

end

initialfork

#10ans=five*int;//ans=-15

#20ans=(int+5)/2;//ans=1

#30ans=five/int;//ans=-1

#40num=rega+regb;//num=1101在整数除法中,余数舍弃

#50num=rega+1;//num=0100如果操作数的某一位是x或z,则结果为x

#60num=int;//num=1101负数赋值给reg或其它无符号变量时使用2的补码表示

#70num=regb%rega;//num=1模运算中使用第一个操作数的符号

#80$finish;

join

endmodule

(2)按位操作符

(3)逻辑操作符

(4)

!

logicalnot逻辑反逻辑反的结果为一位1,0或x(10)

~bit-wisenot位反位反的结果与操作数的位数相同(11010010)

(5)移位操作符

(6)==逻辑等值确定是指所有的位为0或1其结果是1’b1、1’b0或1’bx

!

=逻辑不等不确定值是有值为x或z的位

(7)===相同(case等)左边及右边的值相同(包括x、z),则结果为1

!

==不相同(case不等)左边及右边的值不相同,则结果为0

补:

如果逻辑输出在任何时候都直接由当前输入组合决定,则为组合逻辑

如果输出在任何给定时刻不能由输入的状态决定,则为时序逻辑

(8)条件运算符:

=?

:

其意为:

ifcondition为真,则LHS=true_expression,否则LHS=false_expression;

例如:

assignout=(sel==0)?

a:

b;

若sel为0则out=a;若sel为1则out=b。

如果sel为x或z,若a=b=0,则out=0;若a≠b,则out值不确定。

(9)级联操作符(?

?

):

a.可以从不同的矢量中选择位并用它们组成一个新的矢量

b.用于位的重组和矢量构造

(10)复制例如:

regb=2'b11;regc=2'b00;则

#20bus<={{2{regb}},{2{regc}}};//regc和regb复制后的结果级联,//bus=11110000

(11)一元归约操作符

21.与操作(0,1,x,z)P37

&

0

1

x

0

0

0

0

1

0

1

x

x

0

x

x

问:

&&和&有什么不同?

答:

&将操作数从低到高的对应位的进行与操作

&&将每个操作数归约为一位true或false,然后对归约结果进行

22.逻辑强度

逻辑强度模型决定信号组合值是可知还是未知的,以更精确的描述硬件的行为。

下面这些情况是常见的需要信号强度才能精确建模的例子:

开极输出(Opencollectoroutput)(需要上拉)

多个三态驱动器驱动一个信号

MOS充电存储

ECL门(emitterdotting)

逻辑强度是Verilog模型的一个重要部分,通常用于元件建模,如ASIC和FPGA库开发工程师才使用这么详细的强度级。

用户可以给基本单元实例或net定义强度

<基本单元名><强度><延时><实例名>(<端口>);nand(strong1,pull0)#(2:

3:

4)n1(o,a,b)

用户可以用%v格式符显示net的强度值:

$monitor($time,,"output=%v",f);

在Verilog中,级别高的强度覆盖级别低的强度。

(strong,pull,weak,hiz)

23.行为描述的方式,initial和always.

RTL级功能描述:

过程块是行为模型的基础:

initial块,只能执行一次

–always块,循环执行

过程块中由下列内容组成:

过程赋值语句:

描述过程块中的数据流

高级结构(循环,条件语句):

描述块的功能

时序控制:

控制块的执行及块中的语句

24.过程中的时序控制(顺序,并行)

行为零延迟循环:

过程时序控制的种类:

简单延时(#delay):

延迟指定的时间步后执行

边沿敏感的时序控制:

在信号发生翻转后执行

@()可以说明信号有效沿是上升沿(posedge)还是下降沿(negedge)

–可以用关键字or指定多个参数

电平敏感的时序控制:

wait()直至expr值为真时(非零)才执行

若expr已经为真则立即执行

modulewait_test;

regclk,waito,edgeo;

initialbeginclk=0;edgeo=0;waito=0;end

always#10clk=~clk;

always@(clk)#2edgeo=~edgeo;

alwayswait(clk)#2waito=~waito;

endmodule

简单延时:

边沿敏感时序:

wait语句:

顺序语句将被顺序执行,也就是逐条执行;

并行语句在同一时间步内被调度,但经过相关延迟后被执行(但被仿真器在其他时间内执行

LHS:

Left-hand-side

RHS:

Right-hand-side

25.阻塞和非阻塞赋值

阻塞赋值:

执行完成后再执行顺序块内的下一条语句;

非阻塞赋值:

不阻塞过程流,仿真器读入一条赋值语句并对它进行调度之后,就可以处理下一条赋值语句

若过程块中的所有赋值都是非阻塞的,赋值按两步进行:

1.仿真器计算所有RHS表达式的值,保存结果,并进行调度,在时序控制指定的时间赋值;

2.在经过相应的延迟后,仿真器通过将保存的值赋给LHS表达式,完成赋值;

阻塞与非阻塞赋值语句