微型计算机技术讲稿 3.docx

《微型计算机技术讲稿 3.docx》由会员分享,可在线阅读,更多相关《微型计算机技术讲稿 3.docx(7页珍藏版)》请在冰豆网上搜索。

微型计算机技术讲稿3

第二章8086微处理器

8086基本功能:

16位CPU,HMOS工艺,16位DB,20位AB,时钟频率5-10MHZ

2.18086的编程结构

8086CPU分为两大部分:

总线接口部件BIU,执行部件EU

2.1.1总线接口部件—CPU与其外部(存储器、I/O口)的接口

4个段寄存器:

CS代码段,DS数据段,ES附加段,SS堆栈段

16位的指令指针IP

20位的地址加法器—形成20位存储器地址

6字节指令队列(8088为4字节)--实现预取指令缓存

2.1.2执行部件—运算、处理和控制

通用寄存器:

4个16位AX,CX,DX,BX

或8个8位AL,CL,DL,BL,AH,CH,DH,BH

基址指针:

SP—堆栈指针BP—基址指针

变址寄存器:

SI—源变址寄存器DI—目的变址寄存器

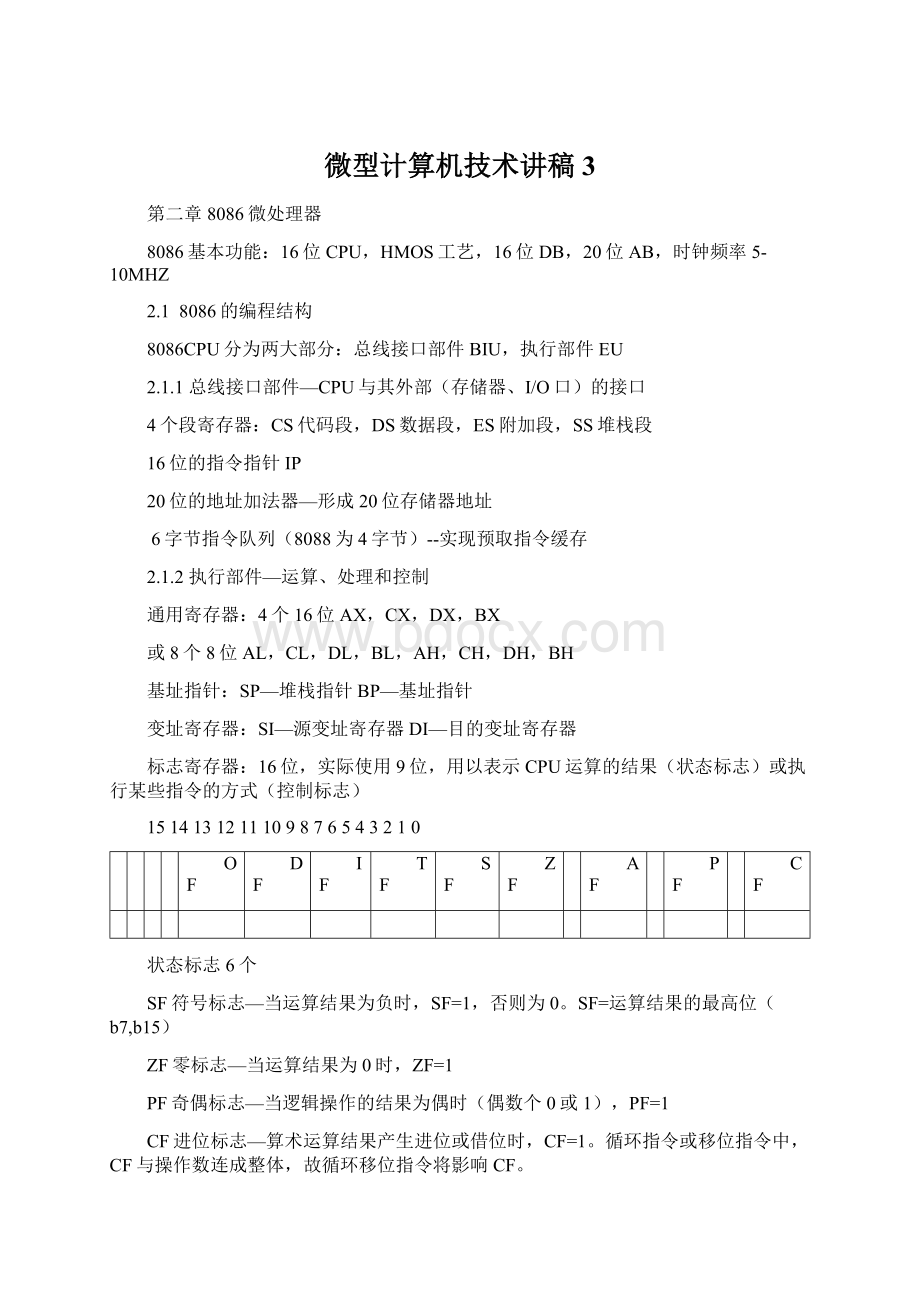

标志寄存器:

16位,实际使用9位,用以表示CPU运算的结果(状态标志)或执行某些指令的方式(控制标志)

1514131211109876543210

OF

DF

IF

TF

SF

ZF

AF

PF

CF

状态标志6个

SF符号标志—当运算结果为负时,SF=1,否则为0。

SF=运算结果的最高位(b7,b15)

ZF零标志—当运算结果为0时,ZF=1

PF奇偶标志—当逻辑操作的结果为偶时(偶数个0或1),PF=1

CF进位标志—算术运算结果产生进位或借位时,CF=1。

循环指令或移位指令中,CF与操作数连成整体,故循环移位指令将影响CF。

AF辅助进位标志—算术运算时,b3,b4间产生进位或借位时,AF=1,它用于BCD运算调整。

OF溢出标志—算术运算发生二进制补码溢出时,OF=1

一般,指令操作将影响(改变)部分标志,或不影响任何标志。

控制标志3个

DF方向标志—数据串操作的方向。

DF=0,数据串操作从低地址端开始,DF=1,从高地址端开始—可用指令(STD,CLD)设置DF的状态。

IF中断允许标志—决定CPU是否响应外部可屏蔽中断。

IF=1,允许响应,IF=0,禁止响应。

可用指令(STI,CLI)设置。

TF跟踪标志(陷阱标志)--CPU是否单步执行指令。

TF=1,CPU一次只执行一条指令。

设置TF标志的方法如下:

PUSHF

POPAX;将标志寄存器F的内容弹出并送到AX

ORAX,0100H;IF置1

PUSHAX;AX送到F

POPF;IF=1,以下指令单步执行

2.1.3BIU和EU的动作管理

8位CPU指令执行过程

*取指

*指令译码,PC=PC+1

*动作(指令执行)

结论:

8位CPU串行操作。

从16位CPU开始,引入并行操作的概念。

*当指令队列中有空时(8086空2字节,8088空1字节),BIU驱动总线周期,预取指令;

*EU从指令队列中取出指令代码,译码执行。

需要访问存储器或I/O口时,通过BIU驱动总线周期;

*指令队列满或无访问存储器或I/O口操作时,BIU空闲;

*当执行转移、调用或返回指令时,清除指令队列。

结论:

8086取指和指令执行是并行完成的。

2.1.48086的总线周期

T1—CPU发出地址及读/写控制信号;

T2--地址浮空,写操作时,CPU送出数据;

T3—CPU读出数据,或将数据写入存储单元;

T4—总线周期结束,CPU撤掉数据及控制信号,为下一次总线周期作准备。

2.28086的引脚及工作模式

2.2.18086的工作模式

最小模式—系统仅包含CPU,8086直接发控制信号,控制电路最简

最大模式—系统包含两个微处理器/协处理器,CPU通过总线控制器发控制信号

8087—数值数据处理器,整数运算8-64位,浮点运算最大32位,超越函数运算

8089—I/O处理机

2.2.28086的引脚信号

40引脚,DIP封装

⑴地址/数据复用

⑵引脚定义不同

⑶复位信号

复位状态:

标志F,IP,DS,SS,ES清零,指令队列清空,CS=FFFFH

8086/8088复位入口地址为CS:

IP=FFFF0H

⑷状态信号

⑸BHE/S7BHE=0表示高8位数据有效,A0=0表示选中偶数单元

2.2.3最小模式

⑴因CPU地址/数据复用,故需地址锁存

⑵同样因地址数据复用,故需数据缓冲,选通数据总线

⑶时钟CLK产生

2.2.4最大模式

最大模式典型配置

最大/最小模式的区别

2.38086的操作和时序

程序—指令—基本操作(微处理器)

微处理器的基本操作类型:

取指令,读写存储器,中断响应,DMA总线响应,I/O读写等。

2.3.1复位和启动

复位入口地址FFFF0H

复位后状态:

寄存器,AB/BD/CB

2.3.2总线操作

总线读写操作

1.最小模式下总线读操作

2.最小模式下总线写操作

3.最大模式下总线读/写操作

4.总线空闲

2.3.3中断操作及中断系统

1.8086的中断类型

256种中断,中断类型码n=0-255

分类方法:

*产生中断的方式:

硬件中断—通过硬件产生(外部请求,计算机硬件故障)的中断。

软件中断—由CPU执行中断调用指令(如INT21H)或软件发生某种错误时产生(如溢出、除法错、单步等)的中断。

*中断响应的方式:

可屏蔽中断—受IF标志的控制,当IF=0时,CPU不予以响应。

不可屏蔽中断—不受IF标志的控制。

*中断源:

内部中断—由内部原因引起。

外部中断—由外部事件引起。

所有可屏蔽中断INTR均由8259中断控制器管理。

2.中断向量和中断向量表

向量—既有大小又有方向的量。

向量中断—中断源给出中断类型码,CPU根据中断类型码查找中断向量表,进而找到中断服务程序入口地址的方法。

8086/8088,中断服务程序入口地址(20位存储单元地址)用4个单元存放。

即段地址(16位):

偏移地址(16位)。

80X86系列CPU用存储器最低端的1KB(地址00000—003FFH)存放中断向量,此区域称为中断向量表。

DEBUG图示中断向量表(DEBUG,D0:

0)

8086/8088系统中,0—4中断类型保留,依次为除法错(0)、单步

(1)、NMI

(2)、断点(3)、溢出中断(4)。

286以上系统中,增加BOUND范围越界(5)、无效操作码(6)协处理器不可用(7)、协处理器出错(16)保留中断类型。

此外,0-31中断内,均为系统保留。

3.硬件中断

系统对于外部请求的优先响应次序依次是:

总线请求—NMI—INTR

总线请求—在每个总线周期结束时响应(该指令并不一定已执行完)。

NMI—在每条指令结束时,且无总线请求时响应。

INTR--在每条指令结束时,在没有总线请求和NMI请求的前提下,且IF=1时响应。

4.硬件中断的响应时序

INTR的响应时序:

条件:

INTR=1即外设申请可屏蔽中断

且IF=1CPU允许INTR

则CPU在当前指令执行后INTR,发两个INTA负脉冲

*CPU从DB上读取中断类型码

*标志F进栈

*IF=0(禁止其它所有INTR),TF=0(禁止单步操作)

*保护断点CS进栈,IP进栈

*根据中断类型码n,找到中断服务程序入口地址,即:

IP=(n*4),CS=(n*4+2)

8086/8088中断响应过程

8086中断响应周期。

第一个总线周期:

CPU发INTA负脉冲,表示中断响应;

第二个总线周期:

CPU发INTA负脉冲,外设(中断控制器)送出中断向量。

可屏蔽中断的响应过程(两个总线周期):

1执行中断响应总线周期,读入中断类型码(总线读),*4(左移2位);

2标志寄存器进栈,同时置IF=TF=0,禁止响应新的可屏蔽中断请求,禁止单步中断(总线写);

3CS进栈(总线写);

4IP进栈(总线写);

5IP=(n*4)读入中断服务程序入口地址的偏移地址(总线读);

6CS=(n*4+2)读入中断服务程序入口地址的段地址(总线读);

5.中断处理子程序

保护现场→开中断→中断处理→恢复现场→中断返回

6.软件中断

软件中断包括中断调用指令和出错中断(溢出、除法错等)

2.3.4最小模式下的总线保持

两条信号线

HOLD总线保持请求),输入,高电平表示外部总线主设备需使用总线;

HLDA总线响应,输出,高电平表示CPU已让出总线使用权。

CPU检测/响应时间:

每个总线周期最后一T的上升沿(既非每一个指令周期,亦非每一个时钟周期T)

1检测到总线请求即给予响应

2CPU处于总线保持期间,不能使用总线,但EU仍可继续工作,总线保持仅对BIU有影响。

3HOLD=1需维持到总线使用完毕,当HOLD=0时,HLDA=0。

在CPU重新使用总线前有一个短小间隔。

2.3.5最大模式下总线请求/响应

用一条信号线作为总线请求/响应

RQ/GT0优先于RQ/GT1–总线请求/响应

过程:

1外部总线使用设备以一个“负脉冲”,表示请求使用总线;

2CPU发一个“负脉冲”,表示总线响应(让出总线使用权);

3外部总线使用设备用完总线后,发一个“负脉冲”,表示总线释放。

最小模式总线请求/响应为电平触发,最大模式为脉冲触发。

2.48086的存储器组织和I/O组织

2.4.18086的存储器组织

20位地址,寻址1MB存储空间地址00000—FFFFFH

1MB空间分为若干段,四个段指针,同时可访问四个段

CS-代码段,SS-堆栈段,DS-数据段,ES-附加段

X86保留地址区域:

1-3FFH中断向量表,实际只用0-2FFH300H为硬盘参数区

FFFF0H-FFFFFH复位入口地址,存放一条无条件段间转移指令

A0000H以上,I/O缓冲区

FFFFFH以下,ROM(BIOS)区

2.4.28086的I/O组织

微处理器通过I/O接口连接I/O设备,每一个接口(接口芯片)占有一个或I/O端口地址

8086(含以上微处理器)用地址低16位作为I/O口地址,最多可访问64K个I/O口

I/O口的访问

I/O编址方式:

独立的I/O编址方式:

存储器和I/O口分别编址,程序中易分出存储器操作/IO操作,需要专用的I/O指令

与存储器对应的I/O编址方式:

I/O地址作为存储器地址的一部分,访问I/O口的操作等同于存储器操作,指令操作类型多,I/O口地址空间基本不受限制,但汇编程序中不易区分存储器操作和I/O操作

第二章小结

1.关于CPU的结构,两个部分,标志

2.关于8086的工作模式,最大最小模式的配置/特点

3.关于8086的总线操作—时序

4.关于8086的中断系统和中断操作

5.关于8086的总线请求/响应

6.关于微处理器的存储器组织和I/O组织