TimeQuest使用步骤.docx

《TimeQuest使用步骤.docx》由会员分享,可在线阅读,更多相关《TimeQuest使用步骤.docx(17页珍藏版)》请在冰豆网上搜索。

TimeQuest使用步骤

Timequesttiminganalyzer使用方法

步骤1:

执行初始编译

在应用时序约束设计之前,创建一个初始数据库:

post-map。

表1-1.执行初始编译

(1)

QuartusII软件GUI

命令行

在Processing菜单上,指向Start,点击StartAnalysis&Synthesis。

quartus_mapfiltrefr

表1-1注释:

1.quartus_map用于创建一个post-map数据库。

2.Analysis&Synthesis阶段生成post-map数据库。

3.也可为初始数据库创建一个post-fit网表。

不过,创建一个post-map网表耗时较少。

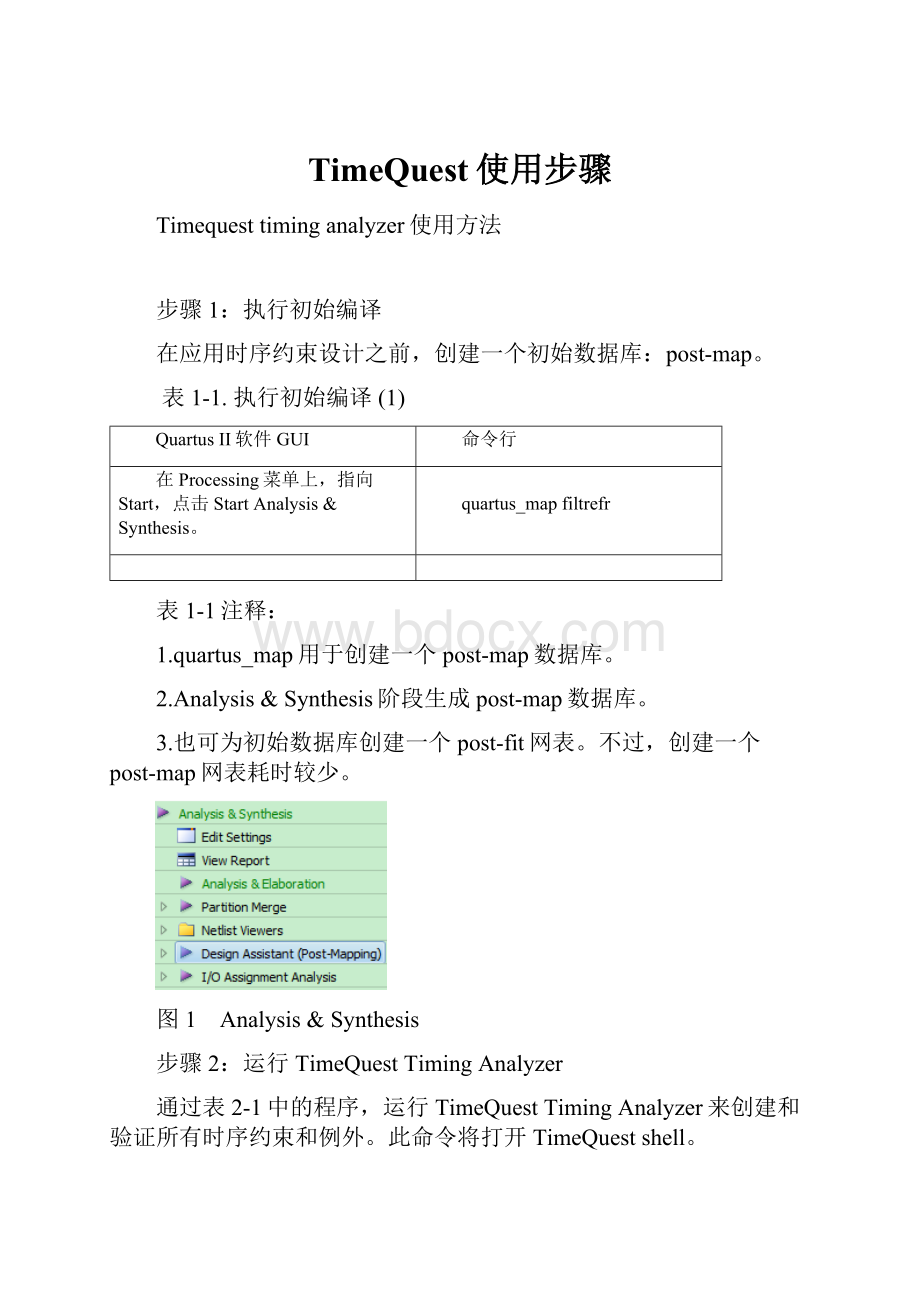

图1 Analysis&Synthesis

步骤2:

运行TimeQuestTimingAnalyzer

通过表2-1中的程序,运行TimeQuestTimingAnalyzer来创建和验证所有时序约束和例外。

此命令将打开TimeQuestshell。

表2-1.运行TimeQuestTimingAnalyzer

QuartusII软件GUI

命令行

在Tools菜单中,单击TimeQuestTimingAnalyzer。

quartus_sta–sr

project_openfir_filter-revisionfiltrefr

当您直接从QuartusII软件中运行TimeQuestTimingAnalyzer时,当前工程将会自动打开。

如果使用GUI,那么当出现下面的消息时,请选择No:

"NoSDCfileswerefoundintheQuartusSettingsFileandfiltref.sdcdoesn'texist.WouldyouliketogenerateanSDCfilefromtheQuartusSettingsFile?

"

图2TimeQuestTimingAnalyzer

步骤3:

创建一个Post-map时序网表

在指定时序要求之前,请创建一个时序网表。

表3-1.创建一个Post-Map时序网表

TimeQuestTimingAnalyzerGUI

TimeQuestTimingAnalyzerConsole

1.在Netlist菜单上,点击CreateTimingNetlist。

出现CreateTimingNetlist对话框。

2.在Inputnetlist中,选择Post-Map。

create_timing_netlist–post_map

注意:

不要在Tasks面板中使用CreateTimingNetlist命令来创建一个post-map时序网表。

默认情况下,CreateTimingNetlist创建一个post-fit数据库。

图3CreateTimingNetlist

图4Inputnetlist

图5waiting

步骤4:

指定时序要求(时钟、IO)

表4-2.创建时钟并分配时钟端口

TimeQuestTimingAnalyzerGUI

TimeQuestTimingAnalyzerConsole

1.在Constraints菜单中,点击CreateClock。

出现CreateClock对话框。

对25MHz时钟指定参数。

单击RUN。

输入:

#createthe25MHz(20ns)clockcreate_clock–period20[get_portsCpsl_Clk25M_i]

2.在Constraints菜单中,点击DrivePLLclocks。

出现DrivePLLclocks对话框,前面指定了PLL基时钟,什么都不选直接单击RUN即可。

默认情况下,如果未使用-waveform选项,那么create_clock命令假设50/50的占空比。

时序包括以下方面:

时钟:

create_clocks/derive_pll_clocks/derive_clocks_uncertainly(手动添加)

IO:

set_input_delay/set_output_delay(此处用延迟0参数,步骤10进行调整)

完成表4-2中显示的程序后,时钟定义完成。

图7Createclock

图8设置参数

图9指定时钟

图10Createclock设置完毕

图11DrivePLLclocks

步骤5:

更新时序网表(timingNetlist)

在您创建时序约束或例外后,通过表5-1中的程序,对时序网表进行更新,将所有时序要求应用到时序网表(新的clk和clkx2时钟约束)。

只要应用了新的时序约束,就必须对时序网表进行更新。

表5-1.更新时序网表(TimingNetlist)

TimeQuestTimingAnalyzerGUI

TimeQuestTimingAnalyzerConsole

在Tasks面板中,双击UpdateTimingNetlist命令。

输入:

update_timing_netlist

图12UpdateTimingNetlist

步骤6:

保存到SDC文件

在为设计指定时钟约束并更新时序网表后,您可以通过表6-1中的程序来选择创建SDC文件。

通过TimeQuestTimingAnalyzerGUI或者在控制台(console)中指定的约束不会自动保存。

因此,Altera建议单独保存利用文本编辑器可以手动编辑的一个goldenSDC文件。

这使您能够根据自身的规范输入注释并组织文件。

如下图:

而不是从TimeQuestGUI的Constraints下拉菜单输入约束:

虽然看起来很相似,但这些约束将直接应用于计时数据库,而不会放入.sdc文件中。

高级用户可能会找到理由这样做,用于修改配置确定参数。

建议初学者打开.sdc文件并从Edit->InsertConstraint访问它们。

表6-1.保存SDC文件

TimeQuestTimingAnalyzerGUI

TimeQuestTimingAnalyzerConsole

1.在Tasks面板中,双击WriteSDCFile命令。

出现WriteSDCFile对话框。

2.在FileName栏输入名称。

输入:

write_sdc-name.sdc r

新的.sdc文件包含"步骤4:

指定时序要求"中定义的时钟约束。

WriteSDCFile命令可以覆盖任何现有的SDC文件。

当这种情况出现时,新的SDC文件没有保持顺序或注释。

(建议拷贝粘贴至SDC文件中)

步骤7:

对初始时时序网表生成时序报告

通过表7-1中的程序定义的时钟,在指定时序约束和更新时序网表后,生成时序报告,这验证了时钟被正确地定义并应用到正确的节点。

1.SDC报告

表7-1.ReportSDC命令

TimeQuestTimingAnalyzerGUI

TimeQuestTimingAnalyzerConsole

在Tasks面板中,双击ReportSDC命令。

输入:

report_sdc

图13生成SDC约束报告(SDCAssignmentsReport)

SDCAssignments报告了在指定设计中包含的所有时序约束和例外。

生成两个报告:

一个用于时钟和一个用于时钟组。

2.clock报告

表7-2.生成报告时钟报告(ReportClocks),总结设计中所有的时钟。

TimeQuestTimingAnalyzerGUI

TimeQuestTimingAnalyzerConsole

在Tasks面板中,双击ReportClocks命令。

输入:

report_clocks

图14时钟报告

3.ClockTransfers报告

通过表7-3中的程序,使用ReportClockTransfers命令生成一个报告来验证所有的时钟到时钟传输都是有效的。

这种报告包含设计中所有的时钟到时钟传输。

表7-3.生成报告时钟传输(ReportClockTransfers)

TimeQuestTimingAnalyzerGUI

TimeQuestTimingAnalyzerConsole

在Tasks面板中,双击ReportClockTransfers命令。

输入:

report_clock_transfers

图15时钟传输报告(ClockTransfersReport)

4. 伪路径设置(两条路径不相关)

本环节只是告诉这个部分伪路径可以作为例外不进行分析。

实际的时序要在做设计时保证其正确。

ClockTransfers报告表明在clk(源时钟)和clkx2(目的时钟)之间存在跨时钟域路径。

共有16条路径,其中clk为源节点提供时钟,clkx2为目的节点提供时钟。

在fir_filter设计中,不必分析clk至clkx2的时钟传输,因为它们是忽略路径。

通过表7-4中的程序声明clk至clkx2的路径为伪路径。

当完成该程序后,TimeQuestTimingAnalyzer表明ClockTransfers报告是过时的。

表7-4.声明伪路径

TimeQuestTimingAnalyzerGUI

TimeQuestTimingAnalyzerConsole

1.在ClockTransfers报告中,在FromClock列选择clk。

2.右击并选择SetFalsePathsBetweenClockDomains。

这个命令表明将所有由clk驱动的源寄存器到由clkx2驱动的目的寄存器之间的路径设为伪路径。

set_false_path-from[get_clocksclk]\

-to[get_clocksclkx2] r

5.set_clock_groups设置(两个时钟域不相关)

另外,也可以使用set_clock_groups命令来声明两个时钟域之间的路径为伪路径。

例如,set_clock_groups-asynchronous-group[get_clocksclk]-group

[get_clocksclkx2]。

该命令表明clk到clkx2以及clkx2到clk的所有路径为伪路径。

此方法是优选的,可以不必每个路径设置。

6. 更新报表

由于您添加了一个新的时序约束,通过表2-14中的程序更新时序网表(timingnetlist)。

表2-14.更新TimingNetlist

TimeQuestTimingAnalyzerGUI

TimeQuestTimingAnalyzerConsole

在Tasks面板中,双击UpdateTimingNetlist命令。

输入:

update_timing_netlistr

在GUI中输入set_false_path后,所有生成的报告面板上都标有"OutofDate",这表明报告面板不包含反映TimeQuestTimingAnalyzer中当前状态的约束或者例外的结果。

要更新报告面板,必须重新生成所有的报告。

在命令行,重新输入命令。

在GUI中,右击报告面板列表中任何过时(out-of-date)的报告,并选择Regenerate或Regenerateall。

步骤8:

保存约束到SDC文件

在指定设计中所有的时钟约束和伪路径后,通过表8-1中的程序将时序约束和例外保存到SDC文件。

(建议拷贝粘贴至SDC文件中)

表8-1.保存约束到SDC文件

TimeQuestTimingAnalyzerGUI

TimeQuestTimingAnalyzerConsole

1.在Tasks面板中,双击WriteSDCFile。

出现WriteSDCFile对话框。

2.在Filename栏,输入-name.sdc.

输入:

write_sdc-name.sdc

1 这一过程覆盖之前所创建的filtref.sdc文件。

如果通过WriteSDCFile命令覆盖SDC,那么在新的SDC文件中移除了定制的格式和注释。

.sdc文件包含时钟约束和伪路径。

步骤9:

执行Timing-Driven全编译

保存约束到SDC文件后,在设计上运行一个全编译以优化布线,从而符合约束。

不过,在开始全编译之前,通过表9-1中的程序将SDC添加到工程中。

表9-1.添加SDC文件到工程中

TimeQuestTimingAnalyzerGUI

TimeQuestTimingAnalyzerConsole

1.在Project菜单中,点击Add/RemoveFilesInProject。

出现Add/RemoveFilesInProject对话框。

2.通过浏览来选择.sdc。

set_global_assignment-nameSDC_FILE\-name.sdc

将SDC添加到工程后,通过表9-2中的程序,在设计上运行一个全编译。

表9-2.运行一个全编译

TimeQuestTimingAnalyzerGUI

TimeQuestTimingAnalyzerConsole

在Processing菜单中,点击StartCompilation。

输入:

quartus_sh--flowcompile-name

完成编译后,TimeQuestTimingAnalyzer在CompilationReport中生成时钟建立和时钟保持的检查总结报告。

步骤10:

在TimeQuest中验证时序

要获得指定路径中详细的时序分析数据,请查看TimeQuestTimingAnalyzer中的时序分析结果。

完全执行布线布局功能(place-and-route)后,运行"步骤2:

运行TimeQuestTimingAnalyzer"中所介绍的TimeQuestTimingAnalyzer,生成一个post-fit时序网表,通过表10-1中的程序,读取SDC文件并更新时序网表来生成关于最新编译的报告。

#1.Summary报告:

表10-1.生成关于LatestCompilation的报告

TimeQuestGUI

TimeQuestTimingAnalyzerConsole

在Tasks面板中,双击所需报告的命令。

例如:

ReportAllSummaries。

create_timing_netlist read_sdcfilref.sdc update_timing_netlistreport_clocks

create_timing_summary-setupcreate_timing_summary-holdcreate_timing_summary-recoverycreate_timing_summary-removalreport_min_pulse_width-nworst10

当双击其中一个报告命令时,CreateTimingNetlist、ReadSDC和UpdateTimingNetlist命令依次在Tasks面板中执行,自动生成时序网表。

#2.Clocksetup报告:

时钟建立检查确保每个寄存器至寄存器的传输不违反SDC指定的时序约束。

通过表10-2中的程序,生成一个时钟建立总结,对设计中的所有时钟进行检查,来验证没有出现违规。

表10-2.生成时钟设置总结检查(ClockSetupSummaryCheck)

TimeQuestTimingAnalyzerGUI

TimeQuestTimingAnalyzerConsole

在Tasks面板中,双击ReportSetupSummary。

输入:

create_timing_summary–setup

Summary(Setup)报告

clkx2时钟没有出现在Summary(Setup)报告中,这是因为clk和clkx2之间所有的时钟路径已经声明是伪路径。

此外,fir_filter设计不包含任何寄存器到寄存器的路径,其中目的寄存器路径由clkx2来驱动。

Summary(Setup)报告中的Slack列表明clk能满足约束,并有11.588ns的余量。

EndPointTNS列是指定时钟域中所有的总负裕量(TNS)的总和。

使用这个值来测量指定时钟域中失败路径的总数。

#3.ClockHold报告:

生成Summary(Setup)报告后,通过表2-21中的程序,生成一个时钟保持检查总结。

表10-3.生成Summary(Hold)Report

TimeQuestTimingAnalyzerGUI

TimeQuestTimingAnalyzerConsole

在Tasks面板中,双击ReportHoldSummary。

输入:

create_timing_summary–hold r

图16Summary(Hold)报告

Summary(Hold)报告表明clk时钟节点符合时序约束,并有0.661ns的余量。

#4.UnconstrainedPaths报告:

在执行全编译之前,通过表10-4中的程序指定所有的时序约束和例外。

这样可以确保Fitter优化设计中的关键路径。

您可以使用ReportUnconstrainedPaths命令来验证已经约束fir_filter设计中的所有路径。

表10-4.指定时序约束和例外

TimeQuestTimingAnalyzerGUI

TimeQuestTimingAnalyzerConsole

在Tasks面板中,双击ReportUnconstrainedPaths。

输入:

report_ucp r

图17UnconstrainedPaths总结报告

#5.Set_input_delay/set_output_delay设置:

UnconstrainedPaths总结报告表明有大量的未约束路径,并详细介绍了这些路径的类型。

要充分约束此设计,利用由TimeQuestTimingAnalyzer所提供的整套SDC约束。

要充分约束fir_filter设计,约束所有的输入和输出端口。

使用SetInputDelay和SetOutput

Delay对话框,或set_input_delay和set_output_delay约束来指定输入和输出延迟值。

由于附加约束应用于设计,通过文本编辑器(例如:

inout_delay.sdc)创建仅包含输入和输出约束的额外SDC。

添加表10-5所示的输入和输出延迟分配到"步骤8:

保存约束到SDC文件"创建的新SDC中。

表 10-5. 输入和输出延迟分配

TheTimeQuestTimingAnalyzerGUI

TheTimeQuestConsole

1.在Constraints菜单中,点击SetInputDelay。

出现SetInputDelay对话框。

2.输入以下内容:

Clockname:

clk

Delayvalue:

2

Targets:

[get_ports{d[0]d[1]d[2]d[3]\

d[4]d[5]d[6]d[7]newtreset}]

3.在Constraints菜单中,点击SetOutputDelay。

出现SetOutputDelay对话框。

4.输入以下内容:

Clockname:

clk

Delayvalue:

1.5

Targets:

[get_ports{yn_out[0]yn_out[1]\yn_out[2]yn_out[3]yn_out[4]yn_out[5]\yn_out[6]yn_out[7]yvalidfollow}]

set_input_delay-clockclk2\

[get_ports{d*newtreset}] r

set_output_delay-clockclk1.5\[get_ports{yn_out*yvalidfollow}] r

记住读取新的约束后更新时序网表,并重新生成UnconstrainedPathsSummary报告。

#6.ReportTiming报告:

通过表10-6中的程序,对设计的时钟或节点生成特定的时序检查报告。

表10-6中的程序生成一个报告,其中clk驱动目的寄存器,并且目的寄存器为 acc:

inst3|result,报告10条最差路径。

表 10-6. 生成ReportTiming报告

TimeQuestTimingAnalyzerGUI

TimeQuestTimingAnalyzerConsole

1.在Tasks面板中,双击ReportTiming。

出现ReportTiming对话框。

2.输入以下内容:

ToClock:

clk

To:

acc:

inst3|result*

Reportnumberofpaths:

10

3.剩下其它的栏使用默认的设置。

report_timing-to_clockclk-to/acc:

inst3|result*-setup-npaths10

图2-10显示了ReportTiming报告。

使用Tasks面板中的ReportTopFailingPaths命令来生成一个报告,该报告详细介绍了设计中的最差的失败路径。

也可以通过菜单设置。

(注:

可编辑下载,若有不当之处,请指正,谢谢!

)