集成电路制造工艺与原理期末答卷.docx

《集成电路制造工艺与原理期末答卷.docx》由会员分享,可在线阅读,更多相关《集成电路制造工艺与原理期末答卷.docx(13页珍藏版)》请在冰豆网上搜索。

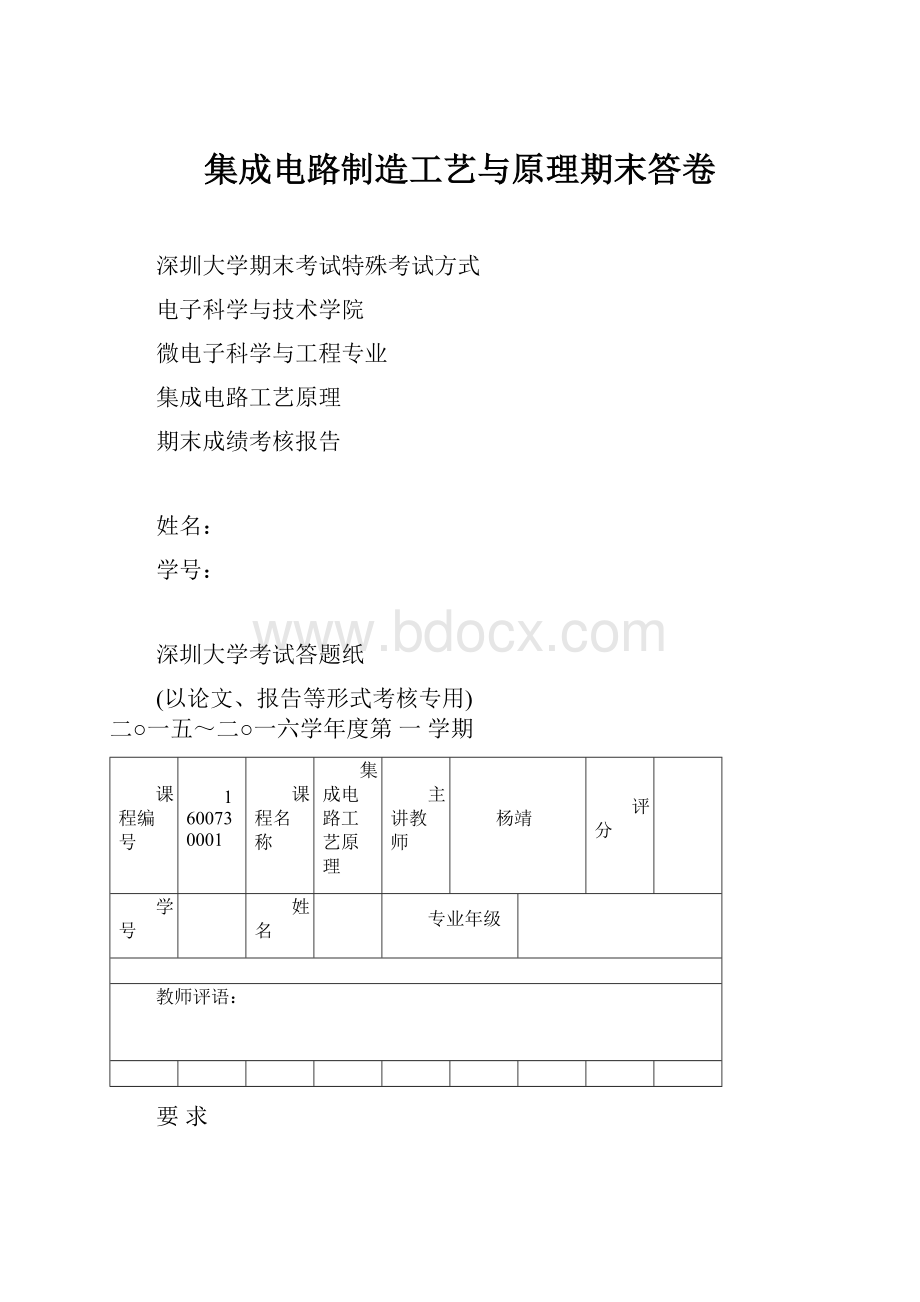

集成电路制造工艺与原理期末答卷

深圳大学期末考试特殊考试方式

电子科学与技术学院

微电子科学与工程专业

集成电路工艺原理

期末成绩考核报告

姓名:

学号:

深圳大学考试答题纸

(以论文、报告等形式考核专用)

二○一五~二○一六学年度第一学期

课程编号

1600730001

课程名称

集成电路工艺原理

主讲教师

杨靖

评分

学号

姓名

专业年级

教师评语:

要求

本报告(作业)必须是完全独立完成,没有抄袭或节选选本课程其他同学的作业,如果确认是抄袭(抄袭和被抄袭)都要承担最终成绩为F的结果。

完成时间:

2016,1,8,17:

00之前

请详细解答以下每道问题!

(回答时请每道题之间留有空隙、题之间清晰分开、每题标明题号;字迹工整、最好打印;图可以手画,但是,必须用规、具,线条清晰规范;坚决杜绝!

卷面脏、乱、草)

•1)举例回答集成电路主要集成了哪些器件?

【5分】

•2)最少给出两个集成电路选用硅半导体的理由。

【5分】

•3)在清洗过程中用到的进入冲洗池的纯净水的电阻(率)在出水口处为多大时说明硅片已经被洗净?

【5分】

•4)常见的半导体的沾污有哪些种类?

【5分】

•5)说明正光刻胶和负光刻胶在曝光过程中的变化和区别。

【5分】

•6)为什么要进行曝光前和曝光后烘焙、怎样提高光刻分辨率?

【10分】

•7)请详细回答,硅片在大气中会自然氧化,从洗净工艺的角度,这属于一种沾污,采用什么工艺即可洗净这种沾污而又不损坏硅?

【10分】

•8)在刻蚀工艺中,由于电极附近鞘层领域的存在,电极附近只有正电荷存在,请用泊松方程解释,在一个周期内电极附近的电场方向总是指向电极。

【10分】

•9)在电极形成工艺中,用到金属Ti,请详尽说明金属Ti的特性,以及金属Ti在集成电路电极结构中的作用!

【15分】

•10)以CMOS的nMOS形成工艺为例来说明,在离子注入工艺中用了多道该工艺步骤,这些步骤有什么目的或起到什么作用。

【15分】

•11)等离子体是现代集成电路工艺中不可或缺的加工手段和材料,根据你的理解和掌握,请就等离子体在集成电路工艺中有哪些应用进行详细的阐述。

【15分】

1)举例回答集成电路主要集成了哪些器件?

【5分】

答:

集成电路主要集成了晶体管、二极管、电阻和电容。

2)最少给出两个集成电路选用硅半导体的理由。

【5分】

答:

(1)硅存量丰富,是地球上第二丰富的元素,占到地壳成分的25%,经合理加工,能够提纯到半导体制造所需的足够高的纯度而消耗更低的成本。

(2)硅熔点高,可以承受更加高温的工艺,相当于放宽了工艺要求。

(3)硅表面会自然生成氧化硅,它是一种高质量、稳定的电绝缘材料,而且能充当优质的化学阻挡层以保护硅不受外部玷污。

生长稳定的薄层氧化硅材料的能力是制造高性能金属-氧化物半导体(MOS)器件的根本。

3)在清洗过程中用到的进入冲洗池的纯净水的电阻(率)在出水口处为多大时说明硅片已经被洗净?

【5分】

答:

在清洗过程中纯净水的电阻率为18MΩ时说明硅片已经被洗净。

4)常见的半导体的沾污有哪些种类?

【5分】

答:

:

(1)颗粒

(2)金属杂质

(3)有机物沾污

(4)自然氧化层

(5)静电释放

5)说明正光刻胶和负光刻胶在曝光过程中的变化和区别。

【5分】

答:

正光刻胶:

曝光区域变得更易溶解,一种正相掩膜版图形出现在光刻胶上。

在曝光过程中正性光刻胶分解,曝光区域易在显影液中被洗去。

负光刻胶:

曝光区域交联硬化,这使曝光的光刻胶难溶于显影液溶剂中,光刻胶没有在显影液中除去。

一种负相的掩模图形形成在光刻胶上。

区别:

负光刻胶在硅片上形成的图形与掩膜板上的图形相反,正光刻胶在硅片上形成的图形与掩膜板上的图形相同。

6)为什么要进行曝光前和曝光后烘焙、怎样提高光刻分辨率?

【10分】

答:

进行曝光前烘焙能解决

(1)光刻胶薄膜发黏并易受颗粒沾污的问题,解决

(2)光刻胶薄膜来自于旋转涂胶的内在应力而导致的粘附性的问题,还能(3)区分曝光和未曝光的光刻胶的溶解差异,最后还有一点就是能够(4)防止光刻胶散发的气体沾污光学系统的透镜。

进行曝光后的烘焙是为了促进关键光刻胶的化学反应,对CADUV光刻胶进行后烘是必须的。

对于基于DNQ化学成分的常规Ⅰ线胶,进行后烘的目的是提高光刻胶的粘附性并减少驻波。

提高光刻分辨率的方法:

增大成像系统数值孔径(NA),缩短曝光波长(λ)以及,降低光学系统工艺因子k的参数。

7)请详细回答,硅片在大气中会自然氧化,从洗净工艺的角度,这属于一种沾污,采用什么工艺即可洗净这种沾污而又不损坏硅?

【10分】

答:

硅片在大气中自然氧化而生成的沾污叫自然氧化层,自然氧化层需要通过使用含HF酸的混合液的清洗步骤去除。

许多清洗方法都是在最后一步时把硅片表面暴露于氢氟酸(HF),以去除硅片表面的自然氧化层。

硅片表面无自然氧化层,是生长高纯外延薄膜和MOS电路栅极超薄氧化物(50埃或更薄)的关键。

HF浸泡之后,硅片表面完全被氢原子终止,在空气中具有很高的稳定性,避免了再氧化。

氢原子终止的硅表面保持着与体硅晶体相同的状态。

此外,干洗等离子体技术也作为工艺设备中的集成预处理步骤去处自然氧化层。

8)在刻蚀工艺中,由于电极附近鞘层领域的存在,电极附近只有正电荷存在,请用泊松方程解释,在一个周期内电极附近的电场方向总是指向电极。

【10分】

答:

由图(a)的A区域可知,A区域内电子跟正电荷都在增加,但单子的增长速度更快,所以对外显负电,所以ρv<0,由式子①②可得电场E<0

由图(a)的B区域可知,B内电子跟正电荷数量相同,对外不显电,即ρv=0,式子①②可得E=0

由图(a)的C区域可知,C内电子跟正电荷都在减少,但电子减得快,所以对外显正电,即ρv>0,由式子①②可得E>0

所以一个周期内电极附近的电场方向总是指向电极。

9)在电极形成工艺中,用到金属Ti,请详尽说明金属Ti的特性,以及金属Ti在集成电路电极结构中的作用!

【15分】

答:

钛的特性:

纯钛是银白色的金属,在金属分类中被划归为稀有轻金属。

钛在元素周期表中属ⅣB族元素,原子序数为22,原子量为47.9,原子半径为0.145nm。

钛的熔点为1660±10℃,其有两种同素异构体,相变点为890~920℃,在转变温度以下为密排六方的α-Ti,在转变温度以上直到熔点之间为体心立方的β-Ti。

钛在化学、物理和机械性能方面有其自己的特点。

与其他金属相比,钛的密度小、比强度高,弹性模量低(常温时为103.4GPa),屈强比高,导热系数小(为0.1507J),热膨胀系数低,无磁性、无毒,耐高、低温,耐腐蚀、与氧的亲和力极强。

金属钛在电路电极结构中的作用:

钛金属在CMOS制作过程的接触形成工艺中可以使硅和随后淀积的导电材料更加紧密地结合起来。

钛的电阻很低,同时能够与硅发生充分反应。

当温度大于700C时,钛跟硅发生反应生成钛的硅化物。

钛和二氧化硅不发生反应,因此这两种物质不会发生化学的键合或者物理聚合。

因此钛能够轻易的从二氧化硅表面除去,而不需要额外掩膜。

钛的硅化物在所有有源硅的表面保留了下来。

(1)金属钛淀积:

一薄阻挡层金属钛衬垫于局部互连沟道的底部和侧壁上。

这一层钛充当了钨与二氧化硅间的粘合剂。

(2)氮化钛淀积:

氮化钛立即淀积于钛金属层的表面充当金属钨的扩散阻挡层。

(3)金属淀积钛阻挡层:

在薄膜区利用物理气相淀积设备在整个硅片表面淀积一薄层钛。

钛衬垫于通孔的底部及侧壁上。

钛充当了将钨限制在通孔中的粘合剂。

(4)溶性阳极和不溶性阳极:

可溶性阳极在电解过程中起补充金属离子和导电的作用,不溶阳极只起导电作用。

最早的不溶性阳极是石墨和铅系阳极上世纪70年代钛阳极作为新技术开始应用在电解和电镀行业。

目前不溶性阳极可分为两大类:

析氯阳极和析氧阳极。

析氯阳极主要用于氯化物电解液体系,电镀过程中阳极有氯气释放出来,因此称为析氯阳极;析氧阳极主要用于硫酸盐、硝酸盐、氢氰酸盐等电解液体系,电镀过程中阳极有氧气释放出来,因此称为析氧阳极。

铅合金阳极析氧阳极,钛阳极根据其表面催化涂层不同分别具有析氧、析氯功能或二者功效兼有。

(5)氯碱工业用钛阳极:

与石墨电极相比,隔膜法生产烧碱,石墨阳极的工作电压为8A/DM2涂层阳极可成倍增加,达17A/DM2。

这样在同样的电解环境下产品可成倍提高,而且所生产品的质量高,氯气纯度高。

(6)电镀用钛阳极:

电镀用不溶性阳极是在钛基体 (网状、板状、带状、管状等)上涂覆具有高电化学催化性能的贵金属氧化物涂层,涂层中含有高稳定性的阀金属氧化物。

新型不溶性钛阳极具有高电化学催化能,析氧过电位比铅合金不溶性阳极低约0.5 V,节能显著,稳定性高,不污染镀液,重量轻,易于更换。

新型不溶性钛阳极的析氧过电位也比镀铂不溶性阳极低,但是寿命却提高1倍以上。

广泛用于各种电镀中作为阳极或者辅助阳极使用,可以替代常规的铅基合金阳极,在相同的条件下,可以降低槽电压,节约电能消耗;不溶性钛阳极在电镀过程中具有良好的稳定性(化学、电化学),使用寿命长。

此阳极广泛用于镀镍镀金、镀铬、镀锌、镀铜等电镀有色金属行业.

10)以CMOS的nMOS形成工艺为例来说明,在离子注入工艺中用了多道该工艺步骤,这些步骤有什么目的或起到什么作用。

【15分】

答:

1.外延生长:

外延层目的是进行轻的P型掺杂(硼)掺杂。

硅片在到达扩散区之前已经有了一个薄的外延层,外延层与衬底有完全相同的晶格结构,只是纯度更高,晶格缺陷更少。

2.原氧化生长:

这一氧化层的主要作用是①保护表面的外延层免受沾污②阻止了在注入过程中对硅片的过度损伤③作为氧化物屏蔽层,有助于控制注入过程中杂质的注入深度

3.第一层掩膜,n阱注入:

在预处理的硅片的上表面涂胶、甩胶、烘焙;后将经过涂胶处理的的硅片每次一片地送入对准与曝光系统,光刻机将特定掩膜的图形直接刻印在涂胶的硅片上;曝光后硅片回到涂胶/显影机中进行显影;显影后再次烘焙,并在转入离子注入区前进行检测。

4.n阱注入(高能):

刻印后的硅片来到离子注入区。

光刻胶图形覆盖了硅片上的特定区域,将其保护起来免于离子注入。

未被光刻胶覆盖的区域允许高能杂质阳离子穿透外延层的上表面(结深约为1μm)。

这一步掺入的杂质为磷。

离子注入机是注入区的主要设备,其主要目的是离化杂质原子,使其加速获得高能(约为200KeV),选出最恰当的元素注入,并聚焦离子成为极窄的一束,最后扫描使硅片不受光刻保护的区域得到均匀掺杂。

5.退火:

在这里硅片经过清洗处理后被放入退火炉。

退火的作用是①裸露在硅片表面生长了一层新的阻挡氧化层②高温使得杂质向硅中移动(扩散)③注入引入的损伤得到修复④杂质原子与硅原子间的共价键被激活,使得杂质原子成为晶格结构中的一部分(电学激活)。

6.第五层掩膜,n-LDD注入:

这一步掩膜步骤的目的是刻印硅片,以得到可以使n型晶体管被注入的光刻胶图形。

其他所有的区域都被光刻胶保护着。

7.n-LDD注入(低能量,浅结):

在未被光刻胶保护的区域,用砷离子进行选择注入。

能量、剂量和结深都明显低于先前的n阱注入步骤。

选择砷而不选择磷的原因是砷的分子量更大,有利于硅表面非晶化,在注入中能够得到更均匀的掺杂深度。

8.第七层掩膜,n+源/漏注入:

这一步掩膜操作目的是定义了要进行注入的n型晶体管区域。

9.n+源/漏注入(中等能量):

这一步中等能量注入进入硅的深度大于LDD的结深。

二氧化硅构成的侧墙阻止了砷杂质侵入狭窄的沟道区。

11)等离子体是现代集成电路工艺中不可或缺的加工手段和材料,根据你的理解和掌握,请就等离子体在集成电路工艺中有哪些应用进行详细的阐述。

【15分】

答:

1. 离子注入

离子注入是一种向硅衬底中引入可控制数量的杂质,以改变其电学性能的方法。

离子注入工在离子注入机内进行,它是半导体工艺中最为复杂的设备之一(见图7-4)。

注入机包含离子源部分,它能从源材料中产生带正电荷的杂质离子。

其中离子源即是产生等离子的部分。

通过电子轰击气体原子,离子源中会产生离子。

电子通常由热钨丝源产生Free-man离子源是一种最常用的电子源:

棒状阴极灯丝装在一个有气体入口的电弧释放室内。

电弧释放室的侧壁是阳极,当气体进入时,灯丝通过大电流,并在阴极和阳极之间加100伏电压,就会在灯丝周围产生等离子体。

高能电子和气体分子发生碰撞,就产生了正离子。

2. 刻蚀工艺

在一个等离子干法刻蚀系统的基本部件包括:

发生刻蚀反应的反应腔、产生等离子体的射频电 源、气体流量控制系统、去除刻蚀生成物和真空系统。

干法等离子体反应器有下面不同的类型:

(1)圆桶式等离子体反应器

圆通式反应器是圆柱形的,在0.1~1托压力下具有几乎完全的化学各向同性刻蚀。

硅片垂直、小间距地装在一个石英舟上。

射频功率加在圆柱两边的电极上。

通常有一个打孔的金属圆柱形刻蚀隧道,它把等离子体限制在刻蚀隧道和腔体壁之间的外部区域。

硅片与电场平行放置使物理刻蚀最小。

等离子体重的刻蚀基扩散到刻蚀隧道内,而等离子体中的带能离子和电子没有进入这一区域。

(2)平板反应器

平板反应器有两个大小和位置对称的平行金属板,一个硅片背面朝下放置于接地的阴极上面,RF信号加在反应器的上电极。

由于等离子体电势总是高于地电势,因而这是一种带能离子进行轰击的等离子体刻蚀模式。

(3)顺流刻蚀系统

等离子体是在大约0.1~1托的压力下,在一个独立的源中产生的,被传输到工艺腔中,并均匀地分布于加热的硅表面。

由于没有离子进行方向性刻蚀,因为顺流刻蚀机采用的是化学刻蚀,是各向同性的。

(4)三极平面反应器

三极平面反应器增加第三个电极来达到控制离子轰击数量的目的。

装置是带两个电源的反应器设置,其中电感耦合的RF源在大约10-13托产生离子和反应基。

低频发生器控制离子的轰击。

(5)离子铣

也称为离子束刻蚀,具有强方向性等离子体的一种物理刻蚀机理。

等离子体通常是由电感耦合RF源或微波产生。

(6)反应离子刻蚀

除了硅片是放置于加RF源的淀积上以及该电极比接地淀积尺寸大大减小以为,RIE与标准的平行板等离子体刻蚀机是类似的。

(7)高密度等离子体刻蚀机

前面用到的标准等离子刻蚀体系是在硅片制造中工作于相对直接产生等离子体的几百毫托的真空度下。

但是对于0.25微米级以下尺寸的几何图形,它难以使刻蚀基高深宽比图形并使刻蚀生成物从高深宽比图形中出来。

而高密度等离子体刻蚀机就是为此而发明的。

3. 淀积

在淀积工艺同样涉及到等离子体,下面是淀积涉及到的等离子的方法:

(1)化学气相沉积(CVD):

化学气相沉积(CVD)是通过气体混合的化学反应在硅片表面沉积 一层固体膜的工艺。

硅片表面及其邻近的区域被加热来向反应系统提供附加的能量。

当化合物 在反应腔中混合并进行反应时,就会发生化学气相淀积过程。

原子或分子会淀积在硅表面形成膜。

Ⅰ.等离子体增强CVD(PECVD):

等离子体增强CVD过程使用等离子体能量来产生并维持CVD反应。

在真空腔中施加射频功率使气体分子分解,就会发生等离子增强CVD并淀积形成膜。

被激发的分子具有化学活性容易与其他原子键合形成粘附在硅片表面的膜。

Ⅱ.高密度等离子CVD(HDPCVD):

高密度等离子是等离子辅助CVD的一个最新发展。

正如名字所言,等离子体在低压下以高密度混合气体的形式直接接触到反应腔中硅片的表面。

他的主要优点是可以在300~400℃较低的淀积温度下,制备出能够填充高深宽比间隙的膜。

(2)物理气相沉积(Physical Vapor Deposition,PVD)技术表示在真空条件下,采用物理方法, 将材料源——固体或液体表面气化成气态原子、分子或部分电离成离子,并通过低压气体(或等离子体)过程,在基体表面沉积具有某种特殊功能的薄膜的技术。

Ⅰ.分子束外延法(MBE):

在超高真空腔内,源材料通过高温蒸发、辉光放电离子化、气体解,电子束加热蒸发等方 法,产生分子束流。

入射分子束与衬底交换能量后,经表面吸附、迁移、成核、生长成膜。

Ⅱ.溅射镀膜:

溅射镀膜是利用气体放电产生的正离子在电场作用下高速轰击阴极靶,使靶材中 的原子(或分子)逸出而淀积到被镀衬底(或工件)的表面,形成所需要的薄膜。

A. 两电极溅射法。

镀膜是在真空溅射槽内进行的,真空度要达10ⅹ10-3以上,充入一定量惰性气体,以材料靶作为阴极,工件作为阳极,在两电极间加上高压使惰性气体电离, Ar+离子被阴极的负高压(一500v)加速,以高速轰击材料靶,从靶面飞溅出来的粒子以足够的速度飞向阳极工件并沉积在其表面上,形成镀层。

B. 三电极溅射

装置就是在以前两电极的装置上附加了第三电极的装置,第三电极作为生成等离子用的电子供应源放出热电子。

而又有时为了放射热电子,使放电稳定化设置了稳定化电极,又称作四电极溅射装置。

C. 磁控管溅射法

是加一个与材料靶表面平行的磁场,由于从靶面飞溅出的高速电子被偏转而不冲击工件,这就克服了由电子冲击工件所引起的温升,同时也促进了惰性气体的离子化