基于FPGA的FIR数字低通滤波器的IP核设计.docx

《基于FPGA的FIR数字低通滤波器的IP核设计.docx》由会员分享,可在线阅读,更多相关《基于FPGA的FIR数字低通滤波器的IP核设计.docx(46页珍藏版)》请在冰豆网上搜索。

基于FPGA的FIR数字低通滤波器的IP核设计

1 系统设计

1.1 设计要求

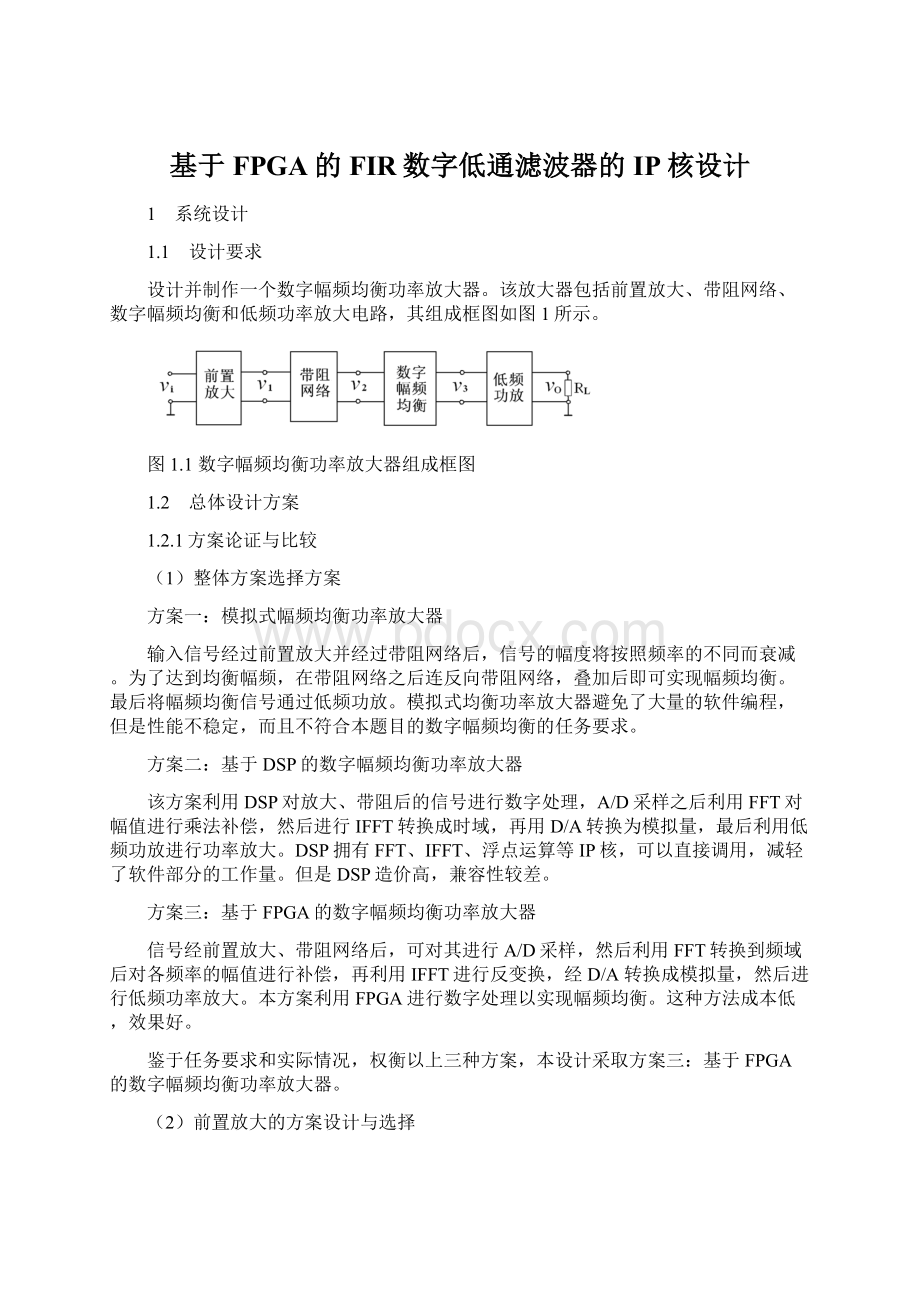

设计并制作一个数字幅频均衡功率放大器。

该放大器包括前置放大、带阻网络、数字幅频均衡和低频功率放大电路,其组成框图如图1所示。

图1.1数字幅频均衡功率放大器组成框图

1.2 总体设计方案

1.2.1方案论证与比较

(1)整体方案选择方案

方案一:

模拟式幅频均衡功率放大器

输入信号经过前置放大并经过带阻网络后,信号的幅度将按照频率的不同而衰减。

为了达到均衡幅频,在带阻网络之后连反向带阻网络,叠加后即可实现幅频均衡。

最后将幅频均衡信号通过低频功放。

模拟式均衡功率放大器避免了大量的软件编程,但是性能不稳定,而且不符合本题目的数字幅频均衡的任务要求。

方案二:

基于DSP的数字幅频均衡功率放大器

该方案利用DSP对放大、带阻后的信号进行数字处理,A/D采样之后利用FFT对幅值进行乘法补偿,然后进行IFFT转换成时域,再用D/A转换为模拟量,最后利用低频功放进行功率放大。

DSP拥有FFT、IFFT、浮点运算等IP核,可以直接调用,减轻了软件部分的工作量。

但是DSP造价高,兼容性较差。

方案三:

基于FPGA的数字幅频均衡功率放大器

信号经前置放大、带阻网络后,可对其进行A/D采样,然后利用FFT转换到频域后对各频率的幅值进行补偿,再利用IFFT进行反变换,经D/A转换成模拟量,然后进行低频功率放大。

本方案利用FPGA进行数字处理以实现幅频均衡。

这种方法成本低,效果好。

鉴于任务要求和实际情况,权衡以上三种方案,本设计采取方案三:

基于FPGA的数字幅频均衡功率放大器。

(2)前置放大的方案设计与选择

方案一:

利用两级OP07放大,OP07放大倍数较高,且元件易购得。

但是OP07在频率大约超过10kHz时增益随频率的变化而变化。

方案二:

AD603与NE5532级联放大。

AD603增益高且稳定,NE5532噪声低,在20Hz-20kHz内增益稳定。

方案选择:

对于任务要求,前置放大器应该放大倍数足够大,在20Hz-20kHz的频带内增益稳定。

另外,鉴于输入信号为有效值小于10mV的小信号,放大器应考虑噪声影响。

方案一中OP07在频率范围内增益不够稳定。

方案二可以获得较高的增益,且噪声较小,增益稳定,符合系统要求。

故选用方案二。

(3)A/D采样电路、D/A转换电路的选择

根据采样定理,和信号的最高频率fsmax=20kHz,求得采样频率fc>2fmax,即fc必须大于40kHz。

对应采样最小时间T=1/fc=25(ns),我们考虑了AD7810和MAX148,经过对性能的分析比较,设计选择了转换速度快,转换精度高的MAX148。

实现IFFT信号模拟输出需要经过D/A转换电路。

选择时考虑了DAC0808和TLC5615两款芯片。

经过实际分析和性能比较,TLC5615可达到10位转换,串行输出,外围电路简单。

所以本系统选择TLC5615。

(5)低频功率放大器电路的设计和选择

功率放大器分为甲类、乙类、甲乙类、丙类、丁类放大器。

通常运用的放大器中效率比较:

η甲<η甲乙<η乙<η丙<η丁

常用的放大器中理想情况下甲类放大器的最高效率为50%,乙类功放的最高频率为78.5%,丙类功放的最高频率可达85%-90%。

但丙类功放要求特殊形式负载,不适用低频,而甲类放大器达不到效率≥60%的系统要求。

所以本系统选择使用乙类放大器作为低频功放。

实际设计时在电路中引入了反馈电路,试性能有了较好的改善。

由于不能使用MOS集成功率模块,本设计使用晶体管二极管和分立的大功率MOS管等元件搭建了引入反馈的乙类推挽功率放大器。

1.2.2系统组成

经过以上各方面的方案论证与分析比较,本设计采用基于FPGA数字幅频均衡功率放大器的方案。

具体系统框图如图1.2所示。

系统分为前置放大器、带阻网络、FPGA数字处理模块、功率放大器模块。

前置放大器使用AD603和NE5532级联放大,阻带网络按题目说明焊接,得到频域值,数字幅频均衡部分使用FPGA技术,先用MAX148进行采样,再利用FFT原理进行幅频补偿,然后进行IFFT,经D/A转换得到信号时域模拟量,再通过功率放大电路完成功率放大。

AD603、NE5532级联MAX148

ViV1V2

FPGA数字处理部分

输出信号VoRLV3

图1.2基于FPGA的数字幅频均衡功率放大器系统框图

2 单元硬件电路设计

2.1 前置放大的设计

题目要求输入信号有效值小于10mV,电压放大倍数不小于400倍,增益

A(dB)=20lg400=52.04(dB),而输入信号频率在20Hz-20kHz,所以要求选用放大器须有足够的增益和增益带宽。

AD603是AD公司推出的一种低噪声且由电压控制的增益放大器。

它提供精确的、可由管脚选择的增益,它的增益是线性变化的,且在温度和电源电压变化时有很高的稳定性,在带宽为9MHz时增益控制电压VG=VC1-VC2(-500mV≤VG≤500mV),理论上增益与增益控制电压的关系:

增益A1(dB)=40VG+30 (从10dB到50dB)

NE5532的增益计算:

增益A2(dB)=20lg(RF/RE)(dB)

级联后增益可达:

A(dB)=(40VG+30)×[20lg(RF/RE)](dB)

而且增益在带宽内可调,信号不失真。

在20Hz-20kHz通频带内衰减小于-1dB。

为了实现输出阻抗为600Ω,在输出端加射级跟随器然后串联600Ω电阻。

前置放大器电路如图2.1所示。

电压增益可由滑动变阻器R4、R3来控制,R4控制VG=VC1-VC2=VC1–0=VC1,R3控制RF/RE,这样即可实现增益可调。

图2.1前置放大电路图

2.2带阻网络的设计

根据题目说明1的带阻网络图搭建带阻电路。

为了达到较高的精度,所用电阻精确度均为千分之一,电感电容也精确度较高。

带阻网络电路如图所示。

信号经过带阻网络后时域变为频域,各个频率对应特定的幅值。

其波特图特性为400Hz左右衰减倍数大,从约400Hz向两侧的衰减倍数逐渐减小。

2.3 A/D采样、D/A转换的电路的设计

A/D部分实现模拟信号到数字信号的转换,ADC采用10位的MAX148。

电路图如图附录4.2所示。

在模拟信号输入端加600Ω接地,然后串接射级跟随器。

D/A部分将数字处理部分得到的数字信号转换成模拟信号,芯片采用10位转换、串行输出的TLC5615,外围电路如图附录4.3所示。

2.4 功率放大器电路的设计

电路如图2.5所示,设计为引入反馈的乙类推挽MOS管功率放大器。

电路的MOS管选用IFR9530和IFR530组成对管使用,NE5532构成电压驱动激励级,功率放大器采用±20V为供电。

因为经过前置放大器、带阻网络、数字幅频均衡后的信号会使Vi放大400倍左右,所以当Vi为5mV时功率放大器前端的输入电压V3约为2V。

功率放大器的负载为RL=8Ω。

功放输出功率:

,电源供给的功率:

,功率放大器的效率为:

为了实现20Hz-20kHz带通,在功放前设置高通RC滤波电路和低通滤波电路。

要求截止频率为20Hz,由系统函数,

,

,

,

令R约1.5kΩ,可得出电容的大概值。

R未算入后续电路的阻抗,所以可对C的值在附近调试。

同理,

,取R=500kΩ,可得到电容C的大概值。

因为R未算入其它阻抗,也可对电容在附近调试。

反馈中电容取120pF。

图2.2低频功率放大器电路图

3 软件设计

FPGA设计用verilog语言对其编程,采用

Quartus的Verilog编译。

程序分为控制部分

和数字处理部分。

3.1 控制部分的程序设计

控制部分的程序主要是分为模数转换和数

模转换两大部分,通过FPGA来控制A/D和D/A

电路进行转换。

3.2数字处理部分的程序设计

数字处理部分的程序主要是完成FFT时频

变换、浮点乘法和IFFT反变换等功能。

3.3主程序流程图

流程图如右图所示。

4系统测试

4.1测试使用的仪器

信号发生器FG708S数字万用表UT-52直流稳压稳流电源JW-4型

数字示波器TDS2012B频率特性测试仪BT3-D

4.2指标测试和测试结果

4.2.1前置放大器部分的指标测试和测试结果

(1)放大倍数和通频带的测试

采用示波器TDS2012B对电压幅值进行测量,当输入信号有效值5mV时幅值为5mV×

=7.07mV,所以信号发生器幅值设为7mV,改变信号频率,在放大电路输出端利用示波器测试不同频率信号对应的输出信号幅值。

表4.1放大倍数测试记录表

Vi

/mV

输出信号幅值Vo/V

平均值

/mV

2020Hz

100Hz

300Hz

500Hz

2k

4k

10k

14k

16k

20k

7

2.98V

2.97V

3.04V

3.18V

3.04V

2.99V

2.98V

2.89V

2.89V

2.95V

3.04V

根据表中数据并计算可知,放大器放大倍数达到428倍,且在带宽内增益稳定。

计算各个频率的增益值:

A=20lg(Vo/Vi),可以证明-1dB通频带包括20Hz-20kHz。

(2)输出电阻的测试

利用公式伏安法对输出电阻进行测量:

表4.2输出电阻测试记录表

Uo1(V)

Uo2(V)

Ri(Ω)

5.84

2.96

593

5.98

2.98

596

5.82

2.90

601

(令RL=600Ω)

求平均数后得:

Ro=595(Ω)

4.2.2 带阻网络部分的指标测试和结果

要求以10kHz时输出的信号V2电压幅度为基准最大衰减≥10dB。

具体结果:

表4.3带阻网络衰减测试记录表

测试数据

频率频率

20Hz20Hz

500Hz

1kHz

5kHz

10kHz10kHz

20kHz20kHz

Vi幅值

0.67V

0.27V

0.336V

0.65V

1.02V

1.23V

由测试结果可知,500Hz的衰减最大,与10kHz相比衰减10.54dB。

4.2.3 数字幅频均衡电路的指标测试和结果

(1)输入阻抗的测试

利用伏安法测试输入阻抗表4.4数字幅频均衡电路输入电阻测试记录表

测试项目

1

2

3

Ui/V

5

5

5

U1/V

9.98

9.97

10.09

U2/V

4.96

4.95

4.93

Ri

597

598

603

对Ri取平均值得:

Ri=599(Ω)

(2)电压幅度波动的测试

先测量10kHz时的电压幅度V0,然后测不同频率的电压幅度Vn,计算20lg[(Vn-V0)/V0]。

表4.6电压幅度波动测试记录表

频率(Hz)

10k

20

1k

5k

15k

20k

Vn(V)

2.10

2.01

2.34

2.23

2.29

2.4

20lg(20lg(Vn/V0)

0

-0.45

1.10

0.47

0.23

1.30

4.2.4 功率放大器部分的指标和测试结果

(1)输出功率和输出波形的测试表4.7输出功率测试记录表

Uo