西电fpga第一次上机报告解析.docx

《西电fpga第一次上机报告解析.docx》由会员分享,可在线阅读,更多相关《西电fpga第一次上机报告解析.docx(13页珍藏版)》请在冰豆网上搜索。

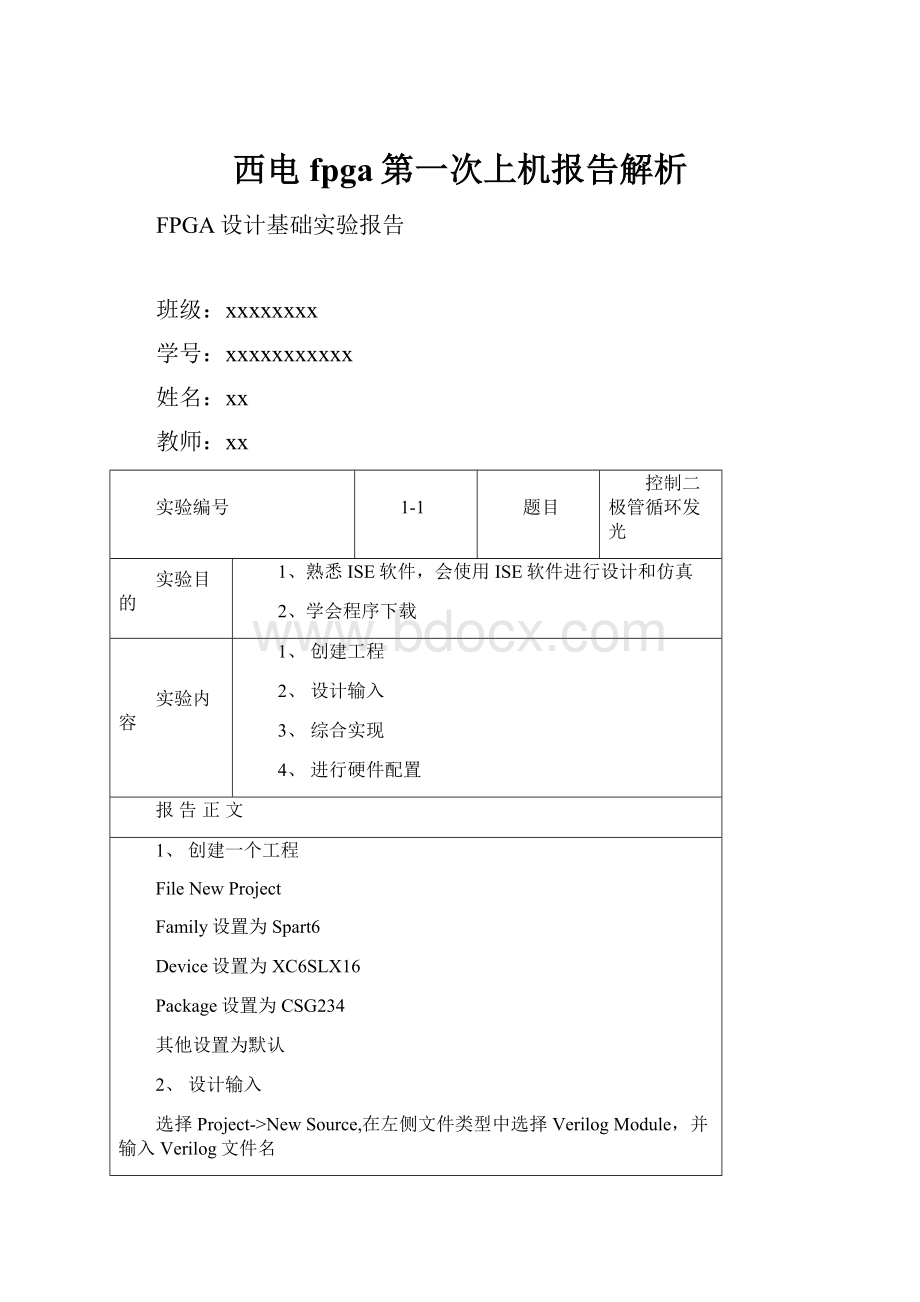

西电fpga第一次上机报告解析

FPGA设计基础实验报告

班级:

xxxxxxxx

学号:

xxxxxxxxxxx

姓名:

xx

教师:

xx

实验编号

1-1

题目

控制二极管循环发光

实验目的

1、熟悉ISE软件,会使用ISE软件进行设计和仿真

2、学会程序下载

实验内容

1、创建工程

2、设计输入

3、综合实现

4、进行硬件配置

报告正文

1、创建一个工程

FileNewProject

Family设置为Spart6

Device设置为XC6SLX16

Package设置为CSG234

其他设置为默认

2、设计输入

选择Project->NewSource,在左侧文件类型中选择VerilogModule,并输入Verilog文件名

单击Next进入模块定义窗口,在其中填入模块端口定义。

这一步也可以略过,在源代码中再行添加

具体代码略。

3、综合与实现

在工程管理区的view中选择Implementation,然后在过程管理区双击Synthesize-XST,就可以开始综合过程

展开Synthesize-XST,选择ViewRTLSchematic,可以查看综合出的RTL电路图

添加用户约束文件:

选择Project->NewSource,在弹出的对话框中,左侧文件类型选中ImplementationConstraintsFile,右侧填写文件名。

在工程管理区内选择EditConstraints编辑约束文件,使用Nexys3开发板实现Gate2工程的用户约束文件代码如下所示。

综合完成后,下一个步骤就是实现(Implementation)。

实现主要分为3个步骤:

翻译(Translate)、映射(Map)与布局布线(place&Route)。

在ISE中,执行实现过程,会自动执行翻译、映射和布局布线过程:

也可单独执行。

在过程管理区双击ImplementDesign选项,就可以自动完成实现的3个步骤。

4、器件配置

器件配置是FPGA开发最关键的一步,只有将HDL代码下载到FPGA芯片中,才能进行调试并最终实现相应的功能。

首先我们必须生成能下载到硬件中的二进制比特文件。

双击过程管理区的GenerateProgrammingFile,ISE就会为设计生成相应的二进制比特文件。

然后利用USB-MiniUSB缆线,来为开发板提供电源和数据下载。

我们只需上网下载免费的DigilentAdept软件,即可快速实现Nexys3开发板上FPGA的配置。

用USB-MiniUSB缆线连接开发板和PC,打开开发板的电源开关。

然后启动DigilentAdept软件。

系统开始自动连接FPGA设备,成功检测到设备后,会显示出JTAG链上所用芯片。

在Browse中找到之前生成的设计的二进制比特文件,并点击旁边的Program按钮,软件就开始对FPGA进行配置。

配置成功后,下面的状态栏会显示ProgrammingSuccessful。

至此,器件配置成功,我们就可以在器件上验证预期的设计有没有很好的得以实现。

实验编号

1-2

题目

控制二极管循环发光

实验目的

1、熟悉ISE软件,会使用ISE软件进行设计和仿真

2、学会程序下载

实验内容

1、创建工程

2、设计输入

3、综合实现

4、进行硬件配置

报告正文

步骤1略

2、设计输入

选择Project->NewSource,在左侧文件类型中选择VerilogModule,并输入Verilog文件名。

单击Next进入模块定义窗口,在其中填入模块端口定义。

这一步也可以略过,在源代码中再行添加

具体代码略。

3、综合与实现

在工程管理区的view中选择Implementation,然后在过程管理区双击Synthesize-XST,就可以开始综合过程

展开Synthesize-XST,选择ViewRTLSchematic,可以查看综合出的RTL电路图

添加用户约束文件:

选择Project->NewSource,在弹出的对话框中,左侧文件类型选中ImplementationConstraintsFile,右侧填写文件名。

在工程管理区内选择EditConstraints编辑约束文件,使用Nexys3开发板实现Gate2工程的用户约束文件代码如下所示。

综合完成后,下一个步骤就是实现(Implementation)。

实现主要分为3个步骤:

翻译(Translate)、映射(Map)与布局布线(place&Route)。

在ISE中,执行实现过程,会自动执行翻译、映射和布局布线过程:

也可单独执行。

在过程管理区双击ImplementDesign选项,就可以自动完成实现的3个步骤。

4、器件配置

器件配置是FPGA开发最关键的一步,只有将HDL代码下载到FPGA芯片中,才能进行调试并最终实现相应的功能。

首先我们必须生成能下载到硬件中的二进制比特文件。

双击过程管理区的GenerateProgrammingFile,ISE就会为设计生成相应的二进制比特文件。

然后利用USB-MiniUSB缆线,来为开发板提供电源和数据下载。

我们只需上网下载免费的DigilentAdept软件,即可快速实现Nexys3开发板上FPGA的配置。

用USB-MiniUSB缆线连接开发板和PC,打开开发板的电源开关。

然后启动DigilentAdept软件。

系统开始自动连接FPGA设备,成功检测到设备后,会显示出JTAG链上所用芯片。

在Browse中找到之前生成的设计的二进制比特文件,并点击旁边的Program按钮,软件就开始对FPGA进行配置。

配置成功后,下面的状态栏会显示ProgrammingSuccessful。

至此,器件配置成功,我们就可以在器件上验证预期的设计有没有很好的得以实现。