计算机组成原理常考计算题.docx

《计算机组成原理常考计算题.docx》由会员分享,可在线阅读,更多相关《计算机组成原理常考计算题.docx(26页珍藏版)》请在冰豆网上搜索。

1.机器数字长为8位(含1位符号位),当X=-127(十进制)时,其对应的二进制表示,(X)原表示,(X)反表示,(X)补表示,(X)移表示分别是多少?

二进制表示为-01111111

[X]原=11111111[X]反=10000000[X]补=10000001[X]移=00000001

2.已知x=0.1011,y=-0.0101,求x+y=?

x-y=?

[x]补=00.1011[x]补=00.1011

+[y]补=11.1011+[-y]补=00.0101

00.011001.0000

x+y=+0.0110x-y产生溢出

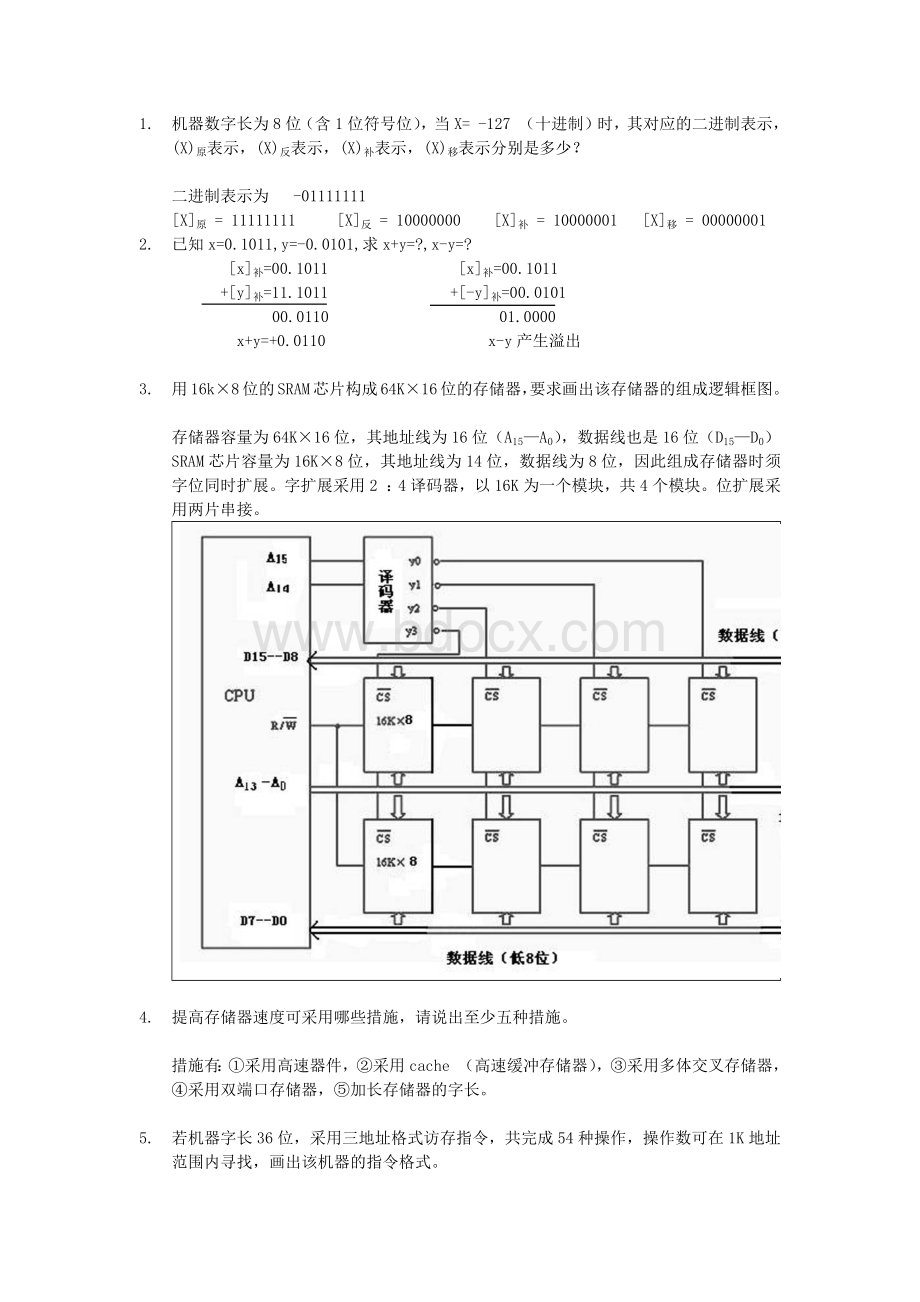

3.用16k×8位的SRAM芯片构成64K×16位的存储器,要求画出该存储器的组成逻辑框图。

存储器容量为64K×16位,其地址线为16位(A15—A0),数据线也是16位(D15—D0)

SRAM芯片容量为16K×8位,其地址线为14位,数据线为8位,因此组成存储器时须字位同时扩展。

字扩展采用2:

4译码器,以16K为一个模块,共4个模块。

位扩展采用两片串接。

4.提高存储器速度可采用哪些措施,请说出至少五种措施。

措施有:

①采用高速器件,②采用cache(高速缓冲存储器),③采用多体交叉存储器,④采用双端口存储器,⑤加长存储器的字长。

5.若机器字长36位,采用三地址格式访存指令,共完成54种操作,操作数可在1K地址范围内寻找,画出该机器的指令格式。

操作码需用6位,操作数地址码需用10位。

格式如下

6101010

OP

D1

D2

D3

OP:

操作码6位

D1:

第一操作数地址,10位

D2:

第二操作数地址,10位

D3:

第三操作数地址,10位

6.举例说明存储器堆栈的原理及入栈、出栈的过程。

所谓存储器堆栈,是把存储器的一部分用作堆栈区,用SP表示堆栈指示器,MSP表示堆栈指示器指定的存储器的单元,A表示通用寄存器。

入栈操作可描述为(A)→MSP,(SP-1)→SP

出栈操作可描述为(SP+1)→SP,(MSP)→A

7.试画出三总线系统的结构图。

8.若显示工作方式采用分辨率为1024×768,颜色深度为3B,桢频为72Hz,计算刷新存储器带宽应是多少?

解:

刷存所需带宽=分辨率×每个像素点颜色深度×刷新速率,故刷存带宽为:

1024×768×3B×72/s=165888KB/s=162MB/s.

1.求十进制数-113的原码表示,反码表示,补码表示和移码表示(用8位二进制表示,并设最高位为符号位,真值为7位)。

原码11110001

反码10001110

补码10001111

移码00001111

2.某机指令格式如图所示:

OP

X

D

15109870

图中X为寻址特征位,且X=0时,不变址;X=1时,用变址寄存器X1进行变址;X=2时,用变址寄存器X2进行变址;X=3时,相对寻址。

设(PC)=1234H,(X1)=0037H,

(X2)=1122H,请确定下列指令的有效地址(均用十六进制表示,H表示十六进制)

(1)4420H

(2)2244H(3)1322H(4)3521H(5)6723H

(1)0020H

(2)1166H(3)1256H(4)0058H(5)1257H

3.将十进制数354转换成二进制数、八进制数、十六进制数和BCD数。

(1)(354)10=(162.A)16

(2)(354)10=(101100010.1010)2

(3)(354)10=(542.5)8

(4)(354)10=(001101010100.011000100101)BCD

4.浮点数格式如下:

1位阶符,6位阶码,1位数符,8位尾数,请写出浮点数所能表示的范围(只考虑正数值)。

最小值2-111111×0.00000001

最大值2111111×0.11111111

5.现有一64K×2位的存储器芯片,欲设计具有同样存储容量的存储器,应如何安排地址线和数据线引脚的数目,使两者之和最小。

并说明有几种解答。

设地址线x根,数据线y根,则

2x·y=64K×2

若y=1x=17

y=2x=16

y=4x=15

y=8x=14

因此,当数据线为1或2时,引脚之和为18

共有2种解答

6.异步通信方式传送ASCII码,数据位8位,奇校验1位,停止位1位。

计算当波特率为4800时,字符传送的速率是多少?

每个数据位的时间长度是多少?

数据位的传送速率是多少?

每个字符格式包含十个位,因此字符传送速率

4800波特/10=480字符/秒

每个数据位时间长度T=1/4800=0.208ms

数据位传送速率8×480=3840位/秒

7.已知某8位机的主存采用半导体存储器,地址码为18位,采用4K×4位的SRAM芯片组成该机所允许的最大主存空间,并选用模块条形式,问:

(1)若每个模块条为32K×8位,共需几个模块条?

(2)每个模块条内有多少片RAM芯片?

(3)主存共需多少RAM芯片?

CPU需使用几根地址线来选择各模块?

使用何种译码器?

(218×8)/(32k×8)=8,故需8个模块

(32k×8)/(4k×4)=16,故需16片芯片

共需8×16=128片芯片

为了选择各模块,需使用3:

8译码器

即3根地址线选择模条。

8.画出中断处理过程流程图。

中断处理过程流程图如图C2.1所示。

取指令

执行指令

否

中断

是

响应中断

关中断,即“中断屏蔽”置位

中

断

转移到中断服务子程序

周

期

保存CPU现场

中

设备服务

断

服

恢复CPU现场

务

子

程

开中断,即“中断屏蔽”复位

序

图C2.1

1.#已知:

X=0.1011,Y=-0.0101,求[X/2]补,[X/4]补[-X]补,[Y/2]补,[Y/4]补,[-Y]补

解:

[X]补=0.1011[X/2]补=0.01011[X/4]补=0.001011[-X]补=1.0101

[Y]补=1.1011[Y/2]补=1.11011[Y/4]补=1.111011[-Y]补=0.0101

2.机器数字长8位(含1位符号位),若机器数为81(十六进制),当它分别表示原码、补码、反码和移码时,等价的十进制数分别是多少?

原码:

-1,补码:

-127,反码:

-126,移码:

+1。

3.用16K×16位的SRAM芯片构成64K×32位的存储器。

要求画出该存储器的组成逻辑框图。

所需芯片总数(64K×32)÷(16K×16)=8片因此存储器可分为4个模块,每个模块16K×32位,各模块通过A15、A14进行2:

4译码

4.#指令格式如下所示,其中OP为操作码,试分析指令格式特点:

15107430

OP

源寄存器

目标寄存器

解:

(1)操作数字段OP可以指定64种基本操作

(2)单字长(16位)二地址指令

(3)源寄存器和目标寄存器都是通用寄存器(各指定16个),所以是RR型指令,两个操作数均在通用寄存器中

(4)这种指令结构常用于算术/逻辑运算类运算指令,执行速度最快。

5.CPU结构如图所示,其中一个累加寄存器AC,一个状态条件寄存器和其它四个寄存器,各部分之间的连线表示数据通路,箭头表示信息传送方向。

(1)标明图中四个寄存器的名称。

(2)简述指令从主存取到控制器的数据通路。

(3)数据在运算器和主存之间进行存/取访问的数据通路。

图C3.1

答:

(1)a为数据缓冲寄存器DR,b为指令寄存器IR,c为主存地址寄存器AR,d为程序计数器PC;

(2)PC→AR→主存→缓冲寄存器DR→指令寄存器IR→操作控制器

(3)存储器读:

M→DR→ALU→AC存储器写:

AC→DR→M

6.总线的一次信息传送过程大致分哪几个阶段?

若采用同步定时协议,画出读数据的同步时序图。

分五个阶段:

总线请求,总线仲裁,寻址(目的地址),信息传送,状态返回(或错误报告)。

时序图:

7.举出三种中断向量产生的方法。

(1)由编码电路实现,直接产生。

(2)由硬件产生一个“位移量”,再加上CPU某寄存器里存放的基地址

(3)向量地址转移法:

由优先级编码电路产生对应的固定地址码,其地址中存放的是转移指令,通过转移指令可以转入设备各自的中断服务程序入口。

8.CD-ROM光盘的外缘有5mm的范围因记录数据困难,一般不使用,故标准的播放时间为60分钟。

请计算模式2情况下光盘存储容量是多少?

解:

扇区总数=60×60×75=270000

模式2存放声音、图像等多媒体数据,其存储容量为

270000×2336/1024/1024=601MB

.若浮点数X的二进制存储格式为(41360000)16,求其32位浮点数的十进制值。

解:

将16进制数展开后,可得二进制格式为

01000001001101100000000000000000

↑

S阶码8位尾数23位

指数e=阶码-127=10000010-01111111=00000011=(3)10

包括隐藏位1的尾数1.M=1.01101100000000000000000=1.011011

于是有X=(-1)S×1.M×2e=+(1.011011)×23=+1011.011=(11.375)10

2.已知X=-0.01111,Y=+0.11001,求[X]补,[-X]补,[Y]补,[-Y]补,X+Y=?

X-Y=?

解:

[X]补=1.10001[-X]补=0.01111[Y]补=0.11001[-Y]补=1.00111

[X]补=11.