8051系统设计.docx

《8051系统设计.docx》由会员分享,可在线阅读,更多相关《8051系统设计.docx(62页珍藏版)》请在冰豆网上搜索。

8051系统设计

第七章8051单片机系统扩展与接口技术

第一节8051单片机系统扩展概述

一、8051扩展系统的结构

单片机芯片内具有CPU、ROM、RAM、定时器/计数器及I/O口等,因此一个单片机芯片事实上已经是一台名符其实的计算机了。

但由于单片机内部资源毕竟有限,在许多较为复杂的技术应用中,其内部资源可能不够用。

这时,必须对单片机系统进行资源性扩展,从而构成一个功能更强的单片机系统。

MCS—51单片机属总线结构型单片机,系统扩展通常采用总线结构形式。

所谓总线,就是指连接系统中各扩展部件的一组公共信号线。

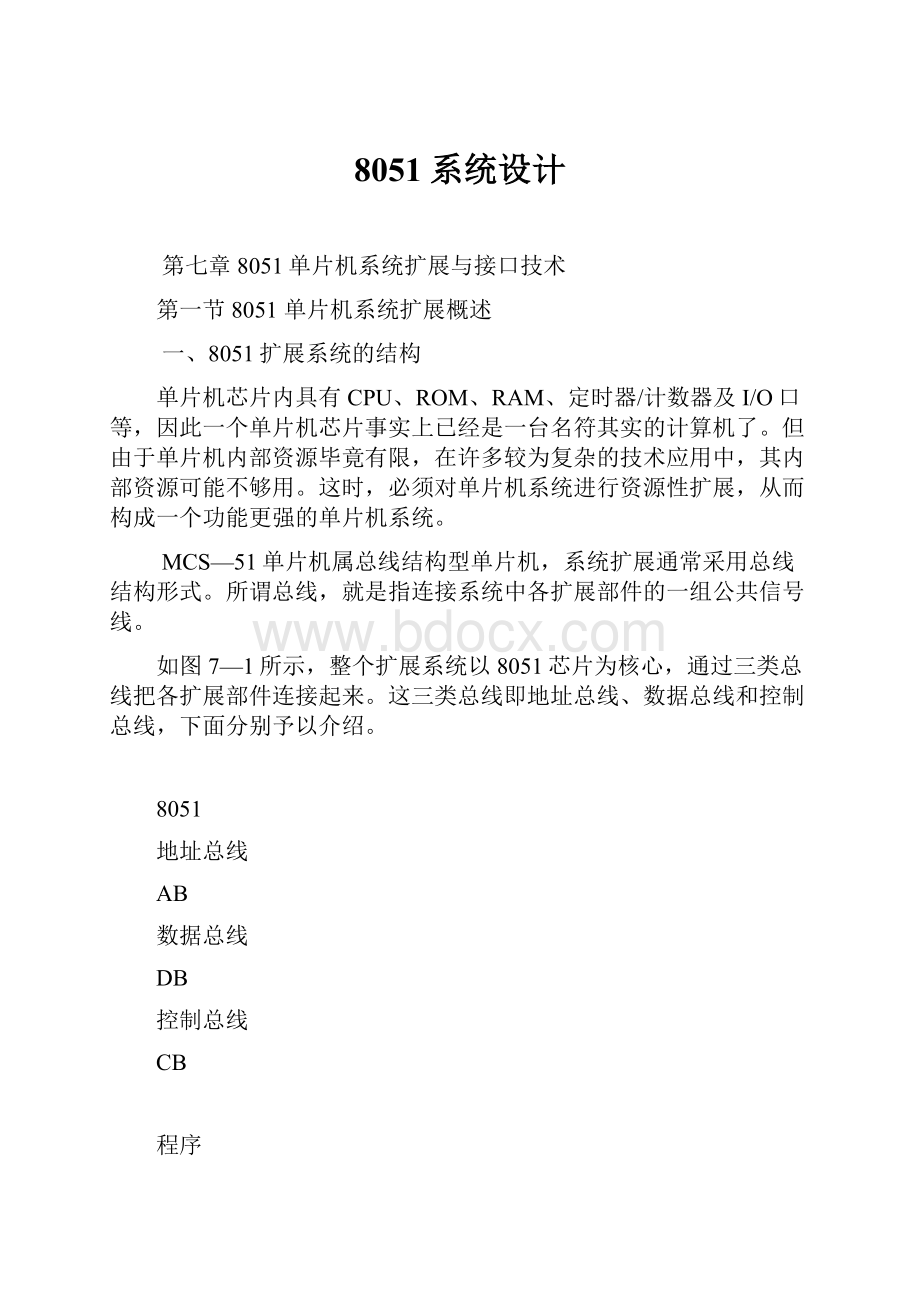

如图7—1所示,整个扩展系统以8051芯片为核心,通过三类总线把各扩展部件连接起来。

这三类总线即地址总线、数据总线和控制总线,下面分别予以介绍。

8051

地址总线

AB

数据总线

DB

控制总线

CB

程序

存储器

I/O接口

I/O接口

数据

存储器

I/O设备

I/O设备

图7—18051芯片系统扩展结构图

1.地址总线(AddressBus,简写为AB)

地址总线可传送单片机送出的地址信号,用于访问外部存储器单元或I/O端口。

地址总线是单向的,地址信号只是由单片机向外发出。

地址总线的数目决定了可直接访问的存储器单元的数目。

例如N位地址,可以产生2N个连续地址编码,因此可访问2N个存储单元,即通常所说的寻址范围为2N个地址单元。

MCS—51单片机有十六位地址线,因此存储器展范围可达216=64KB地址单元。

挂在总线上的器件,只有地址被选中的单元才能与CPU交换数据,其余的都暂时不能操作,否则会引起数据冲突。

2.数据总线(DataBus,简写为DB)

数据总线用于在单片机与存储器之间或单片机与I/O端口之间传送数据。

单片机系统数据总线的位数与单片机处理数据的字长一致。

例如MCS—51单片机是8位字长,所以数据总线的位数也是8位。

数据总线是双向的,即可以进行两个方向的数据传送。

3.控制总线(ControlBus,简写为CB)

控制总线实际上就是一组控制信号线,包括单片机发出的,以及从其它部件送给单片机的各种控制或联络信号。

对于一条控制信号线来说,其传送方向是单向的,但是由不同方向的控制信号线组合的控制总线则表示为双向的。

总线结构形式大大减少了单片机系统中连接线的数目,提高了系统的可靠性,增加了系统的灵活性。

此外,总线结构也使扩展易于实现,各功能部件只要符合总线规范,就可以很方便地接入系统,实现单片机扩展。

整个扩展系统以8051芯片为核心,通过总线把各扩展部件连接起来,其情形有如各扩展部件”挂”在总线上一样。

扩展器件包括ROM、RAM和I/O接口电路等。

因为扩展是在单片机芯之外进行的,因此通常把扩展的ROM称之为外部ROM,把扩展RAM称之为外部RAM。

二、单片机扩展的实现

8051单片机扩展系统的总线结构如图7—2所示:

MCS—51单片机的P0口,是一个地址/数据分时复用口。

即在某些时钟周期时,P0口传送低八位地址,这时ALE为高电平有效;而在其它时钟周期时传送数据,这时ALE为无效的低电平。

利用P0口输出低八位地址和ALE同时有效的条件,即可用锁存器(图中74LS373)把低八位地址锁存下来。

所以系统的低八位地址是从锁存器输出端送出的.而P0口本身则又可直接传送数据。

高八位地址总线则是直接由P2口组成的。

CPU的每一条控制信号引脚的组合,即构成了控制总线。

PSEN

RD

WR

8051

P2

ALE

EAP0

控制线

8

高8位地址

(A15—A8)

DGQ

74LS373

88低8位地址

(A7—A0)

8

数据线

(D7—D0)

图7─2单片机扩展构造图

图7—2中74LS373为8D锁存器芯片,其引脚分布及功能如图7—3所示:

VccQ7D7Q6D6Q5D5D4Q4

20191817161514131211

DiQi

74LS373

12345678910GE

EQ0D0Q1D1Q2D2Q3D3GND

图7-374LS373芯片引脚功能图

表7—174LS373功能表

E

G

功能

0

1

取数Qi=Di

0

0

保持Qi不变

1

X

输出高阻

由表7—1可知,将74LS373芯片E端接地,G端接8051的ALE信号,数据输入端D7—D0接P0口,输出端Q7—Q0接外部程序存储器A7—A0端,当ALE为高电平时,将PO口送出地址低八位信号送373内部锁存器保存;当ALE为低电平时,74LS373输出低8位地址信息不变。

因此当P0口用来作数据总线时,不会造成地址低8位信息的丢失。

P2口始终输出高8位信号,故无需加地址锁存电路。

第二节单片机外部存储器扩展

单片机外部存储器扩展思路是:

根据单片机访问外部存储器的基本时序及工作速度,选择相应的存储器芯片,并根据系统对存储器容量的要求,选择容量合适的存储器芯片。

一般来说,这二种选择都应留有余量。

一、单片机访问外部程序存储器基本时序

单片机在对外部程序存储器进行读操作时,地址信号、数据信号以及有关控制信号基本时序如图7—4:

T机

S1S2S3S4S5S6

P1P2P1P2P1P2P1P2P1P2P1P2

ALE有效有效

PSEN有效

ROM锁存读数据RAM

P0

A7—A0D7—D0A7—A0

P2A15—A8A15—A8A15—A8

图7—4MCS—51单片机访问外部程序存储器基本时序图

由图7—4可得,CPU访问外部ROM时,先从P0口输出低八位地址信号,当CPU从ALE端输出有效信号时,可将低八位地址信号送至锁存器373保存并输出,这样由P2口和锁存器共同输出十六位地址信号,然后CPU从PSEN端线输出读外部ROM数据有效低电平信号选通外部ROM,这时CPU就可通过P0口从数据总线上读入外部ROM指定单元送出的数据。

由此可见,ROM芯片必须在PSEN有效期内将指定单元的数据送到数据总线上,否则CPU将读不到数据。

二、单片机访问外部数据存储器时序

前述读ROM操作是为了取得指令码,该机器周期称为取指周期,而对外部RAM的访问称为指令的执行周期,单片机访问外部数据存储器包括读,写两类操作。

有关信号基本时序如图7—5所示(以读操作为例):

第一个T机第二个T机

S1S2S3S4S5S6S1S2S3S4S5S6

P1P2P1P2P1P2P1P2P1P2P1P2P1P2P1P2P1P2P1P2P1P2P1P2

ALE

有效有效有效

PSEN有效

RD有效

ROM丢弃RAM锁存读数据RAM

P0

A7—A0A7—A0D7—D0A7—A0

P2

A15—A8A15—A8A15——A8

图7─5单片机访问外部数据存储器基本时序图

由图7—5可得,CPU访问外部RAM时,先将P0口输出的低八位地址信号在ALE有效时送至锁存器373保存并输出,这样由P2口和锁存器共同输出十六位地址信号,然后RD端输出读外部数据存储器有效低电平信号选通外部RAM,这样CPU就可通过P0口从数据总线上读入外部RAM指定单元送出的数据。

由此可见,外部RAM芯片必须在RD有效期内将指定单元的数据送到数据总线上,否则CPU将读不到数据。

CPU对外部RAM进行写操作时,除用WR信号取代RD信号以外,其余工作时序与读操作相同。

三、程序存储器的扩展

(一)只读存储器概述

程序存储器扩展使用的元件是只读存储器芯片,简称ROM。

根据编程方式的不同,ROM可分为掩膜ROM,一次性可编程ROM(PROM),紫外光可擦、电可写ROM(EPROM)及电可擦写ROM(EEPROM)。

其中掩膜ROM写入的内容,由ROM生产厂家根据用户程序清单,在生产时ROM就写入,用户不能改写。

EPROM可反复写入并用紫外线擦除。

EEPROM可进行在线写入或编程,但写人速度较慢。

同时目前EEPROM市场价格高于前三种ROM价格。

(二)典型只读存储器芯片

INTEL公司只读存储器芯片(EPROM)的产品有:

2716,2732,2764,27128,27256,27512等。

系列数字27后面的数据除以8即为该芯片的K数。

如:

27256为32K容量。

2764EPROM是具有28根引脚的双列直插式器件,图7—6给出其引脚排列图。

2764具有8K(1024×8)字节容量,共需要有13根地址线(213=8192)A12—A0进行寻址,加上8条数据线D7—D0、一条片选信号线CE、一条数据输出选通线OE、一条编程电源线Vpp及编程脉冲输入线PGM,另外有一条正电源线UCC及接地线GND,其第26号引脚为NC,使用时应接高电平。

在非编程状态时UPP及PGM端应接高电平。

其中片选信号为保证多片存贮系统中地址的正确选择,数据输出选通线保证时序的配合,编程电源线及编程脉冲输入线可实现程序的电编程。

Upp128Ucc

A12227PGM

A7326NC

A6425A8

A5524A9

A4623A11

A37276422OE

A2821A10

A1920CE

A01019D7

D01118D6

D11217D5

D21316D4

GND1415D3

图7─62764引脚排列图

2764芯片由单一正5V电源供电,工作电流100mA,维持电流50mA,读出时间最大为250ns,是一种高速大容量EPROM存贮器。

其工作方式见表7—2。

表7—22764工作方式选择

引脚

方式

CE

(20)

OE

(22)

PGM

(27)

Upp

(1)

Ucc

(28)

输出

D7—D0

读

0

0

+5V

+5V

+5V

数据输出

维持

+5V

X

X

+5V

+5V

高阻态

编程

0

X

0

Upp

+5V

数据输入

编程校验

0

0

5V

Upp

+5V

数据输出

编程禁止

+5V

X

X

Upp

+5V

高阻态

注:

2764的编程电源Upp随型号不同而异,典型的有25V,21V,12V等。

(三)程序存储器扩展的实现:

实现程序存储器扩展,需要考虑以下三点:

1.依据系统容量,并参考市场价格,选定合适的芯片。

2.确定所扩展存储器的地址范围,并依照选定芯片的引脚功能和排列图,将引脚接入单片机系统中。

3.考虑所选芯片的工作速度,尤其当主机晶振频率提高时,注意芯片工作速度是否能满足主机读取指令的时限。

现仍以2764为例,说明电路连接方法如下:

A7—A0:

接373锁存器输出(低八位地址)

A12—A8:

接P2口P2.4—P2.0(高五位地址)

D7—D0:

接P0口P0.7—P0.0(数据线)

CE:

接地。

(也可根据编址情况接地址译码输出电路)

OE:

接CPU的PSEN端

GND:

接地

PGM,VPP,VCC:

共同联接到EC(+5V)端

8051芯片扩展外部8KEPROM电路如图7—7所示。

由于CE=0,2764芯片的地址范围:

0000H—1FFFH(8KB)。

另外还有三根未接入的高地址线,共可形成8个地址段。

PSEN

P2.4-0

8051

ALE

EA

P0

A7-A0A12-A8OE

VCC

2764VPPPGM

D7-D0GNDCE

GQ7-Q0

74LS373

D7-D0EGND

+5v

图7—7扩展8K字节EPROM的8051系统

四、数据存储器的扩展

(一)数据存储器概述

数据存储器亦称随机存取存储器,简称RAM。

用于暂存各类数据。

它的特点是:

1.在系统运行过程中,随时可进行读写两种操作。

2.一旦掉电,原存入数据全部消失(成为随机数)。

RAM按半导体工艺可分为MOS型和双极型两种。

MOS型集成度高、功耗低、价格便宜,但速度较慢。

而双极型的则正好相反。

在单片机系统中使用的是MOS型随机存储器。

RAM按工作方式可分为静态(SRAM)和动态(DRAM)二种。

对静态RAM,只要电源供电,存在其中的信息就能可靠保存。

而动态RAM需要周期性地刷新才能保存信息。

动态RAM集成密度大、功耗低、价格便宜,但需要增加刷新电路。

在单片机中多使用静态RAM。

(二)典型随机存储器芯片:

INTEL公司62系列MOS型静态随机存储器产品有:

6264,62128,62256,62512等。

另外还有容量仅2K的6116。

(现已不生产)。

图7—8给出6264引脚图。

NC128Vcc

A12227WE

A7326CE2

A6425A8

A5524A9

A4623A11

A37626422OE

A2821A10

A1920CE1

A01019IO7

IO01118IO6

IO11217IO5

IO21316IO4

GND1415IO3

图7—86264引脚图

6264是容量为8K×8的静态随机存储器芯片,采用CMOS工艺制作,由单一+5V电源供电,额定功耗200mW,典型存取时间为200ns,28线双列插式封装。

表7─3为6264的操作方式:

表7—36264的操作方式

管脚

操作方式

CE1

(20)

CE2

(26)

OE

(22)

WE

(27)

IO7—IO0

(11—13,15—19)

未选中(掉电)

+5V

X

X

X

高阻

未选中(掉电)

X

0

X

X

高阻

输出禁止

0

+5V

+5V

+5V

高阻

读

0

+5V

0

+5V

DOUT

写

0

+5V

+5V

0

DIN

(三)数据存储器扩展的实现:

与程序存储器扩展一样,数据存储器扩展也要考虑下列三点:

1.依据系统容量,并考虑市场价格,选定合适的芯片。

2.确定所扩展存储器的地址范围,并依照选定芯片的引脚功能和排列图,将引脚接入单片机系统中。

3.所选RAM芯片工作速度匹配(但数据存储器工作速度要求可略低于程序存储器)。

现以6264为例,说明8051与6264芯片的连接方法如下:

A7—A0:

接373锁存器输出端Q7—Q0(低八位地址)

A12—A8:

接P2.4—P2.0(高五位地址)

IO7—IO0:

接P0.7—P0.0(数据线)

OE:

接CPURD端

WE:

接CPUWR端

CE1:

接地

CE2:

接+EC

GND:

接地

VCC:

接EC(+5V)

A7-0

6264

D7-0

A12-8

OECE1

WE

CE2

P0

ALE

8051

P2.4-0

RD

WR

EA

Di373Qi

G

1

P2.7

P2.6

P2.5

+5V

图7—9扩展8K字节RAM的8051系统

同理,图7—9中6264的地址范围是:

0000H—1FFFH(8KB)。

应当指出,上述存储器扩展后的地址范围存在地址重叠现象,如图7—9的6264扩展线路中由于高三位地址P2.7,P2.6,P2.5(A15,A14,A13)的状态不影响6264芯片工作,故上述6264芯片实际地址的编址情况如下:

P2.7

P2.6

P2.5

P2.4

P2.3

P2.2

P2.1

P2.0

P0.7

P0.6

P0.5

P0.4

P0.3

P0.2

P0.1

P0.0

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

X

X

X

0

0

0

0

0

0

0

0

0

0

0

0

0

·

·

·

·

·

·

·

·

X

X

X

1

1

1

1

1

1

1

1

1

1

1

1

1

显然其地址范围是:

0000H—1FFFH,2000H—3FFFH…E000H—FFFFH。

即地址有重叠。

解决上述地址重叠的办法是:

通过译码电路(这里用或门),使不参与寻址的其余地址线P2.7.P2.6.

P2.5=000时,其输出才为0,并接到CE1端。

如图7—9中虚线所连接的那样,这时0000H—1FFFH为其唯一的地址空间,读者可自行验证。

若打算使扩展的存储器芯片有不同的地址空间,只要重新设计译码电路即可,例如将上述存储器芯片的地址空间改为

2000H—3FFFH,此时当P2.7,P2.6,P2.5=001时,CE1=0,即令CE1=P2.7+P2.6+P2.5即可。

第三节单片机输入输出(I/O)口扩展及应用

一、I/O接口技术概述

在计算机应用中,为实现CPU与种类繁多的外部设备进行数据交换,需要通过输入输出接口实现CPU与外设的联接。

一般来说,在数据的I/O传送中,接口电路主要具有以下功能:

1.速度协调

由于CPU与外设工作速度的差异,在实现I/O数据传送时需要通过一些应答信号来协调工作,例如CPU在确认外设已做好接收数据准备时才发送数据。

2.数据锁存

由于CPU的工作速度很快,数据在数据总线上停留时间很短,因此从总线上读取数据的输出接口电路,需设置数据锁存器,暂存所传送的数据,然后再传送给外设。

3.三态输出

由于计算机的数据总线是公共通道,因此挂在数据总线上的输入设备接口必须具有三态输出功能,使得该外设地址没有被CPU选中时,与总线处于高阻隔离状态。

否则各个不同I/O输入设备在随机同时发送数据时,会产生数据冲突。

二、单片机简单I/O口应用及扩展

由于单片机本身接口资源有限,事实上只有P1口和系统不使用的P3口端线才能真正作为I/O口使用,因此在实际应用中经常需要通过扩展技术来增加I/O口的数量。

1.I/O口的直接应用

直接应用单片机本身的I/O口资源完成简单的I/O数据传送.例如用单片机P1口和P3口的某些口线进行输入输出操作.常用指令有

MOVP1,A;

MOVA,P1;

SETBP1.0等。

在运用Px(P0—P3)口直接进行输入输出操作时,应注意以下几点:

(1)Px口作为输出口使用时,P0口须外加上拉电阻,而P1,P2,P3口内部已有上拉电阻,无须外加上拉电阻。

(2)Px口作为输入口使用时,在进行输入操作前应先往各口线写入”1”(复位后Px各口线内锁存器均置”1”)。

(3)P0,P2口多用来传送地址信号,P0口又作为数据总线被系统频繁调用,故很少用P0,P2口作为输入输出口使用。

(4)P3口某些口线作第二功能使用时,其余口线可作为输入输出口线使用。

2.单片机简单I/O口扩展

所谓简单I/O口,是指不能通过编程耒改变其输入或输出性质的I/O接口。

(1)简单输入接口扩展

利用具有三态输出功能的缓冲电路即可实现。

例如利用典型芯片74LS244组成的简单输入接口扩展。

该芯片具有两个四位的三态缓冲器,CE为选通信号,.低电平有效。

即:

CE=1,输出端呈高阻状态;

CE=0,输出端与对应输入端信号相同。

图7—10是74LS244的引脚功能图,图7—11给出了用74LS244作为简单输入接口扩展联接图:

74LS

244

CE1──VccP0

1A1──CE2

2Y4─74LS─1Y1

1A2──2A48051P2.4P2.5P2.6P2.7

2Y3─244─1Y2RD

1A3──2A3

2Y2──1Y3

1A4──2A3≥1≥1≥1≥1

2Y1──2Y4

GND──2A1

CE1.2

244

CE1.2

244

CE1.2

244

CE1.2

244

图7—1074LS244引脚功能图

外设D

外设A外设B外设C

图7—1174LS244作简单输入接口扩展联接图

由图7—11可得,当P2.4=0时,外设A即被选通,故接口地址为EFFFH,(“0”为有效选通信号时,其余位与选通无关位均取”1”)。

同理外设B、外设C、外设D接口地址分别为DFFFH、BFFFH、7FFFH。

3.简单输出接口扩展

扩展简单输出接口仅用D锁存器即可实现。

例如可利用74LS377八D锁存器进行简单输出接口扩展。

图7─12为74LS377引脚及功能图,表7─4给出了74LS377真值表,图7—13是运用377进行输出接口扩展联接:

G━━VCC表7—474LS377真值表

1Q━━8QGCKDQ

1D━74LS━8D

2D━━7D1XXQ(不变)

2Q━377━7Q0↑11

3Q━━6Q0↑00

3D━━6DX0XX

4D━━5D

4Q━━5Q

GND━━CKDiQi

DQi

CK

图7─1274LS377引脚及功能图

P0

8051

WR

CKD7-0

G377

Q7-0

CKD7-0

G377

Q7-0

CKD7-0

G377

Q7-0

CKD7-0

G377

Q7-0

P2.4P2.5P2.6P2.7

外设A外设B外设C外设D

图7─1374LS377作简单输出接口扩展联接图

由表7—4可得,当G=0,且CK上升沿到来后,Qi=Di;当G=1,Q状态维持不变。

图7—13中利用WR的上升沿将P0口数据送入对应锁存器,从而输出数据。

在上述简单接口扩展中,由于外设与CPU之间没有“应答”信号联系,各口功能单一,输入输出不能复用,因此无法适应外设与CPU进行信息交换的实际需要。

PC3─140─Vcc