冯诺依曼结构和哈佛结构.docx

《冯诺依曼结构和哈佛结构.docx》由会员分享,可在线阅读,更多相关《冯诺依曼结构和哈佛结构.docx(37页珍藏版)》请在冰豆网上搜索。

冯诺依曼结构和哈佛结构

计算机基本知识计算机体系结构分类

两种典型的结构:

冯·诺依曼结构

哈佛体系结构

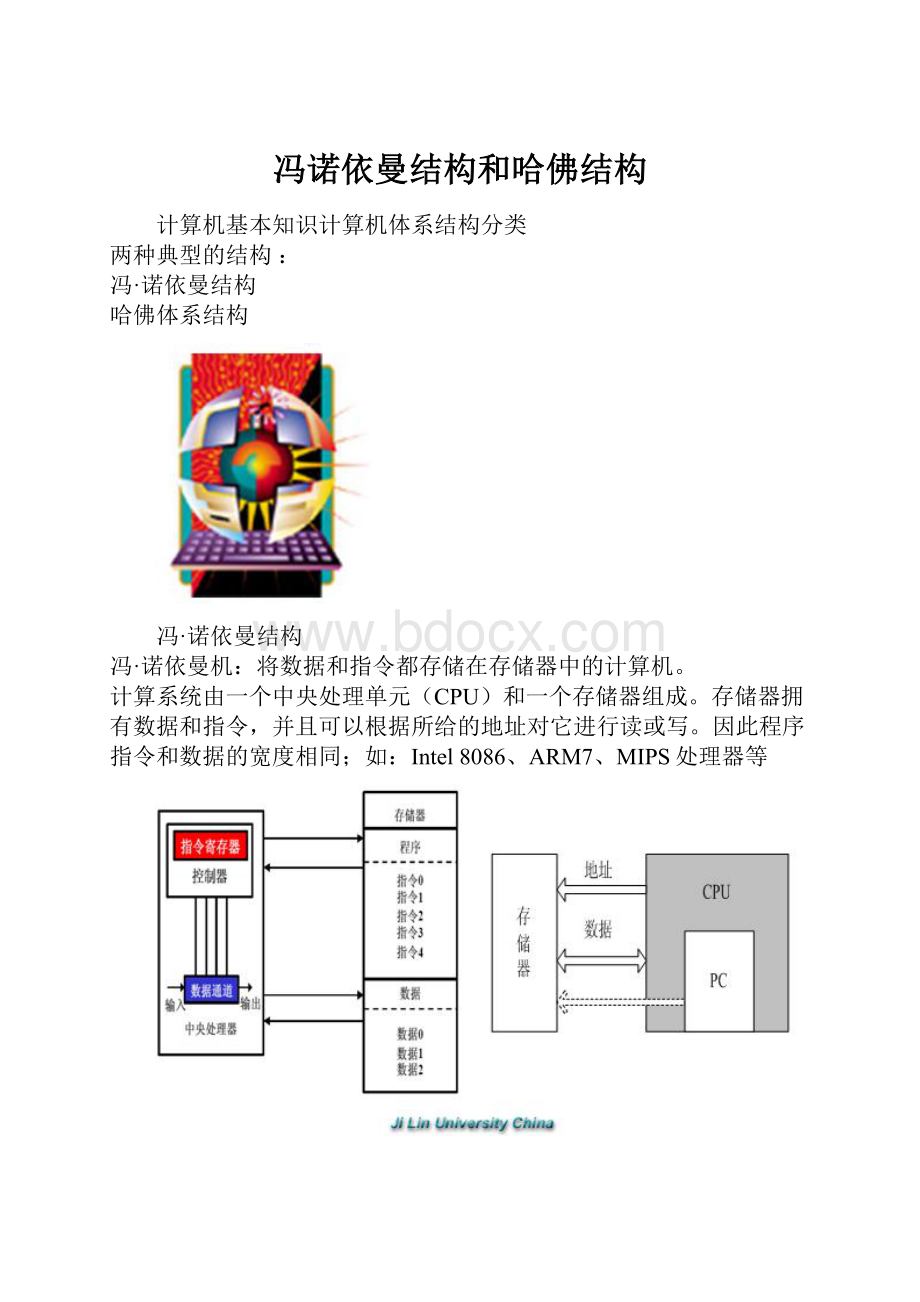

冯·诺依曼结构

冯·诺依曼机:

将数据和指令都存储在存储器中的计算机。

计算系统由一个中央处理单元(CPU)和一个存储器组成。

存储器拥有数据和指令,并且可以根据所给的地址对它进行读或写。

因此程序指令和数据的宽度相同;如:

Intel8086、ARM7、MIPS处理器等

哈佛体系结构

哈佛机:

为数据和程序提供了各自独立的存储器。

程序计数器只指向程序存储器而不指向数据存储器,这样做的后果是很难在哈佛机上编写出一个自修改的程序。

独立的程序存储器和数据存储器为数字信号处理提供了较高的性能。

指令和数据可以有不同的数据宽度;具有较高的效率;如摩托罗拉公司的MC68系列、Zilog公司的Z8系列、ARM10系列等

ARM 7使用冯·诺依曼体系结构。

ARM9使用哈佛体系结构。

ARM公司简介

ARM是AdvancedRISCMachines的缩写,它是一家微处理器行业的知名企业,该企业设计了大量高性能、廉价、耗能低的RISC(精简指令集)处理器。

1985年第一个ARM原型在英国剑桥诞生。

公司的特点是只设计芯片,而不生产。

它提供ARM技术知识产权(IP)核,将技术授权给世界上许多著名的半导体、软件和OEM厂商,并提供服务。

有ARM7/ARM9等多个版本。

除了一些Unix图形工作站外,大多数ARM核心的处理器都使用在嵌入领域。

ARM,既可以认为是一个公司的名字,也可以认为是对一类微处理器的通称,还可以认为是一种技术的名字。

ARM处理器的应用

到目前为止,基于ARM技术的微处理器应用约占据了32位嵌入式微处理器75%以上的市场份额。

全球80%的GSM/3G手机、99%的CDMA手机以及绝大多数PDA产品均采用ARM体系的嵌入式处理器。

“掌上计算”相关的所有领域皆为其所主宰。

主要应用:

消费类电子,无线、图像应用开放平台、存储、自动化、智能卡、SIM卡等。

ARM处理器的三大特点:

耗电少功能强、16位/32位双指令集、众多合作伙伴。

各ARM体系结构版本

ARM体系结构从最初开发到现在有了很大的改进,并仍在完善和发展。

为了清楚地表达每个ARM应用实例所使用的指令集,ARM公司定义了6种主要的ARM指令集体系结构版本,以版本号V1~V6表示

ARM版本Ⅰ:

V1版架构

该版架构只在原型机ARM1出现过,只有26位的寻址空间,没有用于商业产品。

其基本性能有:

基本的数据处理指令(无乘法);

基于字节、半字和字的Load/Store指令;

转移指令,包括子程序调用及链接指令;

供操作系统使用的软件中断指令SWI;

寻址空间:

64MB(226)。

ARM版本Ⅱ:

V2版架构

该版架构对V1版进行了扩展,例如ARM2和ARM3(V2a)架构。

包含了对32位乘法指令和协处理器指令的支持。

版本2a是版本2的变种,ARM3芯片采用了版本2a,是第一片采用片上Cache的ARM处理器。

同样为26位寻址空间,现在已经废弃不再使用。

V2版架构与版本V1相比,增加了以下功能:

乘法和乘加指令;

支持协处理器操作指令;

快速中断模式;

SWP/SWPB的最基本存储器与寄存器交换指令;

寻址空间:

64MB。

ARM版本Ⅲ:

V3版架构

ARM作为独立的公司,在1990年设计的第一个微处理器采用的是版本3的ARM6。

它作为IP核、独立的处理器、具有片上高速缓存、MMU和写缓冲的集成CPU。

变种版本有3G和3M。

版本3G是不与版本2a向前兼容的版本3,版本3M引入了有符号和无符号数乘法和乘加指令,这些指令产生全部64位结果。

V3版架构(目前已废弃)对ARM体系结构作了较大的改动:

寻址空间增至32位(4GB);

当前程序状态信息从原来的R15寄存器移到当前程序状态寄存器CPSR中(CurrentProgramStatusRegister);

增加了程序状态保存寄存器SPSR(SavedProgramStatusRegister);

增加了两种异常模式,使操作系统代码可方便地使用数据访问中止异常、指令预取中止异常和未定义指令异常。

;

增加了MRS/MSR指令,以访问新增的CPSR/SPSR寄存器;

增加了从异常处理返回的指令功能。

ARM版本Ⅳ:

V4版架构

V4版架构在V3版上作了进一步扩充,V4版架构是目前应用最广的ARM体系结构,ARM7、ARM8、ARM9和StrongARM都采用该架构。

V4不再强制要求与26位地址空间兼容,而且还明确了哪些指令会引起未定义指令异常。

指令集中增加了以下功能:

符号化和非符号化半字及符号化字节的存/取指令;

增加了T变种,处理器可工作在Thumb状态,增加了16位Thumb指令集;

完善了软件中断SWI指令的功能;

处理器系统模式引进特权方式时使用用户寄存器操作;

把一些未使用的指令空间捕获为未定义指令

ARM版本Ⅴ:

V5版架构

V5版架构是在V4版基础上增加了一些新的指令,ARM10和Xscale都采用该版架构。

这些新增命令有:

带有链接和交换的转移BLX指令;

计数前导零CLZ指令;

BRK中断指令;

增加了数字信号处理指令(V5TE版);为协处理器增加更多可选择的指令;

改进了ARM/Thumb状态之间的切换效率;

E---增强型DSP指令集,包括全部算法操作和16位乘法操作;

J----支持新的JAVA,提供字节代码执行的硬件和优化软件加速功能。

ARM版本Ⅵ:

V6版架构

V6版架构是2001年发布的,首先在2002年春季发布的ARM11处理器中使用。

在降低耗电量地同时,还强化了图形处理性能。

通过追加有效进行多媒体处理的SIMD(SingleInstruction,MultipleData,单指令多数据)功能,将语音及图像的处理功能提高到了原型机的4倍。

此架构在V5版基础上增加了以下功能:

THUMBTM:

35%代码压缩;

DSP扩充:

高性能定点DSP功能;

JazelleTM:

Java性能优化,可提高8倍;

Media扩充:

音/视频性能优化,可提高4倍

ARM处理器系列

ARM公司开发了很多系列的ARM处理器核,目前最新的系列已经是ARM11。

ARM7、ARM9、ARM9E和ARM10为4个通用处理器系列。

每一个系列提供一套相对独特的性能来满足不同应用领域的需求。

ARM7系列

ARM9系列

ARM9E系列

ARM10E系列

ARM11系列

SecurCore系列

Intel的Xscale

Intel的StrongARM

ARM7微处理器系列

低功耗的32位RISC处理器,冯·诺依曼结构。

极低的功耗,适合便携式产品。

具有嵌入式ICE-RT逻辑,调试开发方便。

3级流水线结构。

能够提供0.9MIPS的三级流水线结构

代码密度高,兼容16位的Thumb指令集。

对操作系统的支持广泛,包括WindowsCE、Linux、PalmOS等。

指令系统与ARM9系列、ARM9E系列和ARM10E系列兼容,便于用户的产品升级换代。

主频最高可达130MIPS。

主要应用领域:

工业控制、Internet设备、网络和调制解调器设备、移动电话等多种多媒体和嵌入式应用。

ARM7TDMI微处理器

4种类型:

ARM7TDMI、ARM7TDMI-S、ARM720T、ARM7EJ。

ARM7TMDI是目前使用最广泛的32位嵌入式RISC处理器,属低端ARM处理器核。

注:

“ARM核”并不是芯片,ARM核与其它部件如RAM、ROM、片内外设组合在一起才能构成现实的芯片。

ARM7TDMI内部结构

组成:

处理器核、用于边界扫描的TAP控制器、在线仿真器ICE。

双向数据总线D[31:

0]被分割成单向输入和输出总线,以便于与外部存储器兼容。

ARM7TDMI的模块和内核框图

ARM7TDMI功能信号图

ARM9微处理器系列

ARM9系列微处理器在高性能和低功耗特性方面提供最佳的性能。

5级整数流水线,

哈佛体系结构。

支持32位ARM指令集和16位Thumb指令集。

全性能的MMU,支持WindowsCE、Linux、PalmOS等多种主流嵌入式操作系统。

支持数据Cache和指令Cache,具有更高的指令和数据处理能力。

主要应用:

无线设备、仪器仪表、安全系统、机顶盒、高端打印机、数码照相机和数码摄像机。

3种类型:

ARM920T、ARM922T和ARM940T。

ARM9E微处理器系列

单一处理器内核提供微控制器、DSP、Java应用系统的解决方案。

支持DSP指令集。

5级整数流水线,指令执行效率更高。

支持32位ARM指令集和16位Thumb指令集。

支持VFP9浮点处理协处理器。

全性能的MMU,支持WindowsCE、Linux、PalmOS等多种主流嵌入式操作系统。

MPU支持实时操作系统。

支持数据Cache和指令Cache,

主频最高可达300MIPS。

主要应用:

下一代无线设备、数字消费品、成像设备、工业控制、存储设备和网络设备等领域。

3种类型:

ARM926EJ-S、ARM946E-S和ARM966E-S。

ARM10E微处理器系列

与同等的ARM9比较,在同样的时钟频率下,性能提高了近50%,功耗极低。

支持DSP指令集。

6级整数流水线,指令执行效率更高。

支持32位ARM指令集和16位Thumb指令集。

支持VFP10浮点处理协处理器。

全性能的MMU,支持WindowsCE、Linux、PalmOS等多种主流嵌入式操作系统。

支持数据Cache和指令Cache。

主频最高可达400MIPS。

内嵌并行读/写操作部件。

主要应用:

下一代无线设备、数字消费品、成像设备、工业控制、通信和信息系统等领域。

3种类型:

ARM1020E、ARM1022E和ARM1026EJ-S。

SecurCore微处理器系列

专为安全需要而设计,提供了完善的32位RISC技术的安全解决方案。

灵活的保护单元,以确保操作系统和应用数据的安全。

采用软内核技术,防止外部对其进行扫描探测。

可集成用户自己的安全特性和其他协处理器。

主要应用:

对安全性要求较高的应用产品及应用系统,如电子商务、电子政务、电子银行业务、网络和认证系统等领域。

4种类型:

SecurCoreSC100、SecurCoreSC110、SecurCoreSC200和SecurCoreSC210。

Xscale处理器

基于ARMv5TE体系结构的解决方案,是一款全性能、高性价比、低功耗的处理器。

支持16位的Thumb指令和DSP指令集。

已使用在数字移动电话、个人数字助理和网络产品等场合。

Xscale处理器是Intel目前主要推广的一款ARM微处理器

ARM系列流水线比较

ARM系列性能比较

ARM处理器结构

ARM和Thumb状态

RISC技术

流水线技术

超标量技术

ARM和Thumb状态

V4版以后有:

(1)32位ARM指令集

(2)16位Thumb指令集,功能是ARM指令集的功能子集。

ARM7TDMI核以后,T变种的ARM微处理器有两种工作状态:

(1)ARM状态

(2)Thumb状态。

当ARM微处理器执行32位的ARM指令集时,工作在ARM状态;

当ARM微处理器执行16位的Thumb指令集时,工作在Thumb状态

Thumb技术介绍

ARM7体系结构被广泛应用的时候,嵌入式控制器的市场仍然由8位、16位处理器占领。

这些产品不能满足高端应用。

这些应用需要32位RISC处理器的性能和更优于16位CISC处理器的代码密度。

为了解决代码密度的问题,ARM增加了T变种。

Thumb从32位ARM指令集中抽出来的36条指令格式,可重新编成16位的操作码。

在运行时,16位的Thumb指令又由处理器解压成32位指令。

Thumb核有2套独立的指令集,它使设计者得到ARM32位指令性能的同时,又能享有Thumb指令集产生的代码方面的优势,在性能和代码大小之间取得平衡。

和ARM指令集相比,Thumb指令集具有以下的局限:

完成相同的操作,Thumb指令通常需要更多的指令,因此在对系统运行时间要求苛刻的场合,ARM指令集更为合适。

Thumb指令集没有包含进行异常处理时需要的一些指令,因此在异常中断时,还是需要使用ARM指令,这种限制决定了Thumb指令需要与ARM指令配合使用。

ARM与Thumb状态转换

在程序的执行过程中,微处理器可以随时在两种工作状态之间切换,并且该转变不影响处理器的工作模式和相应寄存器中的内容。

进入Thumb状态:

当操作数寄存器的状态位(位[0])为1时,执行BX指令。

进入ARM状态:

当操作数寄存器的状态位(位[0])为0时,执行BX指令。

RISC技术

嵌入式微处理器可以分为两类:

CISC和RISC;

CISC(ComplexInstructionSetComputer):

复杂指令系统计算机;随着计算机技术的发展而不断引入新的复杂的指令集,计算机的体系结构会越来越复杂。

大约有20%的指令会被反复使用,占整个程序代码的80%,而余下的80%的指令却不经常使用,在程序设计中只占20%。

RISC(ReducedInstructionSetComputer):

精简指令系统计算机;-采用固定长度的指令格式

-使用单周期指令

-大量使用寄存器

-可用加载/存储指令批量传输数据

-在循环处理中使用地址的自动增减

RISC技术与CISC技术比较

RISC技术

ARM处理器采用加载/存储(Load/Store)体系结构是典型的RISC处理器,即只有Load/Store的存/取指令可以访问存储器,其余指令都不允许进行存储器操作。

RISC体系结构基本特点:

(1)大多数指令只需要执行简单和基本的功能,其执行过程在一个机器周期内完成。

(2)只保留加载/存储指令。

操作数由加载/存储指令从存储器取出放寄存器内操作。

(3)芯片逻辑不采用或少采用微码技术,而采用硬布线逻辑。

(4)减少指令数和寻址方式。

(5)指令格式固定,指令译码简化。

(6)优化编译。

RISC技术

ARM体系结构还采用了一些特别的技术:

所有的指令都可根据前面的执行结果决定是否被执行,提高了指令的执行效率。

可用Load/Store指令批量传输数据,以提高数据的传输效率。

可在一条数据处理指令中同时完成逻辑处理和移位处理。

RISC和CISC各有优势,界限并不那么明显。

现代的CPU往往采用CISC的外围,内部加入了RISC的特性,如超常指令集CPU就是融合了RISC和CISC的优势,成为未来的CPU发展方向之一。

流水线技术

是一种将每条指令分解为多步,并让各步操作重叠,从而实现几条指令并行处理的技术;

程序中的指令仍是一条条顺序执行,但可以预先取若干条指令,并在当前指令尚未执行完时,提前启动后续指令的另一些操作步骤,从而可加快程序的运行速度;

开发和设计嵌入式系统的过程中,CPU的性能是一个非常重要的考虑因素。

流水线技术是在本质上影响程序执行速度的因素。

由于计算机中一条指令的各个执行阶段相对独立,因此,现代CPU大多设计成流水线型的机器,在这种类型机器中几个指令可以并行执行。

采用流水线的重叠技术大大提高了CPU的运行效率。

当流水线内部的信息通畅流动时,CPU流水线能够工作得最好。

但实际应用中,指令各执行阶段的操作时间长短不同,有一些指令序列可能会打断流水线内的信息流,所以有时流水线操作不十分通畅,会暂时降低CPU的执行速度。

单周期指令的执行过程

ARM的3级流水线

ARM7架构采用了一个3段的流水线:

(1)取指:

将指令从内存中取出来。

(2)译码:

操作码和操作数被译码以决定执行什么功能。

为下一周期准备数据路径需要的控制信号。

这一级指令”占有“译码逻辑,而不是”占有”数据路径

(3)执行:

执行已译码的指令。

指令占有数据路径,寄存器堆栈被读取,操作数在桶行移位器中被移位。

ALU产生运算结果并回写到目的寄存器中,ALU结果根据指令需求更改状态寄存器的条件位。

流水线模式下PC的更改过程

多周期ARM指令的3级流水线操作

数据路径涉及到所有执行周期、地址计算和数据传送。

译码逻辑总是产生数据路径在下一个周期使用的控制信号,因此除译码周期以外,在STR地址计算周期也产生数据传送所需的控制信号。

取指的存储器访问和执行的数据路径占用都是不可同时共享的资源,对于多周期指令来说,如果指令复杂以至于不能在单个时钟周期内完成执行阶段,就会产生流水线阻塞。

ARM的流水线设计问题

1)缩短程序执行时间:

Tprog:

执行一个程序所需时间;

Ninst:

执行该程序的指令条数;

CPI:

执行每条指令的平均时钟周期数;

Fclk:

处理器的时钟频率。

措施:

提高时钟频率fclk(导致流水线的级数增加)。

减少每条指令的平均时钟周期数CPI(需要解决流水线的相关问题)

2)解决流水线相关:

结构相关:

某些指令在流水线中重叠执行时,产生资源冲突。

措施:

1)采用分离式指令Cache和数据Cache。

2)ALU中采用单独加法器来完成地址计算。

数据相关:

当一条指令需要前面指令的执行结果,而这些指令均在流水线中重叠执行时,就可能引起流水线的数据相关。

数据相关有“写后读”、“写后写”和“读后写”等。

措施:

1)旁路技术。

2)流水线互锁技术。

控制相关:

当流水线遇到分支指令和其他会改变PC值的指令时,就会发生控制相关。

措施:

1)引入延时分支。

2)尽早计算出分支转移成功时的PC值(即分支的目标地址)。

ARM的5级流水线

ARM9和StrongARM架构都采用了5级流水线.

增加了I-Cache和D-Cache,把存储器的取指与数据存取分开;

增加了数据写回的专门通路和寄存器;

把指令的执行过程分割为5部分:

取指:

将指令从指令存储器中取出,放入指令流水线中。

指令译码:

对指令进行译码,从寄存器堆中读取寄存器操作数。

执行:

把一个操作数移位,产生ALU结果。

如果指令是Load或Store,在ALU中计算存储器的地址。

数据缓存:

如果需要,访问数据存储器;否则,ALU的结果只是简单地缓冲一个时钟周期,以便使所有指令具有同样地流水线流程。

写回:

将指令产生地结果写回到寄存器堆。

流水线对比

超标量执行

通过重复设置多套指令执行部件,同时处理并完成多条指令,实现并行操作,来达到提高处理速度的目的。

所有ARM内核,包括流行的ARM7、ARM9和ARM11等,都是单周期指令机。

ARM公司下一代处理器将是每周期能处理多重指令的超标量机。

超标量处理机:

一个时钟周期内同时执行多条指令的处理机。

超标量处理器中的多指令单元

超标量与流水线技术是兼容的,为了能够在一个时钟周期内同时发射多条指令,超标量处理机必须有两条或两条以上能够同时工作的指令流水线。

但与此同时,也带来了多流水线的调度问题和操作部件的资源冲突问题。

超标量处理器在执行的过程中必须动态地检查指令相关性。

如果代码中有分支指令,必须将分支被执行和分支不被执行这两种情况分开考虑。

计算执行时间几乎是不可能的。

存储系统机制

存储器就是用来存储信息的部件,存储器是嵌入式系统硬件中的重要组成部分。

设计嵌入式系统的存储器时需要考虑:

是否需要扩展;

整个嵌入式系统的存储器是由片内和片外两部分组成。

为了解决速度和内存容量的问题,在系统中采用虚拟地址空间和高速缓存来提高内存的平均性能。

存储管理单元(MMU)进行地址转换,它在一个小的物理内存中提供相对较大的虚拟存储空间。

存储器部件的分类

按在系统中的地位分类:

(1)主存储器(MainMemory,简称内存或主存)

(2)辅助存储器(AuxiliaryMemory,SecondaryMemory,简称辅存或外存)

按存储介质分类:

(1)磁存储器(MagneticMemory),

(2)半导体集成电路存储器(通常称为半导体存储器),

(3)光存储器(OpticalMemory),

(4)激光光盘存储器(LaserOpticalDisk)

按信息存取方式分类:

(1)随机存取存储器RAM

(2)只读存储器ROM

存储器的组织和结构

嵌入式存储器一般采用存储密度较大的存储器芯片,典型的嵌入式存储器系统由ROM、RAM、EPROM等组成。

常用的存储器

随机存储器(RAM)

(1)静态随机存储器(SRAM)

(2)动态随机存储器(DRAM)

只读存储器(ROM),它在嵌入式系统中非常有用,因为许多代码或数据不随时间改变。

(1)工厂编程的只读存储器

(2)现场可编程只读存储器

存储器的性能

大容量、高速度、低价格是评价存储器性能的三个主要指标,也是存储体系设计的主要目标。

容量:

Sw=Wlm。

其中W为存储体的字长(单位为位或字节),l为单个存储体的字数,m为并行工作的存储体个数。

速度:

m个存储体并行工作时,可达到的最大频率宽度为Bm=Wm/TM。

其中TM是连续起动一个存储器所必要的时间间隔,TM>TA。

Bm是连续提供数据的速率。

价格:

具有SM位的存储器,每位价格表示为c=C/Sm。

其中C是总价格。

存储体系的组成

单体单字存储器

单体多字存储器

多体单字交叉存取存储器

多体多字交叉存取存储器

并行主存系统:

能并行读出多个CPU字的单体多字和多体单字及多体多字的交叉存取系统。

存储体系的形式

存储层次结构的组成原则:

①每位价格从上往下依次减少。

②存储容量从上往下依次增加。

③存取速度从上往下依次减慢。

④CPU的访问频度从上往下依次减少。

总线协议

总线是CPU与存储器和设备通信的机制。

总线的一个主要作用是提供到存储器的接口。

大部分总线协议的基本构件是四周期握手协议。

总线读写

总线的基本操作是读和写。

Clock提供总线组件各部分同步。

当总线读时,R/W’为1。

当总线写时,R/W’为0。

Address是一个a位信号束,为访问提供地址。

Data是一个n位信号束,它可从CPU得到数据或向CPU传送数据。

Dataready’当数据束上值合法时发信号。

总线的时序图

总线行为以时序图说明。

时序图表示总线上的信号如何随时间变化。

直接内存访问(DMA)