哈工大CPU设计代码.docx

《哈工大CPU设计代码.docx》由会员分享,可在线阅读,更多相关《哈工大CPU设计代码.docx(29页珍藏版)》请在冰豆网上搜索。

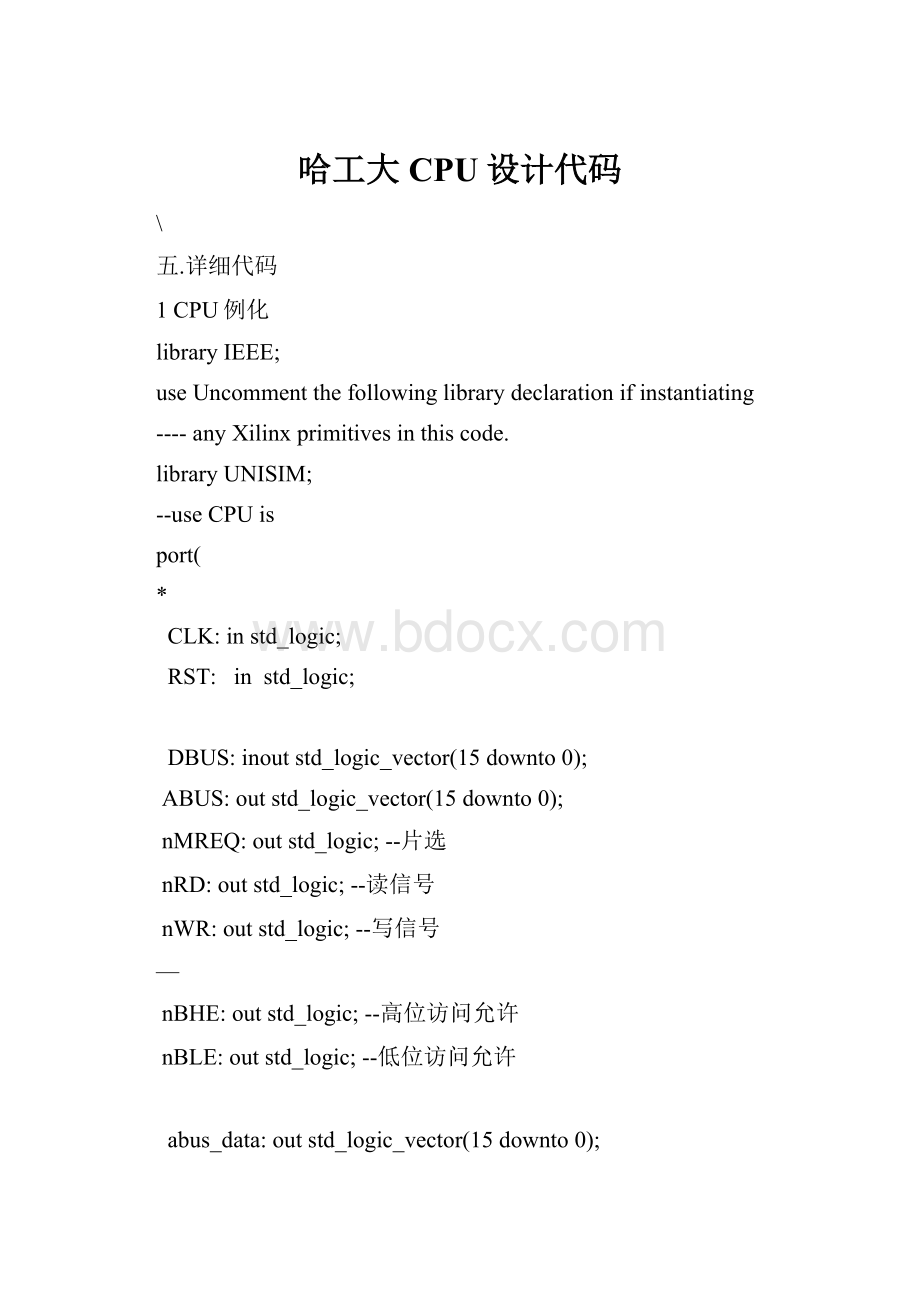

哈工大CPU设计代码

\

五.详细代码

1CPU例化

libraryIEEE;

useUncommentthefollowinglibrarydeclarationifinstantiating

----anyXilinxprimitivesinthiscode.

libraryUNISIM;

--useCPUis

port(

*

CLK:

instd_logic;

RST:

instd_logic;

DBUS:

inoutstd_logic_vector(15downto0);

ABUS:

outstd_logic_vector(15downto0);

nMREQ:

outstd_logic;--片选

nRD:

outstd_logic;--读信号

nWR:

outstd_logic;--写信号

—

nBHE:

outstd_logic;--高位访问允许

nBLE:

outstd_logic;--低位访问允许

abus_data:

outstd_logic_vector(15downto0);

dbus_data:

outstd_logic_vector(15downto0);

cs_data:

outstd_logic;

wr_data:

outstd_logic;

rd_data:

outstd_logic;

!

bh_data:

outstd_logic;

bl_data:

outstd_logic;

beat:

outstd_logic_vector(3downto0);

ir:

outstd_logic_vector(15downto0);

cy_out:

outstd_logic;

z_out:

outstd_logic

);

《

endCPU;

architectureBehavioralofCPUis

componentjiepaiis

Port(

clk:

inSTD_LOGIC;

rst:

inSTD_LOGIC;

k:

outSTD_LOGIC_VECTOR(3downto0)

。

);

endcomponent;

componentquzhiis

Port(

rst:

instd_logic;--复位

k0,k1:

instd_logic;--时钟控制

pc_in_flag:

instd_logic;--PC回写允许

~

ir_in:

instd_logic_vector(15downto0);--IR进入

pc_in:

instd_logic_vector(15downto0);--PC回写

visit_mem_flag:

outstd_logic;--访存信号

pc_out:

outstd_logic_vector(15downto0);--PC输出

ir_out:

outstd_logic_vector(15downto0)--IR输出

);

endcomponent;

…

componentyunsuanis

Port(

rst:

instd_logic;--复位信号

k0,k1,k2,k3:

instd_logic;--节拍控制

rewrite_flag:

instd_logic;--寄存器回写允许

rewrite_data:

instd_logic_vector(7downto0);--寄存器回写数据

ir_in:

instd_logic_vector(15downto0);--指令IR进入

!

aluout:

inoutstd_logic_vector(7downto0);--运算结果输出

addr:

outstd_logic_vector(15downto0);--准备好的地址输出

if_reg:

outstd_logic;--是否回写寄存器

if_pc:

outstd_logic;--是否回写pc

m_r:

outstd_logic;--给存储器管理模块读信号

m_w:

outstd_logic;--给存储器管理模块写信号

CyFlag:

outstd_logic;

(

ZFlag:

outstd_logic;

toHX:

outstd_logic_vector(15downto0)

);

endcomponent;

componentcunchuis

¥

Port(

rst:

instd_logic;--复位信号

m_w_in:

inoutstd_logic;--写请求

m_r_in:

inoutstd_logic;--读请求

c_w_out:

outstd_logic;

c_r_out:

outstd_logic;

k2:

instd_logic;--节拍控制

aluout_in:

instd_logic_vector(7downto0);--Aluout输入

<

dataFromMem:

instd_logic_vector(7downto0);

dataToMem:

outstd_logic_vector(7downto0);

outToHX:

outstd_logic_vector(7downto0)--输出到回写模块

);

endcomponent;

componentfangcunis

"

Port(

k0,k1,k2:

instd_logic;--节拍控制

qz_visit_flag:

instd_logic;--取址模块取址信号

c_r_in:

instd_logic;

c_w_in:

instd_logic;

pc_in:

instd_logic_vector(15downto0);--pc输入

addr_in:

instd_logic_vector(15downto0);

data_in:

instd_logic_vector(7downto0);--存数的时候用

—

DBUS:

inoutstd_logic_vector(15downto0);

ABUS:

outstd_logic_vector(15downto0);

nMREQ:

outstd_logic;--片选

nRD:

outstd_logic;--读信号

nWR:

outstd_logic;--写信号

nBHE:

outstd_logic;--高位访问允许

nBLE:

outstd_logic;--低位访问允许

、

data_out:

outstd_logic_vector(7downto0);--取得数据输出

ir_out:

outstd_logic_vector(15downto0)--取得指令输出

);

endcomponent;

componenthuixieis

Port(

?

k3:

instd_logic;

if_pc_in:

instd_logic;

if_reg_in:

instd_logic;

from_M:

instd_logic_vector(7downto0);

pc_in:

instd_logic_vector(15downto0);--用于处理jz,jc

jmp_in:

instd_logic_vector(15downto0);

ir_in:

instd_logic_vector(15downto0);

pc_update:

outstd_logic;--PC回写标志

}

reg_update:

outstd_logic;--Reg回写标志

pcnew:

outstd_logic_vector(15downto0);

Rdata:

outstd_logic_vector(7downto0)

);

endcomponent;

--信号赋值

$

signalk0_cpu,k1_cpu,k2_cpu,k3_cpu:

std_logic;

signalrepc_flag_cpu:

std_logic;

signalirToqz_cpu:

std_logic_vector(15downto0);

signalrepc_cpu:

std_logic_vector(15downto0);

signalqzVmem_flag_cpu:

std_logic;

signalpcOut_cpu:

std_logic_vector(15downto0);

signaltoHX_cpu:

std_logic_vector(15downto0);

signalirOut_cpu:

std_logic_vector(15downto0);

"

signalrereg_flag_cpu:

std_logic;

signalrereg_data_cpu:

std_logic_vector(7downto0);

signalaluout_cpu:

std_logic_vector(7downto0);

signaladdr_cpu:

std_logic_vector(15downto0);

signalif_reg_cpu:

std_logic;

signalif_pc_cpu:

std_logic;

signalm_r_cpu:

std_logic;

signalm_w_cpu:

std_logic;

)

signalc_r_cpu:

std_logic;

signalc_w_cpu:

std_logic;

signaldataFromMem_cpu:

std_logic_vector(7downto0);

signaldataToMem_cpu:

std_logic_vector(7downto0);

signaloutToHX_cpu:

std_logic_vector(7downto0);

signalabus_cpu:

std_logic_vector(15downto0);

signaldbus_cpu:

std_logic_vector(15downto0);

signalcs_data_cpu:

std_logic;

`

signalwr_data_cpu:

std_logic;

signalrd_data_cpu:

std_logic;

signalbh_data_cpu:

std_logic;

signalbl_data_cpu:

std_logic;

begin

u1:

jiepaiportmap(

…

clk=>CLK,

rst=>RST,

k(0)=>k0_cpu,

k

(1)=>k1_cpu,

k

(2)=>k2_cpu,

k(3)=>k3_cpu

);

u2:

quzhiportmap(

-

rst=>RST,

k0=>k0_cpu,

k1=>k1_cpu,

pc_in_flag=>repc_flag_cpu,

ir_in=>irToqz_cpu,

pc_in=>repc_cpu,

visit_mem_flag=>qzVmem_flag_cpu,

》

pc_out=>pcOut_cpu,

ir_out=>irOut_cpu

);

u3:

yunsuanportmap(

rst=>RST,

k0=>k0_cpu,

k1=>k1_cpu,

k2=>k2_cpu,

&

k3=>k3_cpu,

rewrite_flag=>rereg_flag_cpu,

rewrite_data=>rereg_data_cpu,

ir_in=>irOut_cpu,

aluout=>aluout_cpu,

addr=>addr_cpu,

if_reg=>if_reg_cpu,

>

if_pc=>if_pc_cpu,

m_r=>m_r_cpu,

m_w=>m_w_cpu,

CyFlag=>Cy_out,

ZFlag=>Z_out,

toHX=>toHX_cpu

);

u4:

cunchuportmap(

(

rst=>RST,

m_w_in=>m_w_cpu,

m_r_in=>m_r_cpu,

c_w_out=>c_w_cpu,

c_r_out=>c_r_cpu,

k2=>k2_cpu,

aluout_in=>aluout_cpu,

dataFromMem=>dataFromMem_cpu,

;

dataToMem=>dataToMem_cpu,

outToHX=>outToHX_cpu

);

u5:

fangcunportmap(

k0=>k0_cpu,

k1=>k1_cpu,

k2=>k2_cpu,

qz_visit_flag=>qzVmem_flag_cpu,

c_r_in=>c_r_cpu,

c_w_in=>c_w_cpu,

pc_in=>pcOut_cpu,

addr_in=>addr_cpu,

data_in=>dataToMem_cpu,

DBUS=>DBUS,

;

ABUS=>abus_cpu,

nMREQ=>cs_data_cpu,

nRD=>rd_data_cpu,

nWR=>wr_data_cpu,

nBHE=>bh_data_cpu,

nBLE=>bl_data_cpu,

data_out=>dataFromMem_cpu,

~

ir_out=>irToqz_cpu

);

u6:

huixieportmap(

k3=>k3_cpu,

if_pc_in=>if_pc_cpu,

if_reg_in=>if_reg_cpu,

from_M=>outToHX_cpu,

pc_in=>pcOut_cpu,

、

jmp_in=>toHX_cpu,

ir_in=>irOut_cpu,

pc_update=>repc_flag_cpu,

reg_update=>rereg_flag_cpu,

pcnew=>repc_cpu,

Rdata=>rereg_data_cpu

);

!

-------------------------------

beat(0)<=k0_cpu;

beat

(1)<=k1_cpu;

beat

(2)<=k2_cpu;

beat(3)<=k3_cpu;

ABUS<=abus_cpu;

abus_data<=abus_cpu;

。

dbus_data<=DBUS;

ir<=irOut_cpu;

nMREQ<=cs_data_cpu;

cs_data<=cs_data_cpu;

nRD<=rd_data_cpu;

rd_data<=rd_data_cpu;

nWR<=wr_data_cpu;

>

wr_data<=wr_data_cpu;

nBHE<=bh_data_cpu;

bh_data<=bh_data_cpu;

nBLE<=bl_data_cpu;

bl_data<=bl_data_cpu;

endBehavioral;

2时钟管理模块

?

libraryIEEE;

useUncommentthefollowinglibrarydeclarationifinstantiating

----anyXilinxprimitivesinthiscode.

libraryUNISIM;

--usejiepaiis

port(

rst:

instd_logic;--复位信号

clk:

instd_logic;--输入时钟信号

(

k:

outstd_logic_vector(3downto0)--节拍输出

);

endjiepai;

architectureBehavioralofjiepaiis

signaltemp_k:

std_logic_vector(3downto0);

!

begin

process(clk,rst,temp_k)

begin

if(rst='1')then

temp_k<="0000";

elsifclk='1'andclk'eventthen

casetemp_kis

when"0000"|"1000"=>

;

temp_k<="0001";

when"0001"=>

temp_k<="0010";

when"0010"=>

temp_k<="0100";

when"0100"=>

temp_k<="1000";

whenothers=>

\

null;

endcase;

endif;

k<=temp_k;

endprocess;

endBehavioral;

3取址模块

libraryIEEE;

*

useUncommentthefollowinglibrarydeclarationifinstantiating

----anyXilinxprimitivesinthiscode.

libraryUNISIM;

--usequzhiis

Port(rst:

instd_logic;--复位

k0,k1:

instd_logic;--时钟控制

pc_in_flag:

instd_logic;--PC回写允许

ir_in:

instd_logic_vector(15downto0);--IR进

(

pc_in:

instd_logic_vector(15downto0);--PC回写

visit_mem_flag:

outstd_logic;--访存信号

pc_out:

outstd_logic_vector(15downto0);--PC输出

ir_out:

outstd_logic_vector(15downto0)--IR输出

);

endquzhi;

`

architectureBehavioralofquzhiis

signaltemp_pc:

std_logic_vector(15downto0);

begin

process(rst,k0,k1,pc_in_flag,pc_in,ir_in,temp_pc)

begin

ifrst='1'then

temp_pc<="0000000000000000";

ir_out<="0000000000000000";

&

elsifpc_in_flag='1'then

temp_pc<=pc_in;

--elsifk1'eventandk1='1'then

--temp_pc<=temp_pc+1;

endif;

casek0is

when'1'=>

[

pc_out<=temp_pc;

visit_mem_flag<='1';

whenothers=>

visit_mem_flag<='0';

endcase;

ir_out<=ir_in;

endprocess;

[

endBehavioral;

4运算模块

libraryIEEE;

useUncommentthefollowinglibrarydeclarationifinstantiating

----anyXilinxprimitivesinthiscode.

libraryUNISIM;

--useyunsuanis

[

Port(

rst:

instd_logic;--复位信号

k0,k1,k2,k3:

instd_logic;--节拍控制

rewrite_flag:

instd_logic;--寄存器回写允许

rewrite_data:

instd_logic_vector(7downto0);--寄存器回写数据

ir_in:

instd_logic_vector(15downto0);--指令IR进入

aluout:

inoutstd_logic_vector(7downto0);--运算结果输出

—

addr:

outstd_logic_vector(15downto0);--准备好的地址输出

if_reg:

outstd_logic;--是否回写寄存器

if_pc:

outstd_logic;--是否回写pc

m_r:

outstd_logic;

m_w:

outstd_logic;

toHX:

outstd_logic_vector(15downto0);

Cyflag:

outstd_logic;

【

Zflag:

outstd_logic

);

endyunsuan;

architectureBehavioralofyunsuanis

typeregisarray(0to7)ofstd_logic_vector