计算机硬件技术基础习题答案太原理工Word格式.docx

《计算机硬件技术基础习题答案太原理工Word格式.docx》由会员分享,可在线阅读,更多相关《计算机硬件技术基础习题答案太原理工Word格式.docx(15页珍藏版)》请在冰豆网上搜索。

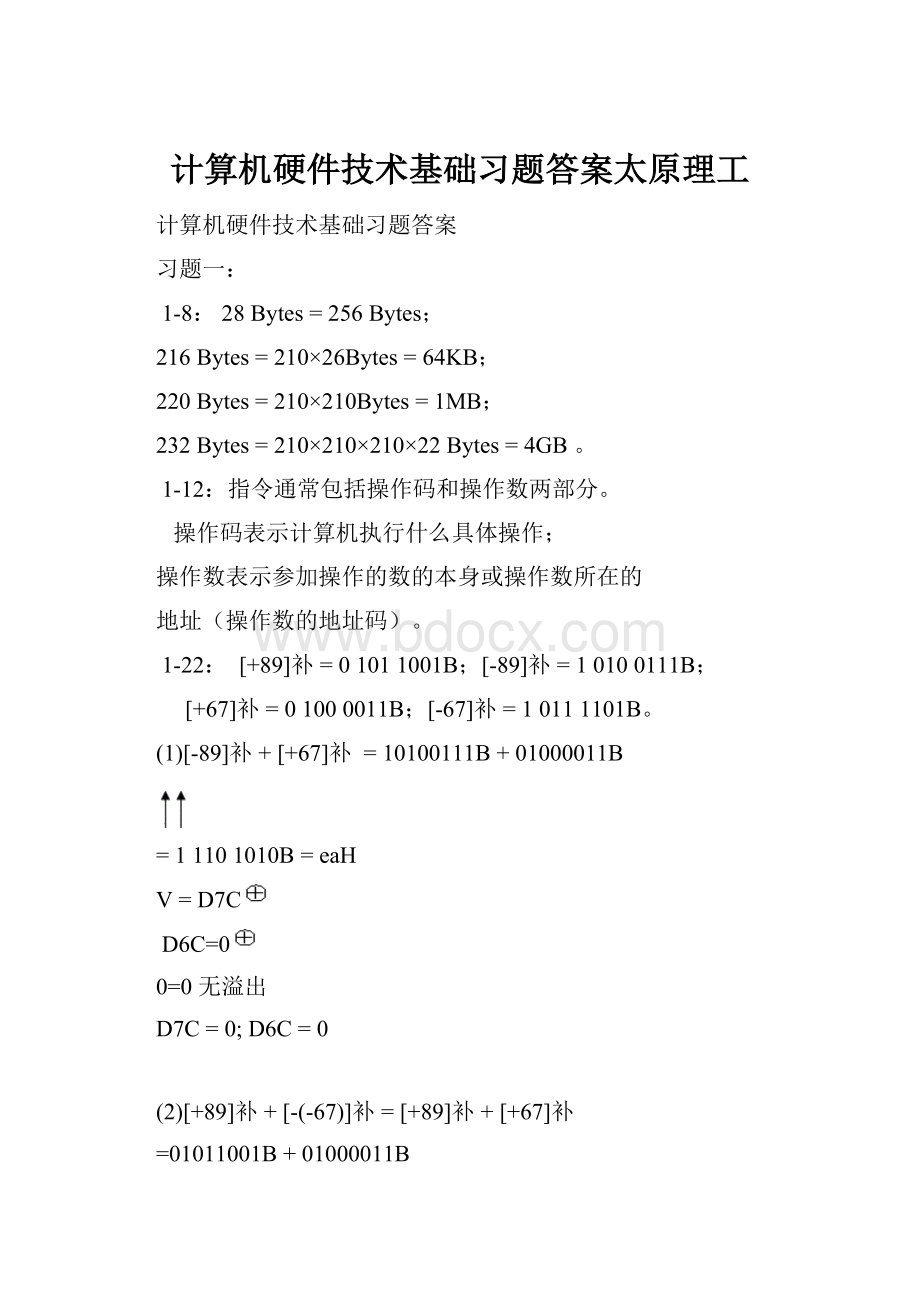

0=1溢出

D7C=1;

(4)[-89]补+[-(-67)]补=[-89]补+[+67]补

=10100111B+01000011B

1-30:

(1)01111001+01110000

补码竖式:

01111001

+01110000

———————

11101001

V=D7C

1=1溢出;

两正数相加,其结果应为正数;

但结果为负

数,故产生了溢出,正溢出。

(2)-01111001–01110000

10000111

+10010000

1,00010111

0=1溢出;

两负数相加,其结果应为负数;

但结果为正

数,故产生了溢出,负溢出。

(3)01111100–01111111

补码竖式:

01111100

+10000001

11111101

0=0无溢出。

(4)-01010001+01110001

补码竖式:

10101111

+01110001

1,00100000

1=0无溢出。

1-31:

字长为32位二进制数的补码表示范围:

-231~+(231-1)

负数的最小值为:

-231

正数的最大值为:

+(231-1)

习题二:

2-1:

CISC称为复杂指令集计算机。

早期的CPU全部是

CISC架构,它的设计目的是要用最少的机器语言指

令来完成所需的计算任务。

Intel80x86系列微处理器

总体来说使用CISC设计架构。

RISC称为精简指令集计算机。

是从20世纪80年代开始逐渐发展的一种微处理器体系结构,它的设计目的是尽量减少指令的数量和种类,设法降低执行每条指令的时钟频率(降低CPU的复杂性),要求软件来指定各个操作步骤。

(了解各自的特点)

2-11:

(1)起始地址:

10000H;

结束地址:

1FFFFH。

(2)起始地址:

12340H;

2233FH。

(3)起始地址:

E0000H;

EFFFFH。

(4)起始地址:

AB000H;

BAFFFH。

2-12:

(1)CS=1000H和IP=2000H

下条指令的存储器地址为:

1000H×

16+2000H

=10000H+2000H

=12000H

(2)CS=2400H和IP=1A00H

2400H×

16+1A00H

=24000H+1A00H

=25A00H

(3)CS=1A00H和IP=B000H

1A00H×

16+B000H

=1A000H+B000H

=25000H

(4)CS=3456H和IP=ABCDH

3456H×

16+ABCDH

=34560H+ABCDH

=3F12DH

2-15:

8086的进位标志由加法类指令和减法类指令(运

算类指令)来置位。

2-51:

嵌入式系统的特点:

(1)将计算机技术、电子技术和半导体技术相结合的

技术密集、高度分散、不断创新的集成系统;

(2)面向特定应用领域的具有体积小、功耗低、成本

低、专业化程度高的系统;

(3)必须紧密结合专门应用的需求,与具体产品的换

代同步更新,应有较长生命周期的系统;

(4)系统软件固化在内存或处理器芯片内部,高效与

可靠运行的系统;

(5)本身不具备自举开发能力(完成设计后不能任意

修改程序)的系统。

嵌入式系统的组成部分:

嵌入式处理器、嵌入式外设、嵌入式操作系统和嵌入式应用系统4部分组成。

习题三

3-2:

指令格式包含哪些部分?

什么是寻址方式?

8086/8088的寻址方式可分为哪几种类型?

指令格式包括操作码和操作数(或操作数地址)两部分;

根据操作码所指定的功能去寻找操作数所在地址的方式叫寻找方式;

8086/8088的寻址方式分为两种类型:

(1)数据寻址方式,是寻址操作数地址,操作数可能在代码段(已取入CPU内)、数据段、附加数据段、堆栈段中;

(2)程序存储器寻址方式,是寻址程序地址,在代码段中。

3-3:

指出8086/8088下列指令源操作数的寻址方式。

目的操作数,源操作数

(1)MOVAX,1200H立即数寻址

(2)MOVBX,[1200H]

直接数据寻址

(3)MOVBX,[SI]

寄存器间接寻址

(4)MOVBX,[SI+1200H]

寄存器相对寻址

(5)MOV[BX+SI],AL

寄存器寻址

(6)ADDAX,[BX+DI+20H]

相对基址加变址寻址

(7)MULBL

(8)XLAT

该指令是无操作数指令,其源操作数为[BX+AL],相当于基址加变址寻址

(9)INAL,DX

(10)INCWORDPTR[BP+50H]

此指令的操作数即是源操作数,又是目的操作数。

3-5指出8086/8088下列指令的错误。

(1)MOV[SI],IP---IP寄存器不可直接访问

(2)MOVCS,AX---CS寄存器不可直接访问

(3)MOVBL,SI+2---寄存器相对寻址格式错或寄存器寻址类型不匹配

(4)MOV60H,AL---立即数不能为目的操作数

(5)PUSH2400H---源操作数不能为立即数

(6)INC[BX]---间接寻址的存储单元加1指令,

应该用BYTEPTR、WORDPTR

指明是字节加还是字加

(7)MUL-60H---乘法指令的源操作不能为立即数

(8)ADD[2400H],2AH---目的操作数[2400H]应指

明是BYTEPTR字节操作

(9)MOV[BX],[DI]---源操作数与目的操作数不能

同时为存储器操作数

(10)MOVSI,AL---源操作数为字节寄存器,目的

操作数为字寄存器

3-10:

若AX=5555H,BX=FF00H,试问在下列程序段执行后,AX=?

BX=?

CF=?

ANDAX,BX------AX=5500H,CF=0

XORAX,AX------AX=0000H,CF=0

NOTBX------BX=00FFH,CF=0(保持不变)

3-14:

试选用最少的指令,实现下述功能。

(1)AH的高四位清零。

ANDAH,0FH

(2)AL的高4位取反

XORAL,0F0H

(3)AL的高4位移到低4位,高4位清零

MOVCL,4

SHRAL,CL

(4)AH的低4位移到高4位,低4位清零

MOVCL,4

SHLAH,CL

3-17:

设初值AX=6264H,CX=0004H,在执行下列程序段后,AX=?

ANDAX,AX---AX=6264H

JZDONE---ZF=0,顺序执行程序

SHLCX,1---CX=0008H

RORAX,CL---AX=6462H

DONE:

ORAX,1234H---AX=7676H

习题四

4-3:

已知一数组语句定义为:

ARRAYDW100DUP(567H,3DUP(?

)),5678H

请指出下列指令执行后,各个寄存器中的内容是什么?

MOVBX,OFFSETARRAY---BX=ARRAY的偏移地址

MOVCX,LENGTHARRAY---CX=100

MOVSI,0---SI=0

ADDSI,TYPEARRAY---SI=2

4-5:

下列程序段执行后,寄存器AX、BX和CX的内容分别是多少?

ORG0202H

DA_WORDDW20H

MOVAX,DA_WORD

----AX=0020H

MOVBX,OFFSETDA_WORD

----BX=0202H

MOVCL,BYTEPTRDA_WORD

----CL=20H

MOVCH,TYPEDA_WORD

----CH=2

4-9:

某程序设置的数据区如下:

DATASEGMENT

DB1DB12H,34H,0,56H

DW1DW78H,90H,0AB46H,1234H

ADR1DWDB1

ADR2DWDW1

AAADW$-DB1

BUFDB5DUP(0)

DATAENDS

画出该数据段内容在内存中的存放形式(要求用十六进制补码表示,按字节组织)。

12H

34H

00H

56H

78H

90H

46H

ABH

04H

10H

DB1DS:

0000H

DW1

ADDR1

ADDR2

AAA

BUF

4-10:

分析下列程序:

A1DB10DUP(?

)

A2DB0,1,2,3,4,5,6,7,8,9

.

MOVCX,LENGTHA1------CX=10

MOVSI,SIZEA1–TYPEA1------SI=9

LP:

MOVAL,A2[SI]------AL=9,8,7,6,5,4,3,2,1,0

MOVA1[SI],AL------A1[SI]=9,8,7,6,5,4,3,2,1,0

SUBSI,TYPEA1------SI=8,7,6,5,4,3,2,1,0

DECCX-----CX=9,8,7,6,5,4,3,2,1,0

JNZLP

HLT

(1)该程序的功能是什么?

(2)该程序执行后,A1单元开始的10个字节内容是什么?

答:

(1)该程序是将数据区A2的数据逆序复制到数据区A1中;

(2)该程序执行后,A1单元开始的10个字节内容是:

0,1,2,3,4,5,6,7,8,9

4-11:

假设BX=45A7H,变量VALUE中存放的内容为78H,下列各条指令单独执行后BX=?

(1)XORBX,VALUE------BX=45DFH

(2)SUBBX,VALUE------BX=452FH

(3)ORBX,VALUE------BX=45FFH

(4)XORBX,0FFH-------BX=4558H

(5)ANDBX,00H-------BX=0000H

(6)TESTBX,01H------BX=45A7H

习题五

5-2:

常用的地址译码方式有几种?

各有哪些特点?

答:

地址译码方式有两种:

(1)单译码方式(字结构)

它的全部地址码只用一个地址译码器电路译码,译码输出的字选择线直接选中与输入地址码对应的存储单元。

(2)双译码方式(重合译码)

它将地址码分为X与Y两部分,用两个译码电路分别译码,X向译码又称行译码,其输出线称行选择线,它选中存储矩阵中一行的所有存储单元;

Y向译码又称列译码,其输出线称列选择线,它选中存储矩阵中一列的所有存储单元,只有X向和Y向的选择线同时选中的那一位存储单元,才能进行读或写操作。

5-4:

设有一个具有13位地址和8位字长的存储器,试问:

(1)存储器能存储多少字节信息?

213字节=8K字节;

(2)如果存储器由1K×

4位RAM芯片组成,共计需要多少芯片?

8K×

8=(1K×

8)×

8

=(1K×

4×

2)×

4)×

2×

=(1K×

16=16片

位扩展字扩展

(3)需要用那几个高位地址作为片选译码来产生芯片选择信号?

13位地址线中,A0---A9同时与16片1K×

4位RAM芯片的A0---A9地址线相连,A10,A11,A12这三根高位地址线作为片选译码来产生选择信号,其中每一条译码选择线同时连接作为位扩展的两片1K×

4位RAM芯片的片选线。

5-5:

下列RAM芯片各需要多少条地址线进行寻址?

需要多少条数据I/O线?

(1)512×

4位=29×

4位需9条地址线,4条数据I/O线;

(2)1K×

4位=210×

4位需10条地址线,4条数据I/O线;

(3)1K×

8位=210×

8位需10条地址线,8条数据I/O线;

(4)2K×

1位=211×

1位需11条地址线,1条数据I/O线;

(5)4K×

1位=212×

1位需12条地址线,1条数据I/O线;

(6)16K×

4位=214×

4位需14条地址线,4条数据I/O线;

(7)64K×

1位=216×

1位需16条地址线,1条数据I/O线;

(8)256K×

4位=218×

4位需18条地址线,4条数据I/O线;

5-6:

分别用1024×

4位和4K×

2位芯片构成64K的随机存取存储器,各需多少片?

64K=216KB=216×

8位=(210×

26)×

(4×

2)位

=210×

4位×

26×

2=(1024×

4位)×

128片

64K=216KB=216×

8位=(212×

24)×

(2×

4)位

=212×

2位×

24×

4=(4K×

2位)×

64片

5-15:

什么是存储器的分层结构?

并简要说明其特点。

存储器的层次结构主要为Cache—主存和主存—辅存这两个存储层次上;

Cache—主存在存储系统中主要是提高CPU的访问速度,使访问容量接近主存,访问速度接近Cache;

主存—辅存在存储系统中主要是扩大存储器的容量,使访问容量接近辅存,访问速度接近主存。