ICT 入门培训流程规范Word格式文档下载.docx

《ICT 入门培训流程规范Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《ICT 入门培训流程规范Word格式文档下载.docx(12页珍藏版)》请在冰豆网上搜索。

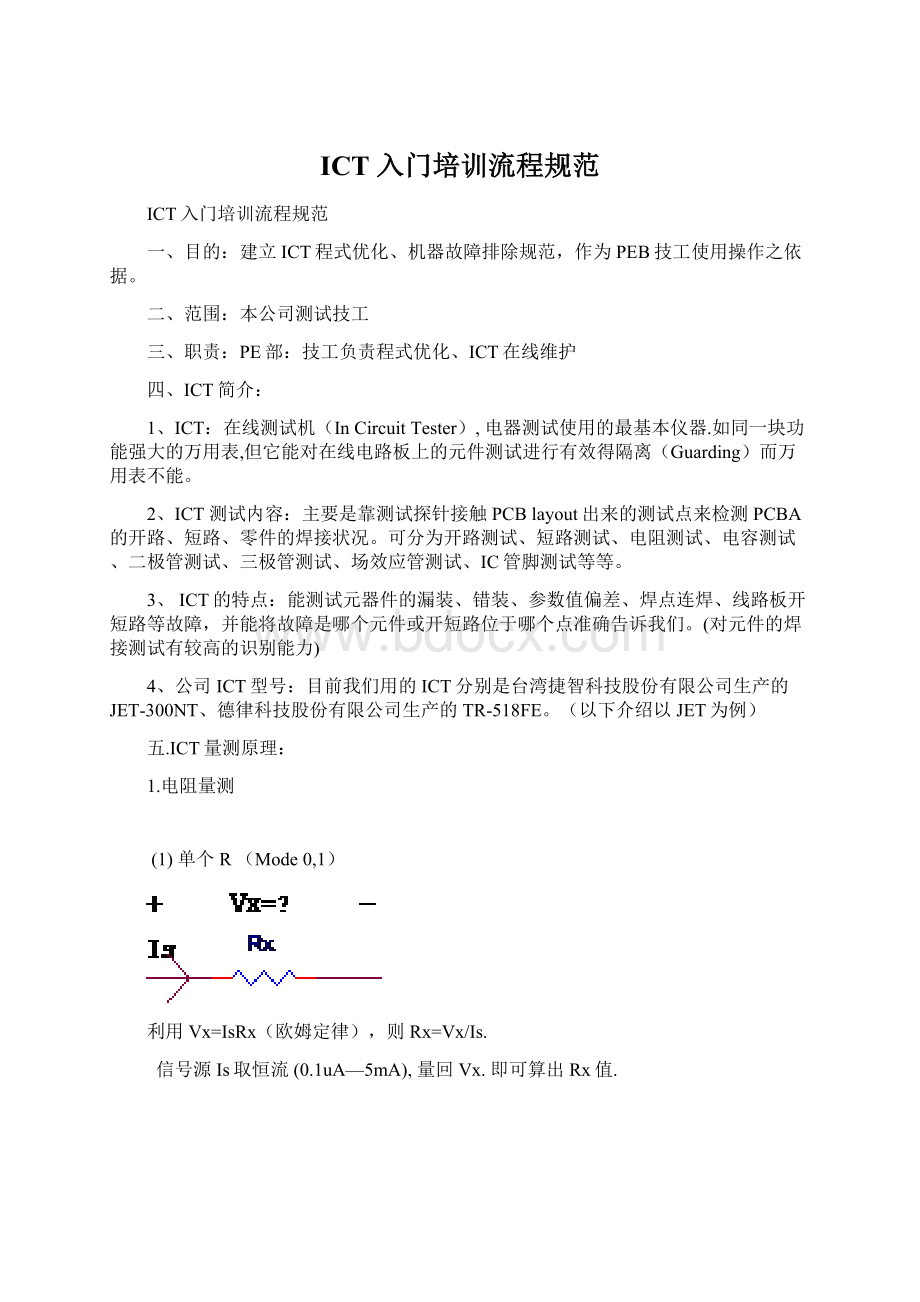

(1)单个R(Mode0,1)

利用Vx=IsRx(欧姆定律),则Rx=Vx/Is.

信号源Is取恒流(0.1uA—5mA),量回Vx.即可算出Rx值.

Ra=R1+R2

Rb=R3+R4

Rc=R1+Rx+R4

Rd=R2+Rx+R3

Rx=(Rc+Rd-Ra-Rb)/2

(2)小电阻(50欧姆以内)四线量测:

小电阻两端各下两支探针,1-4号探针的接触阻抗分别R1-R4,Ra,Rb,Rc,Rd分别为四次测试之量测值.

(3)R//C(mode2)信号源Vs取恒压(0.2V),量回Ix,Rx=Vs/Ix=0.2V/Ix,算出Rx值.

(4)R//L(mode3,4,5):

信号源取交流电压源Vs,用相位法辅助.

|Y’|Cosθ=YRx=1/Rx,

并|Y’|=I’x/Vs,故:

Rx=1/|Y’|Cosθ

2.电容及电感量测

(1)

单个C,L(Mode0,1,2,3):

信号源

取恒定交流压源Vs,Vs/Ix=Zc=1/2лfCx

求得:

Cx=Ix/2лfVs

Vs/Ix=Zl=2лfLx,求得:

Lx=Vs/2лfIx

(2)C//R或L//R(Mode5,6,7):

用相位法辅助,|Y’|Sinθ=|Ycx|,

即ωCx’Sinθ=ωCx

Cx=Cx’Sinθ,(Cx’=Ix’/2лfVs)

|Y’|Sinθ=|Ycx|,

即Sinθ/ωCx’=1/ωCx

Lx=Lx’/Sinθ,(Lx’=Vs/2лfIx’)

電容極性測試的另一方法是三端測試,須在上方加一探針觸及殼體.在電容的正負極加載直流電壓,至充飽后測量殼體電壓.由于正負極與殼體間的阻抗差異,故對于插反的電容所測量到的殼體電壓會與正確時不同.據此可判別電容的極性.(详见附页一)

3.跳线测试:

(UMPER,FUSE,WIRE,CONNECTOR,SWITCH,etc)

4.量测PN结:

(D,Q,IC,FET)

(1)信号源0-10V/3mAor30mA可程式电压源,量PN结导通电压;

(2)ZenerD的测试原理是量测其崩溃电压,与二极体的差异是在测试电压源不同,其电压源为0V-10V及0V-48V可程式电压源.

(3)电晶体测试需要三步骤测试,其中

(1)B-E和

(2)B-C脚是使用二极体的测试方法,(3)E-C使用Vcc的饱和电压值及截止值的不同,来测试电晶体是否插反.电晶体反插测试方法:

在B-E及E-C

脚两端各提供一个可程式电压源,量测出电晶体E-C正向的饱和电压为Vce=0.2V左右,若该电晶体反插时,则Vce电压将会变成截止电压,并大于0.2V,即可测出电晶体反插的错误.

5.量测Open/Short:

即以阻抗判定,先对待测板上所有Pin点进行学习,R<

25Ω即归为ShortGroup,然后Test时进行比较,R<

5Ω判定为Short,R>

55Ω判为Open.

6.Guarding(隔离)的实现:

以电流源当信号源输入时,則在相接元件一的另一腳加上一等高電位能(GuardingPoint),以防止電流流入與被測元件相接的旁路元件,確保量測的精準性。

此時隔離點的選擇必須以和被測元件高電位能腳(Hi-Pin)相接之旁路元件為參考範圍.

以电压源当信号源输入时,則在相接元件二的另一腳加上一等底電位能(GuardingPoint),以防止與被測元件相接之元件所產生的電流流入,而增加量測的電流,影響量測的精準性。

此時隔離點的選擇必須以和被測元件低電位能腳(Low-Pin)相接之旁路元件為參考範圍.

7、三端電容極性測試:

7.1测试点

7.2试程式

測試原理為從HiP送sourcevoltage,然後從G-P1讀回量測值,由於缺件或反插,其量測值很低(接近0),所以只比較下限,上限Don’tcare。

✧Act_V:

Sourcevoltage,建議值為0.2V

✧Std_V:

SenseVoltage(Threshold),依實際Debug後決定

✧Hlim:

固定為–1(Don,tcare)

✧Llim:

建議值為20,可依實際Debug後決定

✧Mode:

固定為8或18(適用於防爆電容)

✧Type:

固定為PX

✧Hip:

電容負端(sourcepin)

✧Lop:

電容正端

✧Dly:

依實際Debug後決定

✧G-P1:

SensePin

7.3除错规则

將Hip/Lop相同的電容放在一起,例如CE1,CE2,CE3的HiP及LoP都是1及3,所以測試程式如下:

✧Debug時可交換HiP及Lop比較量測值,以決定較佳之Threshold(Std_V)

✧若交換HiP及Lop量測值差異不大可調整Delaytime或Sourcevoltage(Act_v)

✧若交換HiP及Lop量測值皆很低,可能是第三端接觸問題,可先檢查第三端是否接觸正常或待測電容有歪斜,可用換針或扶正待測電容方式解決

✧治具製作時第三端選用測試針,需考慮相同位置待用料的高度差異,以免造成接觸不良或刺穿待測物的問題

✧三端電容量測是用來檢測缺件及反向,無法檢測錯件

✧可利用量測分析工具(HotKeyF12)決定較佳标准值,Delaytime.

8、IC空焊测试:

六、ICT调试(Debug)流程:

1、固定治具:

将ICT治具架在压床上,将治具天板固定在压床蜂窝板上,锁紧治具固定螺丝,使其不会松动,将压床点动调整治具上探针行程,使之达到其行程的1/2-2/3左右,然后用排线依顺序将治具与开关板连接起来;

2、程序登录计算机:

将治具的测试程序COPY入计算机,并调出;

将测试程序检查一遍,未经过排序的,要先排序。

要按JP-电阻-电容-电感-二极管-IC的顺序(即按实际值排序);

然后存盘。

3、Open/Short学习:

学习之前,将状态参数里面的测试时基改为50,OPSDELAY更改为120-200;

置良品板于治具上,将压床压下即可开始学习;

学习完毕后要存盘。

七、ICTDebug技巧与方法:

1、先将待测板测试一遍,然后可进入“EDIT”DEBUG;

2、对于JP的DEBUG则比较简单,只要判定其有无点号,有无零件,点号正确无误即可OK。

一般“JP”我们把ACT-VAL定为“2JP”上限为“+10%”,下限为“-60%”;

3、电阻的DEBUG,则会比较复难,可按以下几步调试:

1)于小电阻,如零欧姆电阻,ACT-VAL可用2欧姆,然后上限为“+10%”下限为“99%”即可,对于几欧姆或零点欧姆小电阻,若客户要求用四线测试,则需做四线测试,未做要求的就可将线阻及机器内阻加零件值作为标准值,上限可放宽;

2)于小电阻:

(0Ω-1KΩ)要用定电流的测试方法(D1、D2);

3)电阻DEBUG一般有几种方法:

变换测量模式文件位元的变化,更改延迟时间,高低PIN对调,加隔离点等几种方法,可结合实际情况,具体分析处理;

4)GUARDING点对于电阻的DEBUG尤为重要,一般有这样一个原则:

电阻的两个点,其中一点所连组件较少,则该点所连组件另外一点作GUARDING点;

隔离点所连的组件阻抗须为20欧姆以上,电阻的隔离,加GND点很有效果;

5)电阻隔离的目的是将量测到的较少的值隔离成大的,使之更接近于实际值,若该电阻量测的结果很大,超出实际值,则要提出疑问,看看是否针点的问题,还是零件值的错误,或者是由于针点的不准引起的,等待。

6)对于并联的电阻,若两电阻阻抗相差不是很大,则用并联值作标准值,若相差很大,则大电阻不可测;

电阻没有针点的?

电阻没有针点的注明“NP”,没有组件的注明“NC”

7)电阻并联大电容的情况,用定电流的方法测试会不稳定且测试时间长,可用定电压的方法量测,并加长延迟时间,必要时可采用放电;

8)对于单项测试稳定,整页测试不稳定的组件可移到程序的最前面测试,电阻的上下限一般设为10%,大电阻可适当放大一些。

八、具体元件程式Debug方法:

因编写好的程式在实测时,因测试信号的选择,或被测元件线路影响,有些Step会Fail(即量测值超出±

%限),必须经过Debug.

1.电阻

在E[编辑]下,ALT-X查串联元件,ALT-P查并联元件。

据此选好“信号”(Mode)和串联最少元件的Hi-P/Lo-P,并ALT-F7选择GuardingPin。

R//C:

Mode2及Dly加大.

R//D(orIC、Q):

Mode1.

R//R:

Std-V取并联阻值.

R//L:

Mode3、4、5,根据Zl=2πfL,故L一定时,若f越高,则Zl越大,则对R影响越小.

2.电容

在[编缉]下一般根据电容值大小,选择相应的Mode。

如小电容(pF级),可选高频信号(Mode2、3),大电容(nF级)可选低频信号(Mode0、1),然后ALT-F7选择隔离。

3uF以上大电容,可以Mode4、8直流测试。

C//C:

Std-V取并联容值

C//R:

Mode5、6、7,由Zc=1/2лfC,故C一定时,f越高,Zc越小,则R的影响越小。

C//L:

Mode5、6、7,并且f越高效果越好。

3.电感

F8测试,选择Mode0、1、2中测试值最接近Std-V.

L//R:

Mode5、6、7。

4.PN结

F7自动调整,一般PN正向0.7V(Si),反向(2V以上)。

D//C:

Mode1及加Delay。

D//D(正向):

除正向导通测试,还须测反向截止(2V以上)以

免D反插时误判。

Zener:

Nat-V选不低于Zener崩溃电压,若仍无法测出崩溃电压,可选Mode1(30mA),另10-48Vzener管,可以HV模式测试。

5.电晶体

be、bc之PN结电压两步测试可判断Q之类型(PNPorNPN),Hi-P一样(NPN),Lo-P一样(PNP),并可Debugce饱和电压(0.2V以下),注意Nat-V为be偏置电压,越大Q越易进入饱和,但须做ce反向判断(须为截止0.2V以上),否则应调小Nat-V。

八、常见ICT误判及维护:

1、ICT盲点:

①特殊IC(个别IC对GND、VCC无保护二极体)

②单点测试(如排插、插座、个别单个测试点的元件)

③并联10个以上的电容并联(示电容的精密度作调整)

④并联15倍以上小电阻的大电阻

⑤D/L或D/25Ω以下,D不可测

⑥跳线并联

⑦IC内部功能测试

2.压床行程不足,探针压入量程为2/3

3.PCB板定位柱松动,造成探针偏离焊盘

4.PCB上测试点或过穿孔绿油未打开、吃锡不良

5.PCB制程不良:

如未洗板导致PCB上松香过多探针接触不良

6.探针不良(如针头钝化、老化、阻抗过高……

7、元件厂商变更(如小电容、IC之TESTJET)可加大±

%,更改TESTJET值

8、未Debug良好

9、ICT自身故障

10、硬体问题:

10.1开关板:

诊断(D)----切换电路板(B)----系统自我诊断(S)----切换电路板诊断(S)

若有B*C*表示SWB有Fail,请记录并通知TRI。

C*有可能为治具针点有Short造成。

10.2系统自我检测:

诊断(D)----硬体诊断(S)---系统自我检测(S)

有R、D项Fail可能为DC板故障.

有C、L项Fail可能AC板Fail.

有Power项Fail可能PowerFail,也请记录并通知供应商。

●日常维护

1一般GUARD点不超过3个,最好1、2个即可

2无用之GUARD点需去除

3可GUARDING的元件为电阻、电容,一般大电容GUARDING无效

4电阻GUARDING一般对地70%有效

5电容GUARDING一般对VCC70%有效

6GUARDING一般找串联小电阻(大于20Ω)、串联大电容

7若GUARDING元件时,串联跳线或电感可视为同点

8大电容并联测试偏大解决方式:

ACTUALΧ70%>

STANDARDΧ下限值

九、注意事项:

1、小电容的测试通常用“A4”或“A5”模式,若量测结果过大,则需加GUARDING点使OFFSET值不要太大,否则量测没有意义另外电容隔离VCC效果明显。

倘若小电容与大电空并联,则小电容可SKIP掉,不需测试,即便测试也会不稳定,又找不出问题;

2、大电容的量测,若用“DC”模式不稳定,可考虑用RANGE“+1”去试,或加长延迟时间;

3、电容的上下限一般为30%,小电容的上限可适当放宽,下限要小一些;

4、电容极性测试可用两种方法:

其一,二端测试法即用漏电流的方法,实际值送0-9.9V电压,标准值送电流,则模式会变为CM,适当加长DELAY,并调整实际值电压,使正反电流偏差较大;

其二,三端测试法,即在电解电容顶部加多一根针,高PIN为顶部针点,低PIN为负极针点,隔离点为正极针点.实际值送0.2V电压,标准值为0.05V左右,并适当加长DELAY,使反向时接近于0.2V;

5、电感的测试最好用两种方法:

其一,当作跳线测试,其二测其感量,这样既可测出电感的缺件错件,也可测到短路,上下限可放宽;

6、二极管除了用“DT”(2.2V,20MA)模式外,还可用”LV”(0-10V)模式。

当二极管并联大电容时可将RANGE“+1”,加延迟时间,还可将实际值电容提高,直到可测出反插及漏件;

二极管并联的情况,可加做电流的测试,即用“CM”模式,实际值可送0.7V-1V左右电压,并适当加长延迟时间,上下限可为20%;

7、三极管除了测两个PN结外,要加做饱和电压测试,即三端测试法,要注意是NPN型的还是PNP型,分别用N模式和P模式;

尤其是基点要找正确,否则饱和电压测不出,一般NPN型实际值电压送0.7V-1V左右,PNP型送3.5V-4.5V,若饱和电压测不出,可往下调整电压;

8、IC的测试首先要找准该IC的VCC及GND,并在IC编辑里分别注明(可按F4键),若IC做HPTESTJET测试的,还要注明该IC的PORT埠(可按F10键)这些设定工作做完后,可进入零件编辑,根据需要进行IC的学习。

注意:

1)ICSCAN学习后,可能会有些IC脚的量测结果很低,可将低PIN针点取消,只留高PIN即IC脚对应针号,然后将量测值做为标准值:

上下限为±

40%;

2)、HPTESTJET的学习可只做SHORT学习,然后将上限定为±

150%,下限定为-50%,这样可测IC的OPEN/SHORT;

9、DEBUG完成后,要连续测试多少遍,然后利用EDIT里面的F6功能,查看组件的稳定与否,对于那些不稳定的组件则需再做调试,使之稳定。

通过以上几大项即可将治具调试好,若要使程序做得更为完美,则需更为细心,对照BOM检查,查看程序里面组件是否都有测试。

最后希望各位技术员、工程师严格按以上条例DEBUG工作,并在工作中探索经验,使所做程序既快捷又稳定。

产品工程部raop2005-6-30

THANKS

沟通无极限,一切构造源自创造……