CAN总线硬件连接及程序.docx

《CAN总线硬件连接及程序.docx》由会员分享,可在线阅读,更多相关《CAN总线硬件连接及程序.docx(26页珍藏版)》请在冰豆网上搜索。

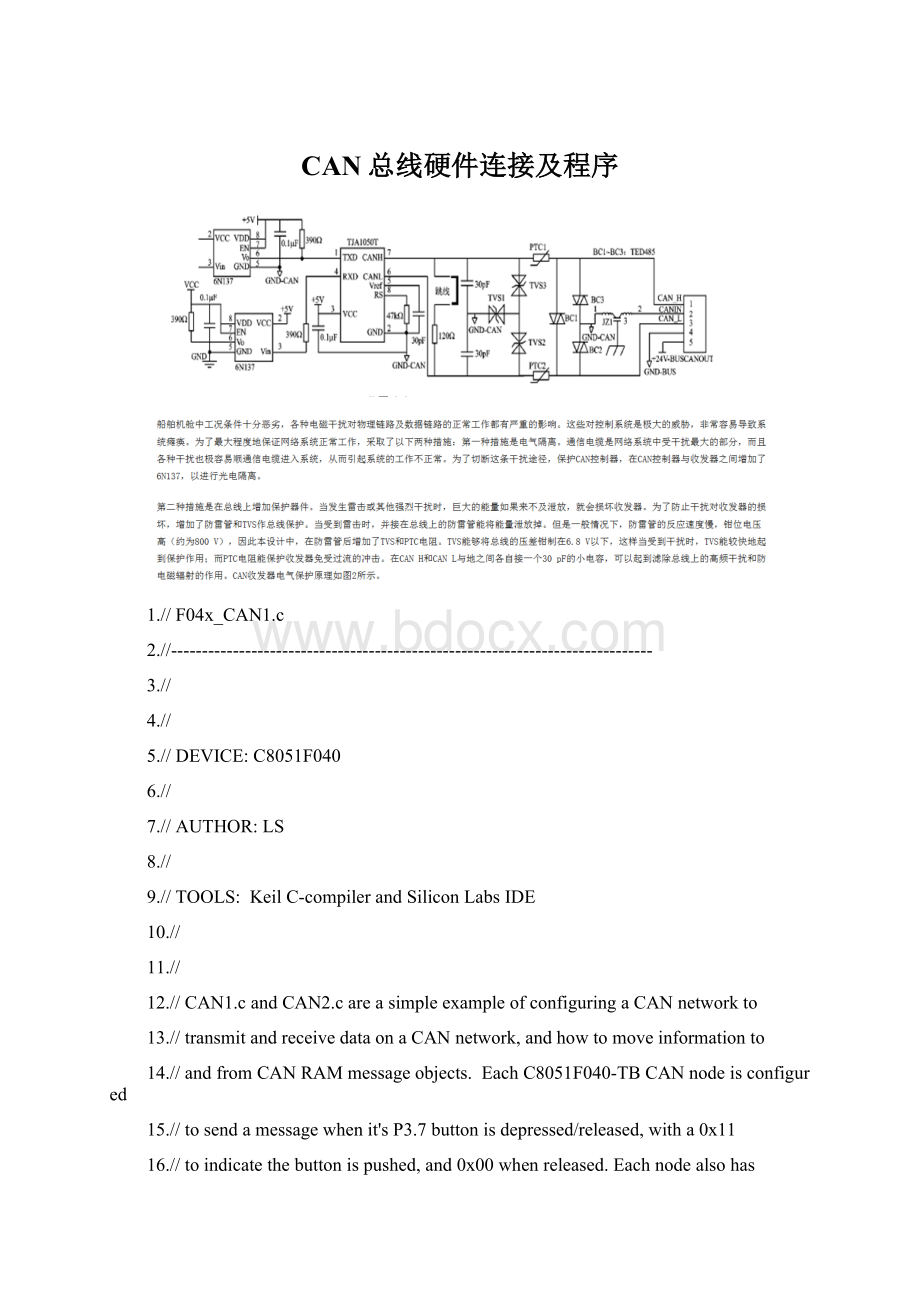

CAN总线硬件连接及程序

1.// F04x_CAN1.c

2.//------------------------------------------------------------------------------

3.//

4.//

5.// DEVICE:

C8051F040

6.//

7.// AUTHOR:

LS

8.//

9.// TOOLS:

Keil C-compiler and Silicon Labs IDE

10.//

11.//

12.// CAN1.c and CAN2.c are a simple example of configuring a CAN network to

13.// transmit and receive data on a CAN network, and how to move information to

14.// and from CAN RAM message objects. Each C8051F040-TB CAN node is configured

15.// to send a message when it's P3.7 button is depressed/released, with a 0x11

16.// to indicate the button is pushed, and 0x00 when released. Each node also has

17.// a message object configured to receive messages. The C8051 tests the

18.// received data and will turn on/off the target board's LED. When one target

19.// is loaded with CAN2.c and the other is loaded with CAN1.c, one target

20.// board's push-button will control the other target board's LED, establishing

21.// a simple control link via the CAN bus and can be observed directly on the

22.// target boards.

23.////////////////////////////////////////////////////////////////////////////////

24.

25.////////////////////////////////////////////////////////////////////////////////

26.// Includes

27.////////////////////////////////////////////////////////////////////////////////

28.

29.#include // SFR declarations

30.

31.// CAN Protocol Register Index for CAN0ADR, from TABLE 18.1 of the C8051F040

32.// datasheet

33.////////////////////////////////////////////////////////////////////////////////

34.#define CANCTRL 0x00 //Control Register

35.#define CANSTAT 0x01 //Status register

36.#define ERRCNT 0x02 //Error Counter Register

37.#define BITREG 0x03 //Bit Timing Register

38.#define INTREG 0x04 //Interrupt Low Byte Register

39.#define CANTSTR 0x05 //Test register

40.#define BRPEXT 0x06 //BRP Extension Register

41.////////////////////////////////////////////////////////////////////////////////

42.//IF1 Interface Registers

43.////////////////////////////////////////////////////////////////////////////////

44.#define IF1CMDRQST 0x08 //IF1 Command Rest Register

45.#define IF1CMDMSK 0x09 //IF1 Command Mask Register

46.#define IF1MSK1 0x0A //IF1 Mask1 Register

47.#define IF1MSK2 0x0B //IF1 Mask2 Register

48.#define IF1ARB1 0x0C //IF1 Arbitration 1 Register

49.#define IF1ARB2 0x0D //IF1 Arbitration 2 Register

50.#define IF1MSGC 0x0E //IF1 Message Control Register

51.#define IF1DATA1 0x0F //IF1 Data A1 Register

52.#define IF1DATA2 0x10 //IF1 Data A2 Register

53.#define IF1DATB1 0x11 //IF1 Data B1 Register

54.#define IF1DATB2 0x12 //IF1 Data B2 Register

55.////////////////////////////////////////////////////////////////////////////////

56.//IF2 Interface Registers

57.////////////////////////////////////////////////////////////////////////////////

58.#define IF2CMDRQST 0x20 //IF2 Command Rest Register

59.#define IF2CMDMSK 0x21 //IF2 Command Mask Register

60.#define IF2MSK1 0x22 //IF2 Mask1 Register

61.#define IF2MSK2 0x23 //IF2 Mask2 Register

62.#define IF2ARB1 0x24 //IF2 Arbitration 1 Register

63.#define IF2ARB2 0x25 //IF2 Arbitration 2 Register

64.#define IF2MSGC 0x26 //IF2 Message Control Register

65.#define IF2DATA1 0x27 //IF2 Data A1 Register

66.#define IF2DATA2 0x28 //IF2 Data A2 Register

67.#define IF2DATB1 0x29 //IF2 Data B1 Register

68.#define IF2DATB2 0x2A //IF2 Data B2 Register

69.////////////////////////////////////////////////////////////////////////////////

70.//Message Handler Registers

71.////////////////////////////////////////////////////////////////////////////////

72.#define TRANSREQ1 0x40 //Transmission Rest1 Register

73.#define TR