基于CPLD的彩色线阵CCD驱动信号的设计11讲解Word文件下载.docx

《基于CPLD的彩色线阵CCD驱动信号的设计11讲解Word文件下载.docx》由会员分享,可在线阅读,更多相关《基于CPLD的彩色线阵CCD驱动信号的设计11讲解Word文件下载.docx(10页珍藏版)》请在冰豆网上搜索。

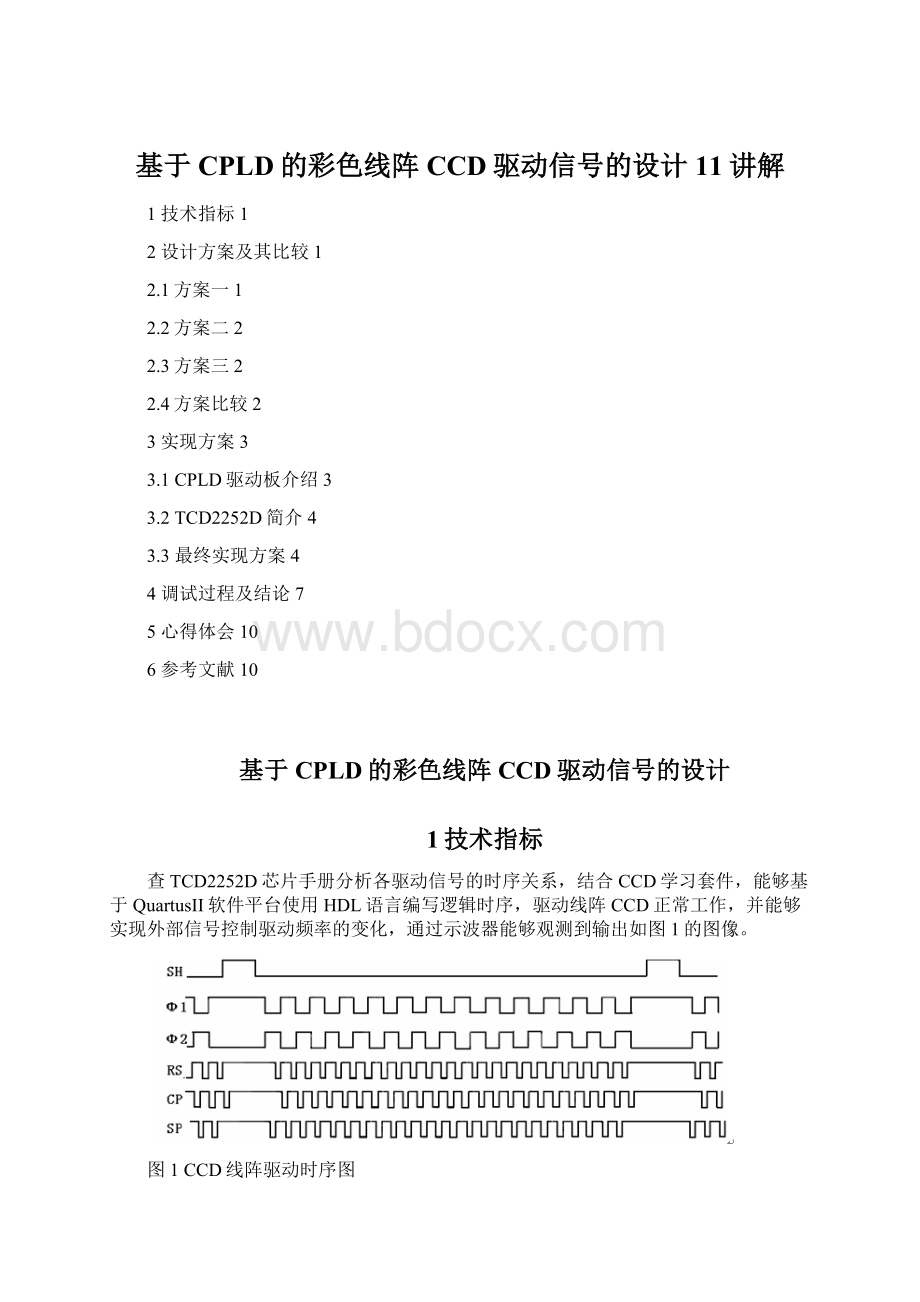

图1CCD线阵驱动时序图

2设计方案及其比较

2.1方案一

方案一为单片机驱动方法。

因为大多是CCD系统里都含有单片机,所以很自然的会联想到单片机的并行锁存输出口所需的驱动脉冲信号,实现对CCD的控制。

单片机靠指令产生I/O口的输出来实现。

由于线阵CCD的典型复位脉冲为1MHz,所以对单片机还是有一定的最低要求。

简易连接图如图2所示。

图2单片机简易连线图

为了获得精确的CCD驱动,最好不要使用循环制性程序。

因为转移指令是要根据某种条件产生的程序分支,而分支程序在不同条件下之行的指令周期数是不同的,因而造成CCD的驱动时序不准确。

但是对于成千的像元的CCD来说,一个工作周期往往需要好多好多字节的程序存储器。

略有麻烦。

2.2方案二

方案二为EPROM驱动方法。

所需的器件TCD1208AP的时序如图3所示。

SH为光积分脉冲信号;

1、2为时钟脉冲信号;

RS为复位脉冲信号;

SP为采样保持脉冲信号。

由图3中的时序可以看出:

在这5个信号中,最窄的是AB段,即SP和RS两个信号的高电平部分,各个信号的任何部分都是AB段的倍数。

根据这一特点,将这组信号以AB段为基本单位划分为若干个等时间间隔,称为状态。

时钟波形电平变化发生在一定状态变化时刻,这样任意一路信号都被分为上万个状态,处于某一状态时,各路信号或1或0,构成一个状态的数据,将数据依次装入可擦除只读存储器EPROM中,只要等时间间隔地依次输出这些数据就形成了CCD所需的各路波形。

图3方案二时序图

2.3方案三

方案三是基于CPLD的设计。

以CPLD器件为核心,设计线阵CCD的驱动电路。

然后在其基础上扩展,选择其他元器件,设计出与其相配套的电路部分,经调试后组成硬件系统。

2.4方案比较

说得好EPROM设计思想十分显然,不论对任何型号的CCD,其硬件结构几乎不需要变化。

只需按CCD的典型驱动波形图,将数据与信号相对应,以及将波形转化成数据即可,设计起来十分简单。

而设计的系统性能稳定,可以进行程序擦除,再开发,但是器件要工作还需要地址发生器,而根据前面分析的结果,要保存一个周期的驱动波形信号需要许多存储量,相应的地址信号也需要更多,设计这么多位的同步计数器又增加了设计工作量,而且电路板面积也随之增大。

另外,存储的数据不能在系统修改。

单片机驱动方法与上面的方法有些相似。

EPROM方法每改变地址就输出新的状态数据,单片机法每改变一次端口输出指令就改变了输出数据。

在这种设计方法中,硬件电路非常简单,但是存在资源浪费较多,频率较低的缺陷。

CPLD设计法实现的系统集成度高、速度快、可靠性好。

系统每一功能模块完成后可单独仿真,整个系统完成时也可在计算机上进行仿真,不需要外部测试仪器就可以检查修改设计中的问题。

所以选用基于CPLD作为实现方案。

3实现方案

3.1CPLD驱动板介绍

CPLD驱动板分为以下几部分:

1)电源模块电源模块:

包括12V电源输入和电压转换模块(12V转5V)

2)时钟模块:

一个50MHz的有源晶振,给CPLD提供时钟输入

3)JTAG模块:

采用JTAG下载方式将.sof程序文件下载到CPLD内;

4)CPLD模块:

CPLD主芯片(EPM7128SLC84);

5)I/O模块:

CPLD芯片其他未使用的引脚;

6)信号处理模块:

2个74系列非门芯片,提高CPLD输出时序的驱动能力,注意是对CPLD输出时序反相输出;

7)CCD模块:

包括芯片和外围工作电路,接收驱动时序,使CCD正常工作。

驱动板实物如图4所示。

图4CPLD驱动板实物

3.2TCD2252D简介

TCD2252D是一种高灵敏度、低暗电流、2700像元的内置采样保持电路的彩色线阵CCD图像传感器。

该传感器可用于彩色传真、彩色图像扫描和OCR。

它内部包含3列2700像元的光敏二极管,当扫描一张A4的图纸时,可达到很高的精度。

其像敏单元数目为2700像元×

3列;

光敏区域为采用高灵敏度和低暗电流PN结作为光敏单元;

相邻光敏列间距为64μm;

时钟为二相(5V);

内部电路为采样保持电路、箝位电路;

彩色滤光片为红、绿、蓝。

3.3最终实现方案

仿真结果如图5所示。

连接图如图6所示。

图5仿真图

图6连接图

最终程序代码如下。

//输入时钟clk频率为50MHZ一个时钟周期为20ns

//二相驱动脉冲信号Φ1和Φ2频率clk/128MHZ

//Frs=Fcp=Fsp=clk/64MHZ

moduleCCD_driver(clk,rst_n,pha1,pha2,SH,SP,RS,CP);

inputclk;

//系统时钟信号

inputrst_n;

//系统复位信号

outputpha1;

//相位1

outputpha2;

//相位2

outputregSH;

outputregSP;

outputregRS;

outputregCP;

regpha1;

reg[31:

0]count;

always@(negedgeclkornegedgerst_n)begin

if(!

rst_n)count=0;

elseif(count>

32'

d177864)count=0;

//SH的整个周期;

else

count=count+1;

end

//产生SH信号

always@(negedgeclk)begin//pha1为高1000ns后SH变高,高电平持续时间2000ns后变低

if(count<

50||count>

150)SH=0;

elseSH=1;

//产生SP信号

always@(negedgeclk)begin//SH信号频率为clk/64,占空比为3:

1

if(count>

=16&

&

count<

216)SP=1;

elseif(count[5:

0]<

6'

d16)SP=0;

elseSP=1;

//产生RS信号

always@(negedgeclk)begin//RS信号频率为clk/64,占空比为3:

=32&

232)RS=1;

d32&

count[5:

0]>

=6'

d16)RS=0;

elseRS=1;

//产生CP信号

=48&

248)CP=1;

d48&

d32)CP=0;

elseCP=1;

//产生pha1pha2信号

always@(negedgeclk)begin//pha1高电平持续时间=t1+t2+t3+t4+t5=4000ns对应200个时钟周期

200)pha1=1;

elsepha1=count[6];

//对时钟128分频

assignpha2=~pha1;

endmodule

4调试过程及结论

首先,我们先把程序烧进CCD驱动板,连接好示波器之后先对六路信号进行一个检查,结果如图7、8、9所示。

实物图如图10所示。

图712波形

图8SH和SP的波形

图9CP和RS的波形

图10调试过程图

在CCD上盖住纸片后波形发生了图11到图12明显的变化。

图11盖住CCD前波形显示图

图12盖住CCD后波形显示图

5心得体会

从一开始的设计好自己的三个方案,找了许多书上网上的资料,整理出三个较好的方案,最后再加以比较得出最终实验原理。

首先安装软件就是一大难题,找了老师同学帮忙之后才安装好,又花了时间学习如何应用软件。

这次设计让我把书本上得到的理论变成了动手实践,学到了很多课本上没有的东西,以前在电脑上仿真还是过于理想化,没有充分考虑过实际问题,真的把器件拿到手之后才会知道会发生什么实际问题。

我觉得这次课程设计我收获了很多,让我知道了自己在理论知识方面略有不足的问题,这有助于我以后学习的时候会端正自己的学习态度,从而学习更多知识。

再一次提高了自己的动手能力,而且明白凡事要有耐心。

这次课设也让我知道了有的时候一个人的能力是远远不够的,团队意识很重要,有时候要发扬团队合作的精神。

这次对我而言,收获的不仅仅是知识,在动手能力方面也有了更大的提高。

可以说整个实验过程还是非常顺利的。

6参考文献