电子技术II实验指导书Word格式文档下载.docx

《电子技术II实验指导书Word格式文档下载.docx》由会员分享,可在线阅读,更多相关《电子技术II实验指导书Word格式文档下载.docx(18页珍藏版)》请在冰豆网上搜索。

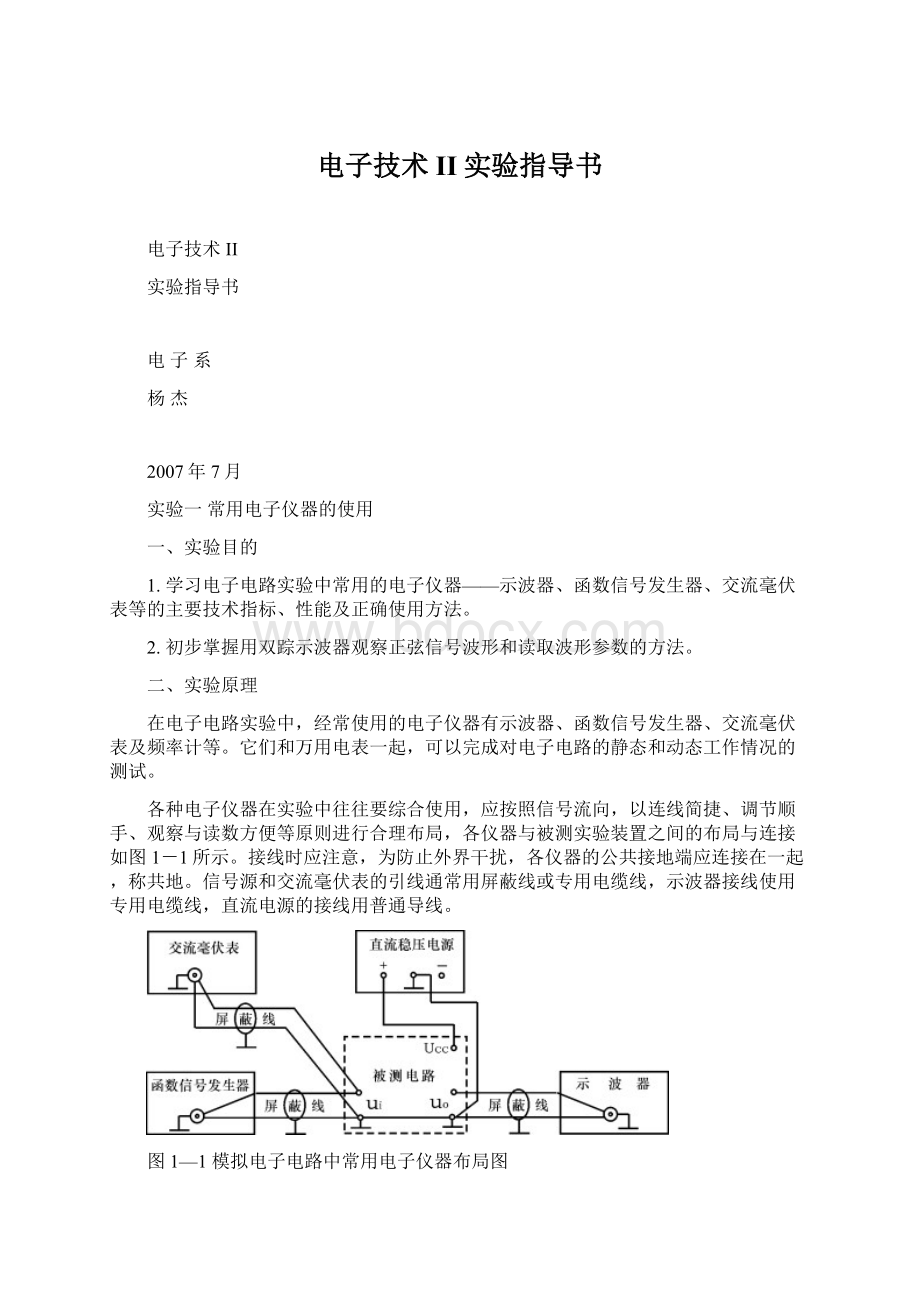

三、实验设备

序号

名称

型号与规格

数量

1

双踪示波器

GOS-6021

2

交流毫伏表

NY4510

3

函数信号发生器

SP1642B

四、实验内容

1.用示波器内校准信号进行自检。

(1)扫描基线调节

将示波器的显示方式开关置于“单踪”显示(CH1或CH2),输入耦合方式开关置“GND”,触发方式开关置于“自动”。

开启电源开关后,调节“辉度INTEN”、“聚焦FOCUS”等旋钮,使荧光屏上显示一条细而且亮度适中的扫描基线。

然后调节“X轴位移”和“Y轴位移”旋钮,使扫描线位于屏幕中央。

(2)显示“校准信号”波形

将示波器面板上的“校正信号”通过专用电缆线引入选定的Y通道(CH1或CH2),将Y轴输入耦合方式开关置于“AC”,触发源(SOURCE)选择置“VERT↑AC”。

调节X轴“扫描速率”开关(time/div)和Y轴“输入灵敏度”开关(Volts/div),使示波器显示屏上显示出一个或数个周期稳定的方波波形。

(3)测量“校准信号”幅度

将“Y轴灵敏度调节”旋钮置于“校准”位置(VAR灯不亮),“Y轴灵敏度”(V/div)开关置适当位置,读取校准信号幅度,记入表1-1。

(4)测量“校准信号”频率

将“X轴灵敏度调节”旋钮置于“校准”位置,“X轴灵敏度”(t/div)开关置适当位置,读取校准信号周期,记入表1-1。

表1-1

项目

幅度

频率

标准值

0.5

1KHz

实测值

一般示波器的校准信号是频率为1KHz、峰值为0.5V的方波,若测量值与之相同,说明示波器工作正常。

2.用示波器和交流毫伏表测量交流信号参数

调节函数信号发生器,使之输出有效值均为1V(50Ω输出端,用交流毫伏表测量),频率分别为100Hz、1KHz、10KHz的正弦波信号。

调节示波器X轴“扫描速率”开关及Y轴灵敏度开关,测量信号源输出电压的频率及峰值

,填入表1-2。

表1-2

信号电压频率

示波器测量值

读数/V

周期/ms

频率/Hz

峰峰值/V

有效值/V(计算)

100Hz

1KHz,

10KHz

五、注意事项

1.函数信号发生器不能短路,交流毫伏表在小量程下不能开路。

2.函数信号发生器、交流毫伏表、双踪示波器等必须采用共地接法。

六、实验结果分析及问题简答

1.交流毫伏表能否测直流电压?

2.能否用数字万用表的交流电压档测量本实验中的信号幅度?

为什么?

3.电子测量中采用共地接法的目的是什么?

说明:

周期(频率)测量法:

1.读格(确认处于校准态)2.用测量游标3.直接读下部数据

电压测量法:

1.读格(确认处于校准态)2.用测量游标3.直接读下部数据(CH1)

实验二晶体管共射极单管放大器

1.学会放大器静态工作点的调试方法。

2.分析静态工作点对放大器性能的影响。

3.掌握放大器电压放大倍数、输入电阻、输出电阻及最大不失真电压的测试方法。

1.由于电子器件是非线形元件,性能的分散性又比较大,在制作晶体管放大电路时,除依据所用元器件的参数进行必要的设计外,还必须对放大器的静态工作点和各项性能指标进行实际调试。

2.图2-1为电阻分压式工作点稳定单管放大器。

它的偏置电路采用RB1和RB2组成的分压电路,并在发射极中接有电阻RE,以稳定放大器的静态工作点。

当在放大器的输入端加入输入信号ui后,在放大器的输出端便可得到一个与ui相位相反,幅值被放大了的输出信号u0。

图2-1单管放大器

3.在图2-1电路中,当流过偏置电阻RB1和RB2的电流远大于晶体管T的基极电流IB时(一般设计时都应满足此条件),它的静态工作点可用下式估算:

电压放大倍数

输入电阻

输出电阻

4.晶体管放大电路的静态工作点是否合适,对放大器的性能和输出波形都有很大影响。

如工作点偏高,放大器在加入交流信号以后易产生饱和失真,此时uO的负半周将被削底,如图2-2(a)所示;

如工作点偏低则易产生截止失真,即uO的正半周被缩顶(一般截止失真不如饱和失真明显),如图2-2(b)所示。

这些情况都不符合放大器不失真放大的基本要求。

5.通常多采用调节偏置电阻RB2的方法来改变静态工作点。

6.为了在输出端得到较大幅度的不失真信号,静态工作点应设置在交流负载线的中点附近。

图2-2(a)饱和失真图2-2(b)截止失真

表2-1

备注

模电实验箱

浙江天煌

4

数字万用表

UT58

5

6

直流稳压电源

GPS-3303C

1.测量静态工作点

按图连接电路,接通12V直流电源,调节RW,使UE=2.0V(即IC=2mA),用数字万用表直流电压档测量UB、UC与UE,数据记录于表2-2。

表2-2

测量值

计算值

UB/V

UE/V

UC/V

UBE/V

UCE/V

IC/mA

2.0

2.测量电压放大倍数

在放大器输入端加入1KHz的正弦信号Us,调节函数信号发生器输出信号大小使Ui(B点与地之间的输入电压)为10mV,用示波器观察放大器输出电压Uo,在输出波形不失真条件下,分别用交流毫伏表测量RL=2.4kΩ和空载情况下的Uo以及函数信号发生器输出信号Us。

数据记录于表2-3。

表2-3

RL/kΩ

Uo/V

Av

Uo—Ui波形相位关系

(用两种颜色画图、标注坐标单位)

2.4

∞

3.观察输入、输出信号的相位关系

用双踪示波器同时观察输入Ui、输出Uo的信号波形,记录其相位关系于表2-2。

4.观察静态工作点对输出波形失真的影响

①置RL=∞。

确认放大器的静态为UE=2.0V(即IC=2mA),用示波器观察输出信号,确认输出无失真(否则重新在无交流信号输入的前提下重调RW)。

②逐步加大函数信号发生器的输入信号,使输出电压u0足够大但不失真。

③保持输入信号不变,减小RW值,使输出波形Uo出现饱和失真,测出相应的UCE、IC,记录于表2-3。

(注:

用测UE的方法测IC:

IC=UE/RE)

④保持输入信号不变,增大RW值,使输出波形Uo出现截止失真,测出相应的UCE、IC,记录于表2-3。

UO波形

失真情况

饱和失真

不失真

截止失真

注:

①用测UE的方法间接测IC。

②每次测静态值IC和UCE等时都要令即使Ui=0(即把信号源的输出旋钮旋至零)。

五、实验报告

1.简答:

若静态工作点偏上,易发生什么失真?

若静态工作点偏下,易发生什么失真?

2.简答:

如果无论怎么调节RB2,在输入不失真得情况下,输出都有明显失真,可能是什么原因?

实验三集成运算放大器的应用(模拟运算电路)

1.研究由集成运算放大器组成的比例、加法、减法和积分等基本运算电路的方法。

2.掌握运算放大器的使用方法,了解其在实际应用时应考虑的问题。

1.集成运算放大器是一种电压放大倍数极高的直接耦合多级放大电路。

当外部接入不同的线性或非线性元器件组成输入和负反馈电路时,可以灵活地实现各种特定的函数关系。

在线性应用方面,可组成比例、加法、减法、积分、微分、对数等模拟运算电路。

2.基本运算电路

几种典型的运算电路如下:

图3-3同相比例运算电路

图3-5uA741管脚排列

1.反相比例运算电路

(1)调零,按图3-1连接实验电路,接通±

12V电源,输入端对地短接,调节Rp,使U0=0。

(2)输入f=100Hz,Ui=0.5V的正弦交流信号,用交流毫伏表测量相应的U0,并用示波器观察ui和u0的波形,填入表3-1中。

注意ui和u0的相位关系。

2.同相比例运算电路

(1)按图3-3(a)连接实验电路。

实验步骤同上,将结果填入表3-1中。

(2)电压跟随器实验,将图3-3(a)中的R1断开,得图3-3(b)电路,重复

(1)的内容。

表3-1(f=100Hz,Ui=0.5V)

Ui/V

AV

ui波形、u0波形

反相比例

同相比例

3.反相加法运算电路

(1)按图3-2连接实验电路,调零和消振。

(2)输入信号采用直流信号,用直流电压表测量输入电压Ui1、Ui2及输出电压Uo,填入3-2中。

4.减法运算电路

(1)按图3-4连接实验电路,调零和消振。

(2)采用直流输入信号,实验步骤同内容3,填入表3-2中。

表3-2

Ui1/V

0.2

–0.2

Ui2/V

0.1

0.3

反相

加法

减法

1.整理测量结果,填写相关表格。

2.把实测值与理论计算值比较,分析误差原因。

3.如果没有交流毫伏表能否完成本次实验?

实验四逻辑门与组合逻辑电路

1.熟悉TTL、CMOS门的逻辑功能。

2.掌握用“与非”门构成其他常用逻辑门电路的方法。

3.掌握组合逻辑电路的分析方法与测试方法。

根据逻辑代数的知识,用“与非”门可实现其他逻辑门的逻辑关系:

Y1=

Y2=

Y3=AB=

Y4=A+B=

Y5=

=

Y6=

实验前按下图给出的Y1-Y6逻辑电路图,根据集成片的引脚排列分配好各引脚。

(a)(b)(c)

(d)(e)(f)

图4-1用“与非”门实现各种基本逻辑关系

数电实验箱

集成芯片

74LS00,74LS86或

CD4011,CD4030

1组

2选1

1.按图4-1(f),分配好74LS00(或CD4011)集成片的各引脚并正确接线,将测试结果填入表4-1,验证其逻辑功能。

表4-1

A

B

Y1

Y2

Y3

Y4

Y5

Y6

2.按下图分配好74LS00和74LS86(或CD4011和CD4030)集成片的引脚,并正确接线,即用“异或”门和“与非”门组成的全加器电路。

图4-2用“与非”门实现“异或”逻辑关系

3.将测试结果填入表4-2,验证其逻辑功能。

图中Ai,Bi为加数,Ci-1为来自低位的进位;

Si为本位和,Ci为向高位的进位信号。

表4-2

Ai

Bi

Ci-1

Si

Ci

1.Y6具有何种逻辑功能?

2.若“或非”门有多余的输入端,应该如何处理?

注意事项

1.TTL逻辑门输入端悬空相当于输入高电平,但实际使用时一般不悬空以免引入干扰。

CMOS逻辑门输入端不允许悬空,多余的输入端必须作相应的处理。

处理的方法是:

或并,或接高电平,或接低电平,使之不影响逻辑功能。

2.看清集成电路的管脚排列位置,切忌电源接错或输出短路,以免损坏集成块。

3.74LS系列只能用5伏电压。

附:

芯片引脚排列(顶视图)

74LS0074LS86

CD4011CD4030

版本信息:

实验三增加标注了运放管脚。

反相减法电路30K改为10K.

实验二增加了IC的测量方法说明。

实验四修改了图4-1(d)输出短接错。

修改了表格4-1中Y2项。