电子时钟设计正文Word文档下载推荐.docx

《电子时钟设计正文Word文档下载推荐.docx》由会员分享,可在线阅读,更多相关《电子时钟设计正文Word文档下载推荐.docx(12页珍藏版)》请在冰豆网上搜索。

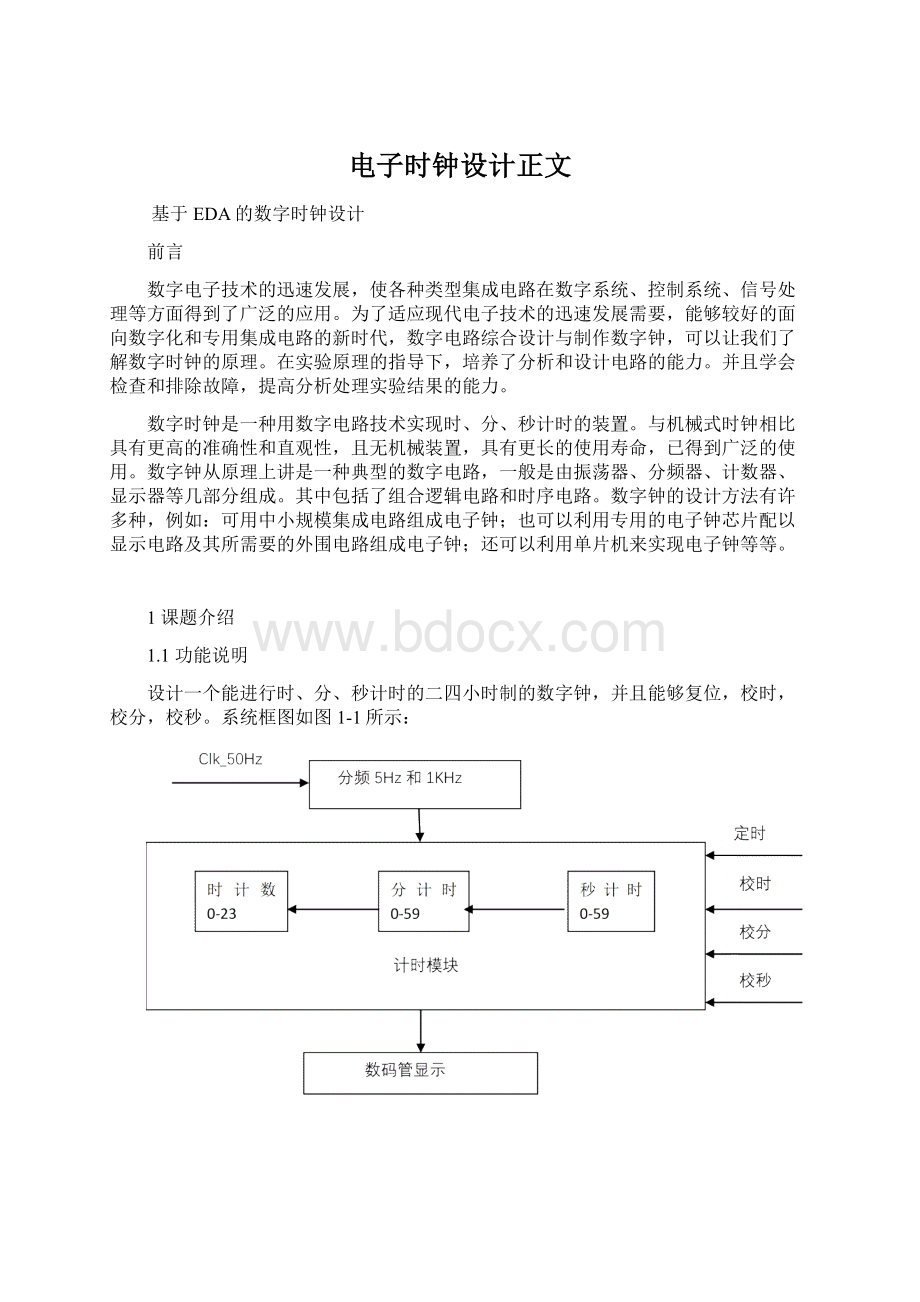

又由于时钟需要进位,所以对计时模块又要分时分秒来处理,最后就是如何实现数码管显示,一个数码管只能显示一个数字,就需要来点亮不同的数码管,并且数字间要建立联系。

此设计问题可分为分频、计时模块和数码管显示三大部。

1.3关于EDA和QuartusII

EDA是电子设计自动化(ElectronicDesignAutomation)的缩写,在20世纪60年代中期从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。

EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

EDA技术的出现,极大地提高了电路设计的效率和可操作性,减轻了设计者的劳动强度。

QuartusII是Altera公司的综合性PLD/FPGA开发软件,原理图、VHDL、VerilogHDL以及AHDL(AlteraHardware支持DescriptionLanguage)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流程。

QuartusII提供了完全集成且与电路结构无关的开发包环境,具有数字逻辑设计的全部特性,包括:

可利用原理图、结构框图、VerilogHDL、AHDL和VHDL完成电路描述,并将其保存为设计实体文件;

芯片(电路)平面布局连线编辑。

2设计方案

整个电路有三大主体电路:

1.分频电路,2.时间控制电路,3,显示时钟电路首先要有输入脉冲,由于平台提供了脉冲发生器,就省去了脉冲发生器的设计,这里我们只需要设计一个分频器,得到我们需要的频率。

时钟的计时范围是00:

00:

00---23:

59:

59,显示是通过分别把时分秒的个位和十位分开送入数码管中来实现。

当需要按键调节时间时,按下对应的按键进行调时。

电路图如图2-1;

2-1总的电路图

3各子模块设计原理

3.1分频模块

根据系统功能需求,此分频模块需要实现两个信号的分频输出,一个是5Hz的信号通过5次叠加提供基准时钟,另一个用于数码管动态显示扫描信号,频率为1KHz。

分频模块如图3-1:

3-1分频模块原件图

3.2计时模块

3.2.1计时和调时

该模块主要是实现0-59和0-23的计数,并且实现秒向分进位,分向时进位。

当按下定时建后,时钟显示会暂停,再按调时按键时可以实现时分秒的调节,调后再按调时键,时钟恢复走时,最后将计数结果的个位和十位分别输出。

时钟模块如图3-2:

3-2时钟模块原件图

3.2.2计时仿真

计时电路模块的仿真如图3-3;

3-3仿真图

3.3显示模块

3.3.1数码管

数码管工作原理,数码管由七个条状和一个点状发光二极管管芯制成,称为七段数码管。

根据其结构的不同,可分为共阳极数码管和共阴极数码管两种。

共阳共阴,是针对数码管的公共脚而说的。

典型的一位数码管,一般有10个脚,8个段码(7段加1个小数点),剩下两个脚接在一起。

各个段码实际上是一个发光二极管,既然是发光二极管,就有正负极。

共阳,也就是说公共脚是正极(阳极),所有的段码实际上是负极,当某一个或某几个段码位接低电平,公共脚接高电平时,对应的段码位就能点亮,进而组合成数字或字母。

共阴是公共脚是负极(阴极),段码位是阳极,当公共脚接地,段码位接高电平时,对应段码位点亮。

根据所用的开发板,采用的是两个四位一体的共阳数码管,一共有8个其电路结构如图3-4,在电路中,数码管的位选信号X1-X8是由三极管控制的,位选信号是低电平有效。

图3-48位共阳数码管电路图

3.3.2译码显示

译码显示就是把时分秒的个位和十位,送入数码管中,并且完成显示。

显示模块如图3-5:

3-5时钟显示模块原件图

3.4系统顶层设计

完成上述功能模块后,需要建立顶层系统设计文件,这里采用原理图设计。

顶层原理图设计方法如下。

1.将分频,时钟,显示各个模块代码用QuartusII的VerilogHDL文本编辑器进行输入,然后将代码按照各自的模块名作为文件名保存到工程文件夹中;

2.然后新建一个工程,将上述3个底层模块设计代码文件添加进工程,并分别进行封装成为可以被原理图文件所调用的元件符号文件;

3.新建一个原理图设计文件,利用原理图设计方法和步骤,完成顶层设计;

4.编译仿真,先编译,编译成功后就是分配管脚,管脚分配如图3-6。

3-6管脚分配图

4设计结果

经过多次的更改.编译和仿真,最后在开发板上显示的效果如图4-1

4-1效果图

5收获与体会

通过本次实验,我知道了自己许多知识的不足,同时也知道了许多操作的不熟练,在软件应用上有很大的不足,让我对许多知识重新熟悉,巩固。

在编程的过程中,我发现了自己的编程习惯不好,写出的程序不是多就是少,导致浪费了许多时间。

在模块设计过程中,考虑不够详细,为最后的编译留下了不少的问题。

其次就是对开发板的原理图不够了解,在设置管脚的时候也出了错。

当然最后这些问题都一一的改了过来,在改的过程中,我对软件也越来越熟悉,编写程序的思维也更加的清晰,对VerilogHDL语句也更加的熟悉,最大的收获就是我喜欢上了这个,感觉很有意思。

这个设计的不足在于计时没有声音也没有整点报时的功能。

在做实验过程中是对耐心的考验,特别是在出错时锻炼了自己的耐力,也是对自己的一种提升。

6附录

分频设计

modulefenpin(clk_50M,clk_1HZ,clk_1kHZ);

inputclk_50M;

outputclk_1HZ;

outputclk_1kHZ;

regclk1,clk1k;

reg[24:

0]counter1;

reg[14:

0]counter2;

always@(posedgeclk_50M)

begin

if(counter1==5000000)

begin

counter1<

=0;

clk1<

=~clk1;

end

elsecounter1<

=counter1+1;

end

if(counter2==25000)

counter2<

clk1k<

=~clk1k;

elsecounter2<

=counter2+1;

assignclk_1HZ=clk1;

assignclk_1kHZ=clk1k;

endmodule

计时设计

moduleshizhong(clk,rst,sec_ge,sec_shi,min_ge,min_shi,hours_ge,hours_shi,key1,key2,key3,key4);

inputclk,rst,key1,key2,key3,key4;

output[3:

0]sec_ge,sec_shi,min_ge,min_shi,hours_ge,hours_shi;

reg[5:

0]sec,min,hours,cout;

regflag;

assignsec_ge=sec%10;

assignsec_shi=sec/10;

assignmin_ge=min%10;

assignmin_shi=min/10;

assignhours_ge=hours%10;

assignhours_shi=hours/10;

always@(posedgeclk)

if(key1==0)flag<

=~flag;

always@(posedgeclkornegedgerst)

begin

if(!

rst)

sec<

min<

hours<

end

elseif(flag==0)

begin

cout<

=cout+1;

if(cout==5)

begin

cout<

sec<

=sec+1;

if(sec==59)

begin

sec<

min<

=min+1;

if(min==59)

begin

min<

hours<

=hours+1;

if(hours==23)hours<

end

end

elseif(key2==0)

sec<

elseif(key3==0)

min<

elseif(key4==0)

hours<

end

endmodule

显示设计

moduledisplay(clk,sec_ge,sec_shi,min_ge,min_shi,hours_ge,hours_shi,led7_cs,led7);

inputclk;

input[3:

output[7:

0]led7;

0]led7_cs;

reg[7:

reg[3:

0]a;

reg[2:

0]add;

always@(posedgeclk)

add<

=add+1;

end

always@(add)

case(add)

0:

begina<

=sec_ge;

led7_cs<

=8'

b11111110;

end

1:

=sec_shi;

b11111101;

2:

=10;

led7_cs<

b11111011;

3:

=min_ge;

led7_cs<

b11110111;

4:

=min_shi;

b11101111;

5:

b11011111;

6:

=hours_ge;

led7_cs<

b10111111;

7:

=hours_shi;

b01111111;

default:

led7_cs<

b11111111;

endcase

always@(a)

case(a)

led7<

b11000000;

b11111001;

b10100100;

b10110000;

b10011001;

b10010010;

b10000010;

b11111000;

8:

b10000000;

9:

b10010000;

10:

endcase

endmodule

参考文献:

[1]程周:

可编程序控制器原理与应用,高等教育出版社,2006.4,P3-P7

[2]袁本荣、刘万春、贾云得、朱玉文:

微计算机信息(测控仪表自动化),2004年6期

[3]吴中俊、黄永红:

可编程序控制器原理及应用,机械工业出版社,2008.8,P52-P57

[4]王兆义:

实时服务可编程序控制器教程,机械工业出版社,2007.7,P15-P27

[5]彭保、范婷婷、马建国:

微计算机信息,2004年10期

[6]徐大诏、XUDa-zhao:

信息技术,2009年12期

[7]潘松,《EDA实用教程》,科学出版社,2004年

[8]朱如琪,《数字电子技术基础》,华中科技出版社,2005