数据采集完整系统基本原理Word文件下载.docx

《数据采集完整系统基本原理Word文件下载.docx》由会员分享,可在线阅读,更多相关《数据采集完整系统基本原理Word文件下载.docx(18页珍藏版)》请在冰豆网上搜索。

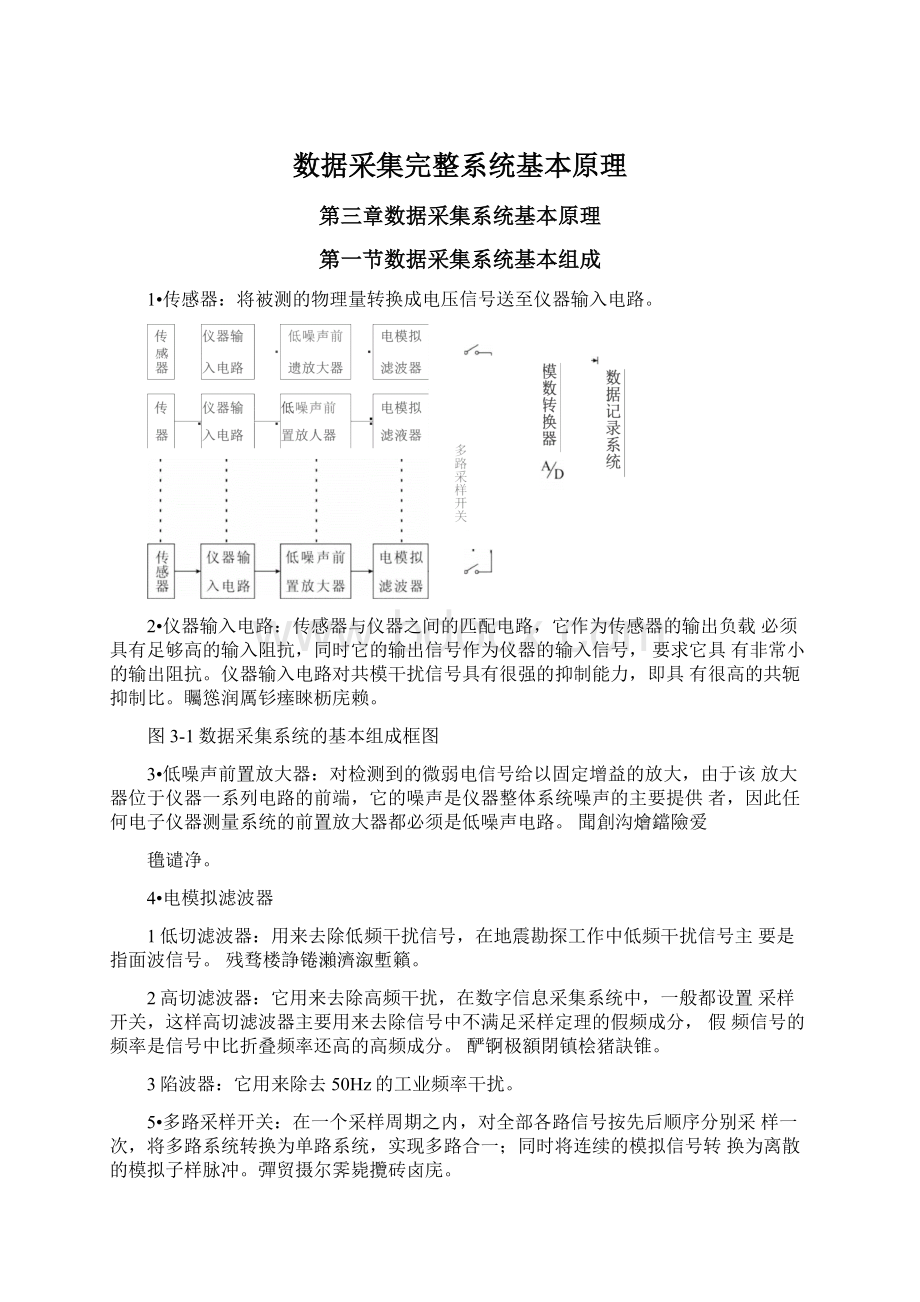

1•对前置放大器的噪声要求

在没有信号输入(放大器入口接地)的情况下,由于内部噪声源的存在,放大器仍有输出信号,该信号即为放大器的噪声。

把放大器电路输出端测得的噪声有效值V除以该电路的增益K,即得到放大器的等效输入噪声Ein=Vn/K

以三级放大器为例,输出噪声为:

Vn「(EK飞K2(E2k2K3(E32K3

等效输入噪声为:

曰2+宜2+丄"

J丿<

K1K2丿

针对集中式地震数据采集系统,前置放大器、滤波器、多路转换开关、浮点

放大器(主放)和模数转换器为五个互不相关的噪声源,等效输入噪声为:

茕桢

广鳓鯡选块网羈泪。

等效输入噪声反应了仪器实际所能记录的最小信号的幅度Vimin(即

主放1:

1

Vimin=E.)o输入信号一旦小于等效输入噪声,输入信号将被仪器噪声所淹没(即信噪比小于1)。

从上述分析可以看出,系统整体等效输入噪声主要由前置放大器提供,同时较大的前置放大器的增益可以有效减少后继电路噪声的影响。

鹅娅

尽損鹌惨歷茏鴛賴。

前放1:

11:

2•双端输入单端输出型前置放大器电路

两个反向器的输出之间的电位差为V,,V,是以Q为主的第一级负反馈放大

器的输出,放大倍数为:

^12Ro

增益为:

Rf2

"

飞,放大器总的增益为:

K=K1K2

在下面的第二个电路实例中,放大器的闭环增益为:

一〔1唱

第三节电模拟滤波器

一、低切滤波器

1、二阶有源低切滤波器

低切滤波器的作用是消除面波为主的低频干扰,根据节点电位法:

Ri

,譜wsws

C2S1V。

二V0C2S

、R2丿

解上方程组可得以拉氏变换形式表示的系统传递函数为

图3-7二阶有源低切滤波器

■'

0C1C2C1C2R1R2

Q=

S2

则HS二

2COo2

S-S0

Q

该滤波器的频率响应及其幅频特性为

①令f0=12HZ,尺二&

二R;

由上式推得:

R=13.271,有Q=0.5

②令f0=12HZR2=kR,Q=1A?

2,可得:

k=2,R=9.380

③令f0=12HZR2=kR,Q=1,求出:

k=4,R=6.68Q

这样便得到在相同截止频率,不同品质因数下的幅频曲线对比图如图3-8

2、

统

DFS-V数字地震仪三阶有源低切滤波器

DFS—V数字地震仪三阶有源低切滤波器如图3-9。

Go=5二缶=1.0」F,

」用c表示,用节点电慰法列写各节点电位方程组籟丛妈羥为贍债蛏练淨。

(cS+cS十一)M=McS+V2cS

Ra

(cScS丄)V2二McSVocSVo

RBRb

丄1

(cS+——)V0=V2cS

Rc.

DFS-V三阶有源低切滤波器

参数表

截止频率(Hz)

RA

RB

RC

3.5

18.53k

17.51k

142.3k

12

5.490k

5.04k

42.15k

5.3

12.35k

11.34k

94.83k

18

3.660k

3.36k

28.10k

8

8.230k

7.56k

63.22k

27

2.44k

2.24k

18.73k

由此可以导出拉氏变换形式的系统传递为

上式中的电容C=Cio=Cii=Ci2,低切滤波器的截止频率为

2:

C3—2RaRbR「

它的陡度为18dB/oct。

该低切滤波器的频率特性曲线如图3-10,从左到右依次是截至频率为3.5HZ、5.3HZ、8HZ12HZ18HZ27HZ的三阶有源低切滤波器和512HZ高切滤波器的幅频特性曲线。

預頌圣鉉儐歲龈讶骅籴。

二、高切滤波器(去假频滤波器)

1、二阶有源高切滤波器

将二阶有源低切滤波器的电阻和电容的位置对调后就得到二阶有源高切

滤波器如图3-11所示,由节点电位法:

V

R2

=gsF)v°

r2

导出传递函数

GC2R|R2

111

+S+

R2jGC1C2R|R2

可得幅频特性

其中

-■(?

s2

fo2Q2

2兀2兀JgC2RR2

Qv'

C1C2RlR2

RR2C2

用同样的分析方法,令f0=64HZ:

①令g=C2=1.0PF,R=R2,由(3-27)推出:

R=R=2.49K0,Q=0.5;

图3-12二阶有源高切滤波器对比

2令R二R=2.49K「,C2二kG,Q=,由(3-27)推出:

k=0.5,g=8.87」F

3令R,=R2=2.49K」,c2二g,Q=1,由(3-27)推出k=0.25,q=2.0」F渗釤呛俨匀谔鱉调硯錦。

用上述三个参数组可以画出相同截止频率,不同品质因数下的二阶有源高切滤波器的幅频曲线如图3-12。

从图中可以看出,在相同截至频率下,Q值越小,

曲线越平滑。

铙誅卧泻噦圣骋贶頂廡。

2、DFS-V数字地震仪去假频滤波器组成原理

为了将陡度提高到70dB/oct以上,DFS-V数字地震仪采用两个不对称有源双梯网和一个二阶有源高切滤波器级联组成去假频滤波器。

第一级有源双梯网的陷波点接近于折迭频率fn,第二级有源双梯网的陷波点高出第一级的30%二阶

有源高切滤波器四分之一采样频率。

擁締凤袜备訊顎轮烂蔷。

图3-14DFS—V高切滤波器电路

截止频率fc(Hz)

R1(Q)

R2Q)

R3(Q)

R4(Q)

R5(Q)

R6(Q)

R7(Q)

R8(Q)

R9(Q)

32

15128

9416

18370

46066

9550

26460

41640

64

7564

4708

9185

23033

4775

13230

20820

128

3782

2354

4592

11516

2338

6615

10410

256

1891

1177

2296

5758

1194

3307

5205

f/Hz

fZHz

图3-13DFS—V高切滤波器组成框图及其幅频特性曲线

电路分析以第一级双梯网络为例它的传递函数为

R1R2

陷波点为fi,fo为固有频率(foVfi,例如:

截止频率为32Hz时,Ri=R2=1512&

」,

R3=9416「,故fo=27Hz,f1=63Hz。

),它等于折迭频率。

贓熱俣阃歲匱阊邺镓騷。

三、陷波器

由于陷波器只对一个频率进行衰减,同时又尽可能地通过其它频率成份,

所以要求陷波器的幅频特性曲线具有更高的陡度,有很窄的切口。

坛搏乡囂忏蒌鍥铃

氈淚。

DFS-V陷波器电路

陷波器电路参数表

陷波频

率/Hz

电阻值/Q

R1

R3

R4

R5

50

206

10604

2294

44130

45016

60

8728

36631

37513

16.6

453

31929

5045

131269

135047

DFS-Vift震仪陷波器幅频特性

图3-17DFS-V陷波器幅频特性

图中由运算放大器AR和R4R5R2C1、C2C3组成有源双梯网络,传递

函数为:

H(S)=——s2+&

S+讥

其中:

心n%=(1-m(1+nC「

RR5C2C3QV.R^C3R5C2C3J

n-C2+C3=2,m=R3。

GR+R3

第四节多路采样开关(MUX)

一、多路采样开关的基本功能

在一个采样周期之内,多路采样开关对全部各路信号按先后顺序分别采样一次,将多路系统转换为单路系统,实现了多路合一;

同时将连续的模拟信号转换为离散的模拟子样脉冲(即采样)。

蜡變黲癟報伥铉锚鈰赘。

图3-18集中式地震仪地震道组成框图

二、多路采样开关应用实例(DFS—V型MUX)買鯛鴯譖昙膚遙闫撷凄。

DFS-V型地震仪的每个模拟箱体可容纳60个地震道,前放滤波和多路采样开关每6道组装在一块FM板上,共有10块FM板。

图中3~S6为每块板上

綾镝鯛駕櫬鹕踪韦辚糴。

图3-19DFS—V型MUX组成

的6个道开关,A1~A;

0为10块FM板上的串联开关,A;

〜a20为10块FM板

上的并联开关。

每个采样周期内,按先后顺序依次采板上的子样,

当采某一块板上的地震道时,该块板的串联开关接通,并联开关断开,6个道

开关依次交替接通。

不被采样的板,其串联开关断开,并联开关接通。

驅踬髏彦浃

绥譎饴憂锦。

多路转换开关板地址译码表

采样板

序号

板地址代码BAE

板

2

地

3

址

4

译

5

码

6

输

7

出FM*1〜10

10

08

04

02

01

9

板串联开关及并联开关的控制指令为FM;

。

当FM*=0时,第i块FM板的串联开关接通,并联开关断开;

FM;

=1时,第i块FM板的串联开关断开,并联开关接通。

〜FM;

0按先后顺序出现0电平,则先后完成第一至第十块FM猫虿驢绘燈鮒诛髅貺庑。

道路转换开关道地址译码表

采样道地址代道地址译码器输出

道040201012345

001101

30101

4011111011

5100111101

6101111110

板的采样工作。

板地址控制代码为BAE-08、04、02、01,该代码经译码后输出

十个板开关控制指令。

每个FM板上六个道开关的控制端来自于道地址译码器的输出。

道地址代码为CA104.02.01,CAE代码从000变化到101,依次完成六个道的采样工作。

锹籁饗迳琐筆襖鸥娅薔。

三、多路采样开关控制原理

構氽頑黉碩饨荠龈话骛。

第五节模数转换器(A/D)

一、逐次逼近型A/D基本原理

1、逐次逼近型A/D基本组成

T网及T网开关电路产生权电压Vt,码寄存器存储比较器每次的比较结果

BRL。

权电压Vt与子样比较,若子样大于Vt,则位取舍电平BRL=1,控制码寄存器的第一位为1,表示取用该位,电路仍产生第一位的权电压;

反之,BRL=0,表示该位被舍去,控制码寄存器的第一位为0,电路不再产生第一位的权电压。

接下来的第二、第三、……、最后一位,逐位均进行相同的判断量化过程,所有各位判断完成后,码寄存器的并行输出即为A/D转换结果。

輒峄陽檉簖疖網儂號泶。

an-1.a0

图3-22逐次逼近型A/D组成框图

尧侧閆繭絳闕绚勵蜆贅。

2、逐次逼近型A/D转换原理示例

举例:

用四位A/D转换器对输入电压M「10.3mV进行量化。

如图3-33所示,其中量化电平为q=1.0mV。

码寄存器的初始状态:

Qi=Q2=Q3=Q4=0,梯网开关Si~S4均接地,权电压Vt=0mV。

1节拍G出现上跳沿时,S,接16mV电源,Vt二,8mVvV^10.3mV,位取舍电平BRL=1判断为取,码寄存器Q1=10识饒鎂錕缢灩筧嚌俨淒。

2节拍C2出现上跳沿时,S1、S2接16mV电源,Vt二•12mV>

V^10.3mV,位取舍电平BRL=0判断为舍,码寄存器Q?

=0。

凍鈹鋨劳臘错痫婦胫籴。

3节拍C3出现上跳沿时,Si、S接16mV电源,Vt=【10mVv

10.3mV,位取舍电平BRL=1判断为舍,码寄存器Q^10恥諤銪灭萦欢煬鞏鹜錦。

4节拍C4出现上跳沿时,Si、S3、S4接16mV电源,Vt=,11mV>

Vjn【10.3mV,位取舍电平BRL=0判断为舍,码寄存器Q4=0。

鯊腎鑰诎漣鉀沩懼統庫。

A/D转换器量化的最后结果为Q1Q2Q3Q4=1010,代表+10mV的电压。

图3-23四位逐次逼近型A/D原理示意图

、逐次逼近型A/D应用实例(DFS-V型A/D)

1•二采保持工作

在此期间,输入开关和二采开关中的串联开关接通,并联开关断开,反相

积分器和差值放大器构成闭环负反馈放大器,对输入子样进行-0.58倍放大:

硕

癘鄴颃诌攆檸攜驤蔹。

2.A/D转换器量化工作

在此期间,输入开关和二采开关中的串联开关断开,并联开关接通。

首先确定符号位,这时权电压仍然为零(Vt=O)。

子样为正时,Vc=—0.58ViV0,所以VnV0,位取舍电平BRL=1;

子样为负时,Vc=—0.58Vi>

0,所以Vn>

0,位取舍电平BRL=0。

BRL去符号位码寄存器,在Q端输出符号位S,所以S=0代表正;

S=1代表负。

子样符号确定以后开始量化,这时权电压不为零(Vt工0)。

由

于保持电压Vc是样电压的0.58倍,则此时要求权电压也应该是正常值(4096mV、2048mV、1024mV、512mV、……、2mV、1mV、0.5mV)的0.58倍,故在原理分析时可以不考虑系数0.58。

阌擻輳嬪諫迁择植秘騖。

(1)子样为负时,权电压也为负值(VtV0),T网逐次产生一4096mV、

—2048mV、…、—1mV、—0.5mV,逐次加入权电压、逐次比较、逐次判断取与舍。

当负子样绝对值大于权电压绝对值时,Vn>

0,BRL=0,判断为取;

当负

子样绝对值小于权电压绝对值时,VnV0,BRL=1,判断为舍。

氬嚕躑竄贸恳彈濾颔澩。

(2)子样为正时,权电压大于零(Vt>

0),T网首先产生的权电压为

+4096+2048+1024+1024S=+8192mV,正好为所有正的权电压之和

(+4096+2048+1024+…+0.5),所以相当于在量化开始时,将所有的权电压都加入。

试4096位时,产生一个—4096mV加入作和,相当于取出了+4096mV,判断为取时,再取消—4096mV;

判断为舍时,就继续产生—4096mV加入作和。

以相同的方式对2048位、1024位1位、0.5位进行试码和判定。

当正子样大

于权电压时,VnV0,BRL=1,判断为取;

当正子样小于权电压时Vn>

0,BRL=0,判断为舍。

釷鹆資贏車贖孙滅獅赘。

A/D输出

图3-30DFS—V型A/D组成框图

综上所述,DFS—V型A/D转换器针对正负两种子样,位取舍电平BRL不同。

BRL=1时,正子样代表取,负子样代表舍;

BRL=0时,正子样代表舍,负子样代表取。

由此就决定了DFS—V型A/D转换器输出结果数据为反码。

怂阐

譜鮫迳導嘯畫長凉。

图3-31二采保持等效电路