集成电路课程设计四位加法器 实验报告Word下载.docx

《集成电路课程设计四位加法器 实验报告Word下载.docx》由会员分享,可在线阅读,更多相关《集成电路课程设计四位加法器 实验报告Word下载.docx(18页珍藏版)》请在冰豆网上搜索。

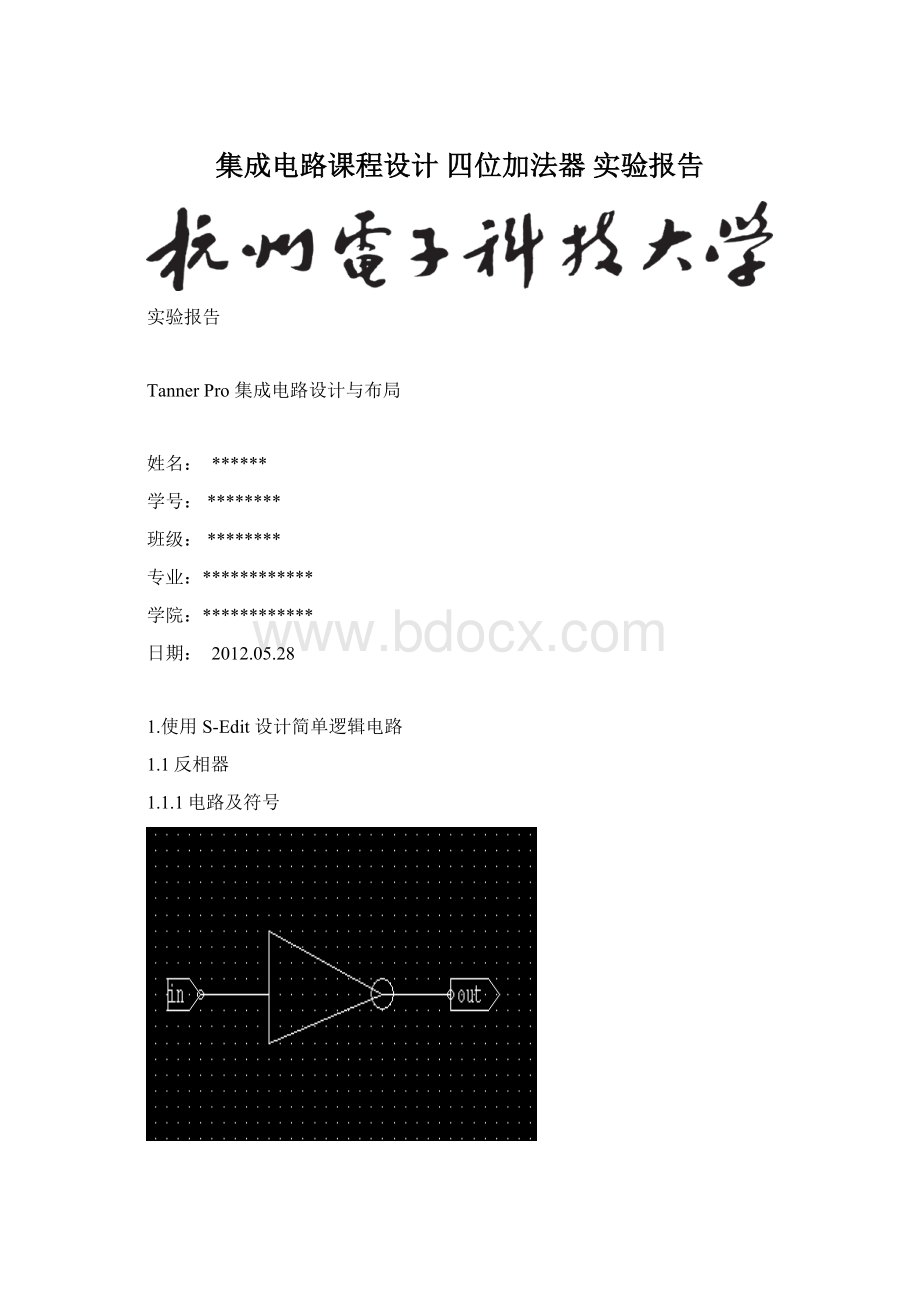

1.1反相器

1.1.1电路及符号

1.1.2反相器直流分析:

.include"

C:

\Users\meng\Desktop\e005_tanner\tanner\TSpice70\models\ml2_125.md"

.dclinsourcevin05.00.02*Vin为0到5v以0.02v增加

.printdcv(OUT)*观察输出

vinINGnd1.0

vvddVddGnd5.0

1.1.3在W-Edit中观看模拟结果如下:

1.2与非门:

1.2.1电路及符号

1.2.2与非门直流分析

.dclinsourceva05.00.1

*SPICEnetlistwrittenbyS-EditWin327.03

*WrittenonJan3,2004at01:

02:

58

.dclinsourceva05.00.1sweeplinparamvb05.01%模拟输入电压va从0V变动到5V时(以0.1V线性增加),vb从0V变动5V时(以1V线性增加)

.printdcv(OUT)%观察输出

vaAGnd5.0

vbBGnd1.0

1.2.3在W-Edit中观看模拟结果如下:

1.3.三输入与非门:

1.3.1电路及符号:

1.3.2三输入与非门直流分析:

Maincircuit:

nand3

M1outinaN2GndNMOSL=2uW=4uAD=66pPD=24uAS=66pPS=24u

M2N2inbN1GndNMOSL=2uW=4uAD=66pPD=24uAS=66pPS=24u

M3N1incGndGndNMOSL=2uW=4uAD=66pPD=24uAS=66pPS=24u

M4outinaVddVddPMOSL=2uW=8uAD=66pPD=24uAS=66pPS=24u

M5outinbVddVddPMOSL=2uW=8uAD=66pPD=24uAS=66pPS=24u

M6outincVddVddPMOSL=2uW=8uAD=66pPD=24uAS=66pPS=24u

vbinbgnd1.0

vainagnd1.0

vcincgnd1.0

vvddvddgnd5.0

*Endofmaincircuit:

.dclinsourceva05.00.1sweeplinsourcevb05.01sweeplinsourcevc05.01

.printdcv(out)

1.3.3在W-Edit中观看模拟结果如下:

1.4.三输入或非门:

1.4.1电路及符号

1.3.2三输入或非门直流分析:

*Maincircuit:

nnor3

M1outinbGndGndNMOSL=2uW=4uAD=66pPD=24uAS=66pPS=24u

M2outinaGndGndNMOSL=2uW=4uAD=66pPD=24uAS=66pPS=24u

M3outincGndGndNMOSL=2uW=4uAD=66pPD=24uAS=66pPS=24u

M4outinbN3VddPMOSL=2uW=8uAD=66pPD=24uAS=66pPS=24u

M5N3inaN7VddPMOSL=2uW=8uAD=66pPD=24uAS=66pPS=24u

M6N7incVddVddPMOSL=2uW=8uAD=66pPD=24uAS=66pPS=24u

1.4.3在W-Edit中观看模拟结果如下:

1.5一位全加器:

1.5.1电路及符号

1.5.2一位全加器直流分析:

.param1=0.5u

vaagndPULSE(0550n5n5n50n100n)

vbbgndBIT({0011}lt=50nht=50non=5rt=5nft=5n)

vcicigndPWL(0ns0v200ns0v205ns5v400ns5v)

.tran/op1n400nmethod=bdf

.printtranv(a)v(b)v(ci)v(s)v(co)

1.5.3在W-Edit中观看模拟结果如下:

1.6四位全加器:

1.6.1电路及符号

1.6.2四位全加器直流分析:

\DocumentsandSettings\Administrator.LENOVO-9011394C\桌面\09045401\集成电路综合设计\e005_tanner\tanner\TSpice70\models\ml2_125.md"

.paraml=0.5u

vvddVddGND5.0

.vectorA{A3A2A1A0}

.vectorB{B3B2B1B0}

vaAGNDBUS({0011111011001010}lt=50nht=50non=5off=0rt=5nft=5n)

vbBGNDBUS({1101011110100101}lt=50nht=50non=5off=0rt=5nft=5n)

.tran/op1n200nmethod=bdf

.printtranv(Cout)v(S3)v(S2)v(S1)v(S0)

1.6.3在W-Edit中观看模拟结果如下:

2.使用L-Edit画布局图

2.1PMOS版图:

2.2NMOS版图:

2.3输入端口的绘制PortA:

以上PMOS、NMOS、节点、端口在画反相器版图时需调用,本次实验中调用初始遇到问题,用copy不能把他们复制进去调用,需要用instance:

2.4PMOSNMOS基板节点组件

PMOS基板节点组件NMOS基板节点组件

2.5反相器版图

2.64位全加器的版图

2.7T-Spice模拟:

M1OUTAGNDPMOSL=2uW=5u

M2OUTAGNDPMOSL=2uW=5u

vvddVddGND5

vaAGNDPULSE(0505n50n100n)

.printtranv(A)v(OUT)

*TotalNodes:

4

*totalElements:

2

3.DRC报告文件

DRCbyTannerResearch'

sL-EditVersion9.00

File:

D:

\集成电路综合设计\e005_tanner\tanner\LEdit90\add4\EX14.tdb

Cell:

Lights

Date:

SunMay2722:

30:

132012

BinSize=100.0000locatorunits

0errors.

0warnings.

Selectlayergenerationelapsedtime:

00:

00:

00(0.00%).

Merge/Booleanlayergenerationelapsedtime:

04(57.14%).

DRCrulecheckingelapsedtime:

03(42.86%).

TotalDRCelapsedtime:

07.

4.使用LVS对比反相器:

生成的inv.spc文件:

LVS对比:

但是对比出错:

反相器LVS始终对比不出,错误如上,但修改多次终于成功。

5.实验总结:

通过本学期的集成电路课程设计的学习,我基本上了解了e005_tanner软件的使用方法。

在这个学期里,我使用了S-Edit、T-Spice、L-Edit三个软件。

分别用来画电路原理图,仿真波形以及画布局图。

在这个实验中,S-Edit最好学,只需要按照原理图放置元件即可,T-Spice次之,在仿真时,很容易出错,需要一步步设置。

最难的就是L-Edit,每做一步都需要设计规则检验,找出错误,修改完之后才能进行下一步的工作,该过程需要细心和耐性。

在L-Edit设计nmos和pmos时经常犯错误,找不出原因,每每都需要请教老师和同学。

设计反向器时,调用nmos和pmos,该过程在前两个步骤之后,操作起来比较容易了。

通过设计一位加法器,然后调用一位加法器来完成4位加法器的设计,该思路很好。

在平时电路设计当中,思路很重要,教会我们解题的技巧。