6050初始化定义文档格式.docx

《6050初始化定义文档格式.docx》由会员分享,可在线阅读,更多相关《6050初始化定义文档格式.docx(13页珍藏版)》请在冰豆网上搜索。

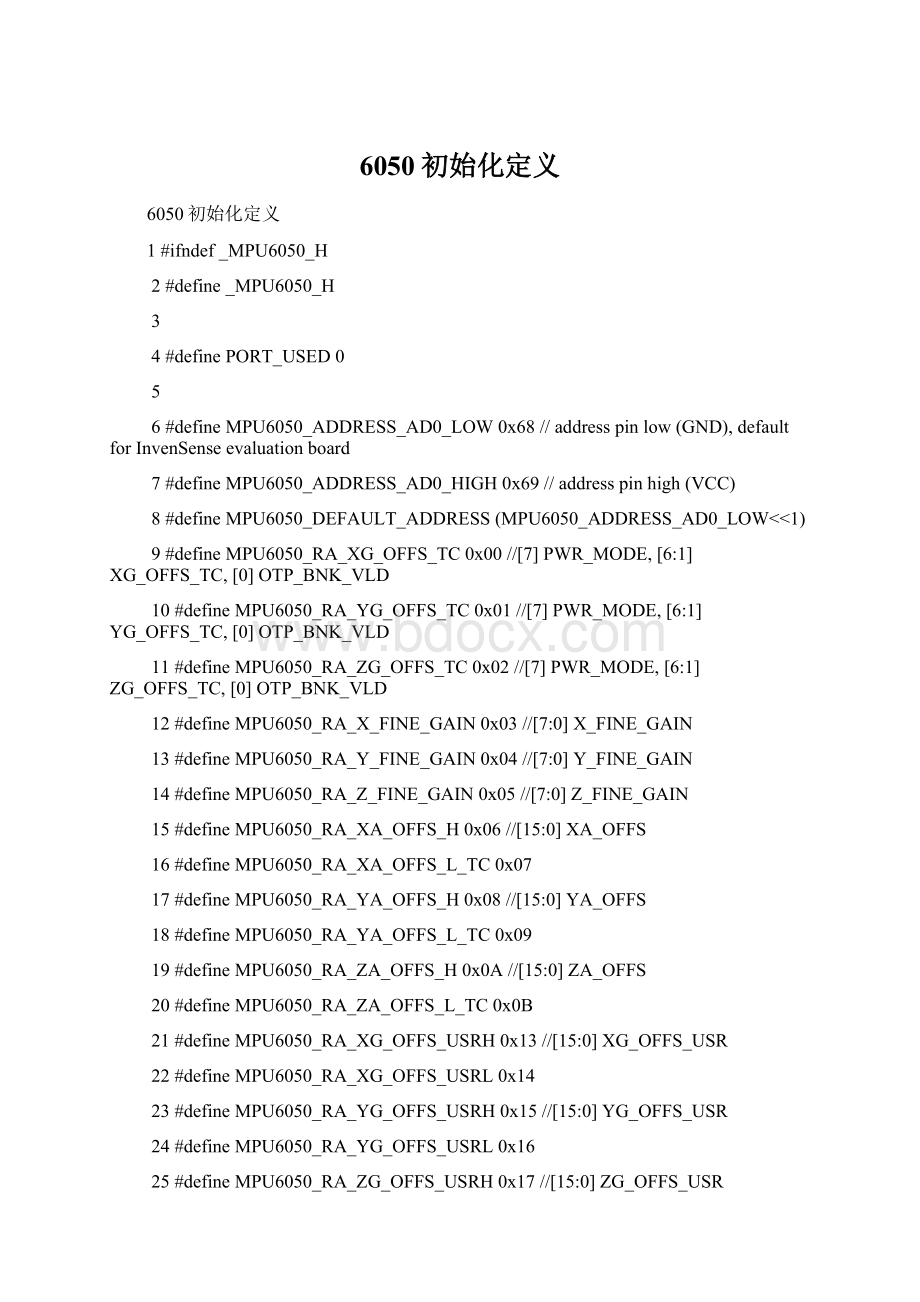

17#defineMPU6050_RA_YA_OFFS_H0x08//[15:

0]YA_OFFS

18#defineMPU6050_RA_YA_OFFS_L_TC0x09

19#defineMPU6050_RA_ZA_OFFS_H0x0A//[15:

0]ZA_OFFS

20#defineMPU6050_RA_ZA_OFFS_L_TC0x0B

21#defineMPU6050_RA_XG_OFFS_USRH0x13//[15:

0]XG_OFFS_USR

22#defineMPU6050_RA_XG_OFFS_USRL0x14

23#defineMPU6050_RA_YG_OFFS_USRH0x15//[15:

0]YG_OFFS_USR

24#defineMPU6050_RA_YG_OFFS_USRL0x16

25#defineMPU6050_RA_ZG_OFFS_USRH0x17//[15:

0]ZG_OFFS_USR

26#defineMPU6050_RA_ZG_OFFS_USRL0x18

27#defineMPU6050_RA_SMPLRT_DIV0x19

28#defineMPU6050_RA_CONFIG0x1A

29#defineMPU6050_RA_GYRO_CONFIG0x1B

30#defineMPU6050_RA_ACCEL_CONFIG0x1C

31#defineMPU6050_RA_FF_THR0x1D

32#defineMPU6050_RA_FF_DUR0x1E

33#defineMPU6050_RA_MOT_THR0x1F

34#defineMPU6050_RA_MOT_DUR0x20

35#defineMPU6050_RA_ZRMOT_THR0x21

36#defineMPU6050_RA_ZRMOT_DUR0x22

37#defineMPU6050_RA_FIFO_EN0x23

38#defineMPU6050_RA_I2C_MST_CTRL0x24

39#defineMPU6050_RA_I2C_SLV0_ADDR0x25

40#defineMPU6050_RA_I2C_SLV0_REG0x26

41#defineMPU6050_RA_I2C_SLV0_CTRL0x27

42#defineMPU6050_RA_I2C_SLV1_ADDR0x28

43#defineMPU6050_RA_I2C_SLV1_REG0x29

44#defineMPU6050_RA_I2C_SLV1_CTRL0x2A

45#defineMPU6050_RA_I2C_SLV2_ADDR0x2B

46#defineMPU6050_RA_I2C_SLV2_REG0x2C

47#defineMPU6050_RA_I2C_SLV2_CTRL0x2D

48#defineMPU6050_RA_I2C_SLV3_ADDR0x2E

49#defineMPU6050_RA_I2C_SLV3_REG0x2F

50#defineMPU6050_RA_I2C_SLV3_CTRL0x30

51#defineMPU6050_RA_I2C_SLV4_ADDR0x31

52#defineMPU6050_RA_I2C_SLV4_REG0x32

53#defineMPU6050_RA_I2C_SLV4_DO0x33

54#defineMPU6050_RA_I2C_SLV4_CTRL0x34

55#defineMPU6050_RA_I2C_SLV4_DI0x35

56#defineMPU6050_RA_I2C_MST_STATUS0x36

57#defineMPU6050_RA_INT_PIN_CFG0x37

58#defineMPU6050_RA_INT_ENABLE0x38

59#defineMPU6050_RA_DMP_INT_STATUS0x39

60#defineMPU6050_RA_INT_STATUS0x3A

61#defineMPU6050_RA_ACCEL_XOUT_H0x3B

62#defineMPU6050_RA_ACCEL_XOUT_L0x3C

63#defineMPU6050_RA_ACCEL_YOUT_H0x3D

64#defineMPU6050_RA_ACCEL_YOUT_L0x3E

65#defineMPU6050_RA_ACCEL_ZOUT_H0x3F

66#defineMPU6050_RA_ACCEL_ZOUT_L0x40

67#defineMPU6050_RA_TEMP_OUT_H0x41

68#defineMPU6050_RA_TEMP_OUT_L0x42

69#defineMPU6050_RA_GYRO_XOUT_H0x43

70#defineMPU6050_RA_GYRO_XOUT_L0x44

71#defineMPU6050_RA_GYRO_YOUT_H0x45

72#defineMPU6050_RA_GYRO_YOUT_L0x46

73#defineMPU6050_RA_GYRO_ZOUT_H0x47

74#defineMPU6050_RA_GYRO_ZOUT_L0x48

75#defineMPU6050_RA_EXT_SENS_DATA_000x49

76#defineMPU6050_RA_EXT_SENS_DATA_010x4A

77#defineMPU6050_RA_EXT_SENS_DATA_020x4B

78#defineMPU6050_RA_EXT_SENS_DATA_030x4C

79#defineMPU6050_RA_EXT_SENS_DATA_040x4D

80#defineMPU6050_RA_EXT_SENS_DATA_050x4E

81#defineMPU6050_RA_EXT_SENS_DATA_060x4F

82#defineMPU6050_RA_EXT_SENS_DATA_070x50

83#defineMPU6050_RA_EXT_SENS_DATA_080x51

84#defineMPU6050_RA_EXT_SENS_DATA_090x52

85#defineMPU6050_RA_EXT_SENS_DATA_100x53

86#defineMPU6050_RA_EXT_SENS_DATA_110x54

87#defineMPU6050_RA_EXT_SENS_DATA_120x55

88#defineMPU6050_RA_EXT_SENS_DATA_130x56

89#defineMPU6050_RA_EXT_SENS_DATA_140x57

90#defineMPU6050_RA_EXT_SENS_DATA_150x58

91#defineMPU6050_RA_EXT_SENS_DATA_160x59

92#defineMPU6050_RA_EXT_SENS_DATA_170x5A

93#defineMPU6050_RA_EXT_SENS_DATA_180x5B

94#defineMPU6050_RA_EXT_SENS_DATA_190x5C

95#defineMPU6050_RA_EXT_SENS_DATA_200x5D

96#defineMPU6050_RA_EXT_SENS_DATA_210x5E

97#defineMPU6050_RA_EXT_SENS_DATA_220x5F

98#defineMPU6050_RA_EXT_SENS_DATA_230x60

99#defineMPU6050_RA_MOT_DETECT_STATUS0x61

100#defineMPU6050_RA_I2C_SLV0_DO0x63

101#defineMPU6050_RA_I2C_SLV1_DO0x64

102#defineMPU6050_RA_I2C_SLV2_DO0x65

103#defineMPU6050_RA_I2C_SLV3_DO0x66

104#defineMPU6050_RA_I2C_MST_DELAY_CTRL0x67

105#defineMPU6050_RA_SIGNAL_PATH_RESET0x68

106#defineMPU6050_RA_MOT_DETECT_CTRL0x69

107#defineMPU6050_RA_USER_CTRL0x6A

108#defineMPU6050_RA_PWR_MGMT_10x6B

109#defineMPU6050_RA_PWR_MGMT_20x6C

110#defineMPU6050_RA_BANK_SEL0x6D

111#defineMPU6050_RA_MEM_START_ADDR0x6E

112#defineMPU6050_RA_MEM_R_W0x6F

113#defineMPU6050_RA_DMP_CFG_10x70

114#defineMPU6050_RA_DMP_CFG_20x71

115#defineMPU6050_RA_FIFO_COUNTH0x72

116#defineMPU6050_RA_FIFO_COUNTL0x73

117#defineMPU6050_RA_FIFO_R_W0x74

118#defineMPU6050_RA_WHO_AM_I0x75

119

120#defineMPU6050_TC_PWR_MODE_BIT7

121#defineMPU6050_TC_OFFSET_BIT6

122#defineMPU6050_TC_OFFSET_LENGTH6

123#defineMPU6050_TC_OTP_BNK_VLD_BIT0

124

125#defineMPU6050_VDDIO_LEVEL_VLOGIC0

126#defineMPU6050_VDDIO_LEVEL_VDD1

127

128#defineMPU6050_CFG_EXT_SYNC_SET_BIT5

129#defineMPU6050_CFG_EXT_SYNC_SET_LENGTH3

130#defineMPU6050_CFG_DLPF_CFG_BIT2

131#defineMPU6050_CFG_DLPF_CFG_LENGTH3

132

133#defineMPU6050_EXT_SYNC_DISABLED0x0

134#defineMPU6050_EXT_SYNC_TEMP_OUT_L0x1

135#defineMPU6050_EXT_SYNC_GYRO_XOUT_L0x2

136#defineMPU6050_EXT_SYNC_GYRO_YOUT_L0x3

137#defineMPU6050_EXT_SYNC_GYRO_ZOUT_L0x4

138#defineMPU6050_EXT_SYNC_ACCEL_XOUT_L0x5

139#defineMPU6050_EXT_SYNC_ACCEL_YOUT_L0x6

140#defineMPU6050_EXT_SYNC_ACCEL_ZOUT_L0x7

141

142#defineMPU6050_DLPF_BW_2560x00

143#defineMPU6050_DLPF_BW_1880x01

144#defineMPU6050_DLPF_BW_980x02

145#defineMPU6050_DLPF_BW_420x03

146#defineMPU6050_DLPF_BW_200x04

147#defineMPU6050_DLPF_BW_100x05

148#defineMPU6050_DLPF_BW_50x06

149

150#defineMPU6050_GCONFIG_FS_SEL_BIT4

151#defineMPU6050_GCONFIG_FS_SEL_LENGTH2

152

153#defineMPU6050_GYRO_FS_2500x00

154#defineMPU6050_GYRO_FS_5000x01

155#defineMPU6050_GYRO_FS_10000x02

156#defineMPU6050_GYRO_FS_20000x03

157

158#defineMPU6050_ACONFIG_XA_ST_BIT7

159#defineMPU6050_ACONFIG_YA_ST_BIT6

160#defineMPU6050_ACONFIG_ZA_ST_BIT5

161#defineMPU6050_ACONFIG_AFS_SEL_BIT4

162#defineMPU6050_ACONFIG_AFS_SEL_LENGTH2

163#defineMPU6050_ACONFIG_ACCEL_HPF_BIT2

164#defineMPU6050_ACONFIG_ACCEL_HPF_LENGTH3

165

166#defineMPU6050_ACCEL_FS_20x00

167#defineMPU6050_ACCEL_FS_40x01

168#defineMPU6050_ACCEL_FS_80x02

169#defineMPU6050_ACCEL_FS_160x03

170

171#defineMPU6050_DHPF_RESET0x00

172#defineMPU6050_DHPF_50x01

173#defineMPU6050_DHPF_2P50x02

174#defineMPU6050_DHPF_1P250x03

175#defineMPU6050_DHPF_0P630x04

176#defineMPU6050_DHPF_HOLD0x07

177

178#defineMPU6050_TEMP_FIFO_EN_BIT7

179#defineMPU6050_XG_FIFO_EN_BIT6

180#defineMPU6050_YG_FIFO_EN_BIT5

181#defineMPU6050_ZG_FIFO_EN_BIT4

182#defineMPU6050_ACCEL_FIFO_EN_BIT3

183#defineMPU6050_SLV2_FIFO_EN_BIT2

184#defineMPU6050_SLV1_FIFO_EN_BIT1

185#defineMPU6050_SLV0_FIFO_EN_BIT0

186

187#defineMPU6050_MULT_MST_EN_BIT7

188#defineMPU6050_WAIT_FOR_ES_BIT6

189#defineMPU6050_SLV_3_FIFO_EN_BIT5

190#defineMPU6050_I2C_MST_P_NSR_BIT4

191#defineMPU6050_I2C_MST_CLK_BIT3

192#defineMPU6050_I2C_MST_CLK_LENGTH4

193

194#defineMPU6050_CLOCK_DIV_3480x0

195#defineMPU6050_CLOCK_DIV_3330x1

196#defineMPU6050_CLOCK_DIV_3200x2

197#defineMPU6050_CLOCK_DIV_3080x3

198#defineMPU6050_CLOCK_DIV_2960x4

199#defineMPU6050_CLOCK_DIV_2860x5

200#defineMPU6050_CLOCK_DIV_2760x6

201#defineMPU6050_CLOCK_DIV_2670x7

202#defineMPU6050_CLOCK_DIV_2580x8

203#defineMPU6050_CLOCK_DIV_5000x9

204#defineMPU6050_CLOCK_DIV_4710xA

205#defineMPU6050_CLOCK_DIV_4440xB

206#defineMPU6050_CLOCK_DIV_4210xC

207#defineMPU6050_CLOCK_DIV_4000xD

208#defineMPU6050_CLOCK_DIV_3810xE

209#defineMPU6050_CLOCK_DIV_3640xF

210

211#defineMPU6050_I2C_SLV_RW_BIT7

212#defineMPU6050_I2C_SLV_ADDR_BIT6

213#defineMPU6050_I2C_SLV_ADDR_LENGTH7

214#defineMPU6050_I2C_SLV_EN_BIT7

215#defineMPU6050_I2C_SLV_BYTE_SW_BIT6

216#defineMPU6050_I2C_SLV_REG_DIS_BIT5

217#defineMPU6050_I2C_SLV_GRP_BIT4

218#defineMPU6050_I2C_SLV_LEN_BIT3

219#defineMPU6050_I2C_SLV_LEN_LENGTH4

220

221#defineMPU6050_I2C_SLV4_RW_BIT7

222#defineMPU6050_I2C_SLV4_ADDR_BIT6

223#defineMPU6050_I2C_SLV4_ADDR_LENGTH7

224#defineMPU6050_I2C_SLV4_EN_BIT7

225#defineMPU6050_I2C_SLV4_INT_EN_BIT6

226#defineMPU6050_I2C_SLV4_REG_DIS_BIT5

227#defineMPU6050_I2C_SLV4_MST_DLY_BIT4

228#defineMPU6050_I2C_SLV4_MST_DLY_LENGTH5

229

230#defineMPU6050_MST_PASS_THROUGH_BIT7

231#defineMPU6050_MST_I2C_SLV4_DONE_BIT6

232#defineMPU6050_MST_I2C_LOST_ARB_BIT5

233#defineMPU6050_MST_I2C_SLV4_NACK_BIT4

234#defineMPU6050_MST_I2C_SLV3_NACK_BIT3

235#defineMPU6050_MST_I2C_SLV2_NACK_BIT2

236#defineMPU6050_MST_I2C_SLV1_NACK_BIT1

237#defineMPU6050_MST_I2C_SLV0_NACK_BIT0

238

239#defineMPU6050_INTCFG_INT_LEVEL_BIT7

240#defineMPU6050_INTCFG_INT_OPEN_BIT6

241#defineMPU6050_INTCFG_LATCH_INT_EN_BIT5

242#defineMPU6050_INTCFG_INT_RD_CLEAR_BIT4

243#defineMPU6050_INTCFG_FSYNC_INT_LEVEL_BIT3

244#defineMPU6050_INTCFG_FSYNC_INT_EN_BIT2

245#defineMPU6050_INTCFG_I2C_BYPASS_EN_BIT1

246#defineMPU6050_INTCFG_CLKOUT_EN_BIT0

247

248#defineMPU6050_INTMODE_