飞思卡尔处理器PWM模块精讲Word文件下载.docx

《飞思卡尔处理器PWM模块精讲Word文件下载.docx》由会员分享,可在线阅读,更多相关《飞思卡尔处理器PWM模块精讲Word文件下载.docx(18页珍藏版)》请在冰豆网上搜索。

PWME7=0---通道7不能对外输出波形

注意:

在通道使能后所输出的第一个波形可能是不规则的。

当输出通道工作在串联模式时(PWMCTL寄存器中的CONxx置1),那么)使能相应的16位PWM输出通道是由PWMEx的高位控制的,例如:

设置PWMCTL_CON01=1,通道0、1级联,形成一个16位PWM通道,由通道1的使能位控制PWM的输出。

2、PWM时钟选择寄存器PWMCLK

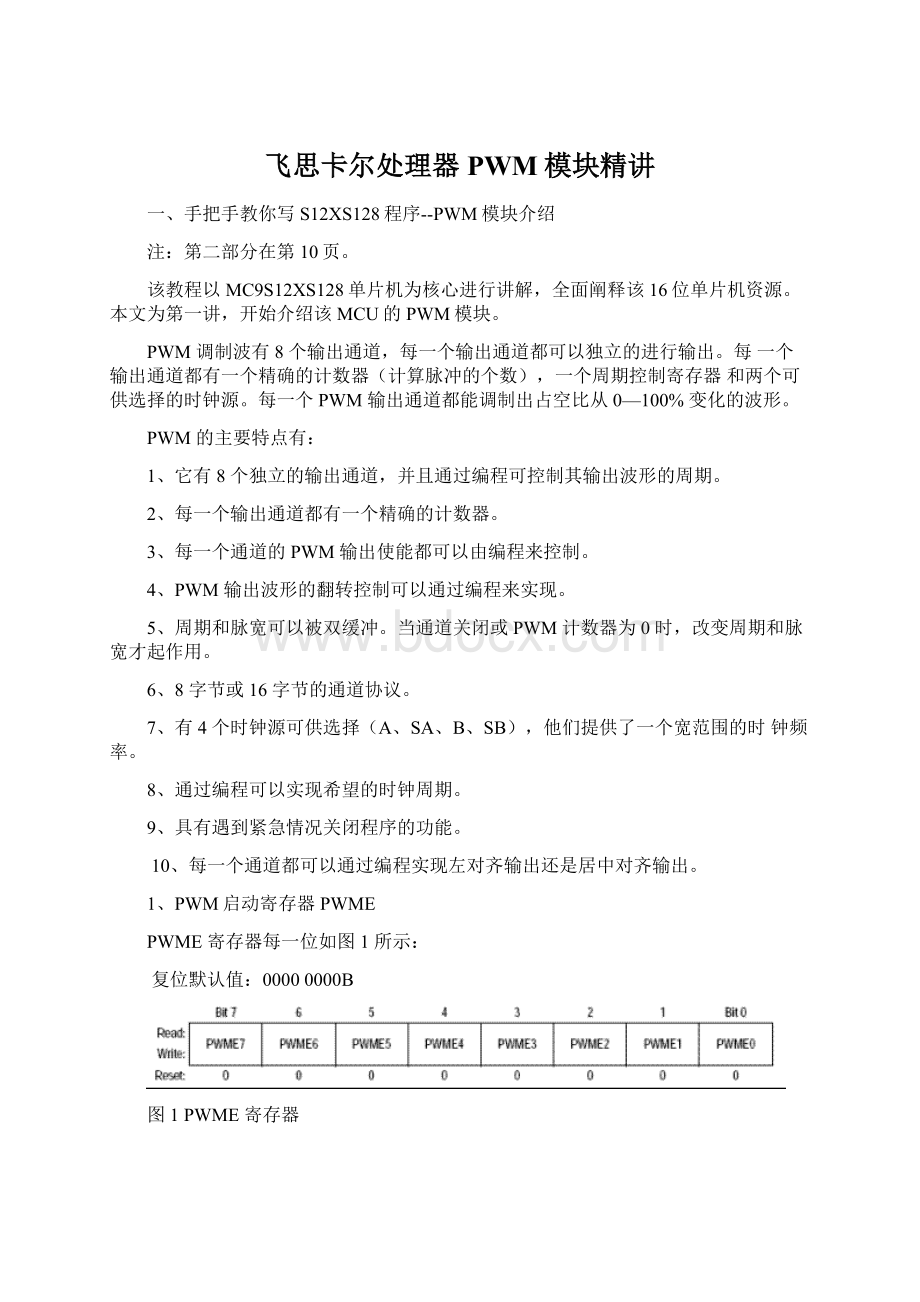

PWMCLK寄存器每一位如图3所示:

图2PWMCLK寄存器

S12的PWM共有四个时钟源,每一个PWM输出通道都有两个时钟可供选择(ClockA、ClockSA或ClockB、ClockSB))。

其中0、1、4、5通道可选用ClockA和ClockSA,2、3、6、7通道可选用ClockB、ClockSB通道。

该寄存器用来实现几个通道时钟源的选择。

PCLK0=1---通道0(PTP0)的时钟源设为ClockSA

PCLK2=0---通道2(PTP2)的时钟源设为ClockB

1、PWM预分频寄存器PWMPRCLK

PWMPRCLK寄存器每一位如图3所示:

图3PWMPRCLK寄存器

PWMPRCLK寄存器包括ClockA预分频和ClockB预分频的控制位。

ClockA、ClockB的值为总线时钟的1/2n(0≤n≤7),具体设置参照图4和图5

图4ClockA预分频设置

图5ClockB预分频设置

PCKB0~PCKB2是对ClockB进行预分频。

PCKA0~PCKA2是对ClockA进行预分频。

2、PWM分频寄存器PWMSCLA、PWMSCLB

PWMSCLA寄存器每一位如图6所示:

图6PWMSCLA寄存器

ClockSA是通过对PWMSCLA寄存器的设置来对ClockA进行分频而产生的。

其计算公式为:

ClockSA=ClockA/(2*PWMSCLA)

PWMSCLB寄存器与PWMSCLA寄存器相似,ClockSB就是通过对PWMSCLB寄存器的设置来对ClockB进行分频而产生的。

ClockSB=ClockB/(2*PWMSCLB)

1、PWM极性选择寄存器PWMPOL

PWMPOL寄存器每一位如图7所示:

该寄存器是0~7通道PWM输出起始极性控制位,用来设置PWM输出的起始电平。

用法:

PWMPOL_PPOL0=1---通道0在周期开始时输出为高电平,当计数器等于占空比寄存器的值时,输出为低电平。

对外输出波形先是高电平然后再变为低电平。

2、PWM波形对齐寄存器PWMCAE

PWMCAE寄存器每一位如图8所示:

图8PWMCAE寄存器

PWMCAE寄存器包含8个控制位来对每个PWM通道设置左对齐输出或中心对齐输出。

用法:

PWMCAE_CAE0=1---通道0中心对齐输出

PWMCAE_CAE7=0---通道7左对齐输出

只有输出通道被关闭后才能对其进行设置,即通道被激活后不能对其进行设置。

1、PWM控制寄存器PWMCTL

PWMCTL寄存器每一位如图9所示:

图9PWMCTL寄存器

该控制寄存器设定通道的级联和两种工作模式:

等待模式和冻结模式。

这两种模式如图10和图11所示。

图10等待模式图11冻结模式

只有当相应的通道关闭后,才能改变这些控制字。

PWMCTL_CON67=1---通道6、7级联成一个16位的PWM通道。

此时只有7通道的控制字起作用,原通道7的使能位、PWM输出极性选择位、时钟选择控制位以及对齐方式选择位用来设置级联后的PWM输出特性

PWMCTL_CON67=0---通道6,7通道不级联

CON45、CON23、CON01的用法同CON67相似。

设置此控制字的意义在于扩大了PWM对外输出脉冲的频率范围。

PSWAI=1---MCU一旦处于等待状态,就会停止时钟的输入。

这样就不会因时钟在空操作而费电;

当它置为0,则MCU就是处于等待状态,也允许时钟的输入。

PFRZ=1---MCU一旦处于冻结状态,就会停止计数器工作。

S12微控制器PWM模块是由独立运行的8位脉冲计数器PWMCNT、两个比较寄存器PWMPER和PWMDTY组成。

1、左对齐方式

在该方式下,脉冲计数器为循环递增计数,计数初值为0。

当PWM使能后,计数器PWMCNT从0开始对时钟信号递增计数,开始一个输出周期。

当计数值与占空比常数寄存器PWMDTY相等时,比较器1输出有效,将触发器置位,而PWMCNT继续计数;

当计数值与周期常数寄存器PWMPER相等时,比较器2输出有效,将触发器复位,同时PWMCNT也复位,结束一个输出周期。

原理参照图14:

图14PWM左对齐方式

2、中心对齐方式

在该方式下,脉冲计数器为双向计数,计数初值为0。

当PWM使能后,计数器PWMCNT从0开始对时钟信号递增计数,开始输出一个周期。

当计数器与占空比常数寄存器PWMDTY相等时,比较器1输出有效,触发器翻转,而PWMCNT继续计数,当计数值与周期常数PWMPER相等时,比较器2输出有效,此时改变PWMCNT的计数方向,使其递解计数;

当PWMCNT再次与PWMDTY相等时,比较器1再一次输出有效,使触发器再次翻转,而PWMCNT继续递减计数,等待PWMCNT减回至0,完成一个输出周期。

原理参照图15:

图15

中心对齐方式

3、周期计算方法

左对齐方式:

输出周期=通道周期×

PWMPERx

中心对齐方式:

PWMPERx×

2

4、脉宽计算方法

占空比=[(PWMPERx-PWMDTYx)/PWMPERx]×

100%

占空比=[PWMDTYx/PWMPERx]×

1、PWM通道计数寄存器PWMCNTx

PWMCNTx寄存器共有8个,每一个通道都有一个8位PWM加/减双向计数器,通道级联后可变成16位PWM加/减双向计数器。

下面以PWMCNT0为例对PWMCNTx寄存器进行介绍。

PWMCNT0寄存器如图12所示:

图12PWMCNT0寄存器

计数器以所选时钟源的频率运行。

计数器在任何时候都可以被读,而不影响计数,也不影响对PWM通道的操作。

任何值写入PWMCNT0寄存器都会导致计数器复位置0,且其计数方向会被设置为向上计数,并且会立刻从缓冲器载入任务和周期值,并会根据翻转极性的设置来改变输出。

当计数器达到计数值后,会自动清零。

只有当通道使能后,计数器才开始计数。

2、PWM通道周期寄存器PWMPERx

PWMPERx寄存器共有8个,每一个通道都有一个这样的周期寄存器。

这个寄存器的值就决定了相关PWM通道的周期。

每一个通道的周期寄存器都是双缓冲的,因此如果当通道使能后,改变他们的值,将不会发生任何作用,除非当下列情况之一发生:

*有效的周期结束。

*对计数器进行写操作(计数器复位)

*通道不可用(PWMEx=0)

这样就会使PWM输出波形要么是新波形要么是旧波形,并不会在两者之间进行交替变换。

如果通道不可用,那么对周期寄存器进行写操作,将会直接

图表1

导致周期寄存器同缓冲器一起闭锁。

图13所示的是PWMPER0寄存器:

图13PWMPER0寄存器

3、PWM通道占空比寄存器PWMDTYx

PWMDTYx寄存器也有8个,每一个通道都有一个这样的占空比常数寄存器。

这个寄存器的值就决定了相关PWM通道输出波形的占空比。

每一个通道的占空比寄存器都是双缓冲的,因此如果当通道被激活后,改变他们的值将不会发生任何作用,除非当下列情况之一发生:

如果通道没有被激活,那么对占空比常数寄存器进行写操作,将会直接导致周期寄存器同缓冲器一起闭锁。

当计数值与占空比常数PWMDTY相等时,则比较输出器有效,这时就会将触发器置位,然后PWMCNT继续计数,当计数值与周期常数PWMPER相等时,比较器输出有效,将触发器复位,同时也使PWMCNT复位,结束一个输出周期。

PWM初始化步骤总结

1、禁止PWMPWME=0

2、选择时钟PWMPRCLK,PWMSCLA,PWMSCLB,PWMCLK

3、选择极性PWMPOL

4、选择对齐方式PWMCAE

5、选择占空比和周期PWMDTYx,PWMPERx

6、使能PWMPWME=1

【例程1】

//------------------------------------------------------------------------------------------------------------------//

//功能说明:

MC9S12XS128--PWM例程

//使用说明:

实现通道3(PTP3)输出频率为1KHz,占空比为50%的方波,用示波器观察

//程序设计:

电子设计吧【】

//设计时间:

2010.01.21

//----------------------------------------------------------------------------------------------------------------//

#include<

hidef.h>

/*commondefinesandmacros*/

#include"

derivative.h"

/*derivative-specificdefinitions*/

//--------------初始化函数----------------//

//-----时钟初始化程序--------//

voidPLL_Init(void)//PLLCLK=2*OSCCLK*(SYNR+1)/(REFDV+1)

{//锁相环时钟=2*16*(2+1)/(1+1)=48MHz

REFDV=1;

//总线时钟=48/2=24MHz

SYNR=2;

while(!

(CRGFLG&

0x08));

CLKSEL=0x80;

//选定锁相环时钟

}

//-----PWM初始化程序------//

voidPWM_Init(void)

{

PWME_PWME3=0x00;

//DisablePWM禁止

PWMPRCLK=0x33;

//00110011A=B=24M/8=3M时钟预分频寄存器设置

PWMSCLA=150;

//SA=A/2/150=10k时钟设置

PWMSCLB=15;

//SB=B/2/15=100k时钟设置

PWMCLK_PCLK3=1;

//PWM3-----SB时钟源的选择

PWMPOL_PPOL3=1;

//Duty=HighTime极性设置

PWMCAE_CAE3=0;

//Left-aligned对齐方式设置

PWMCTL=0x00;

//noconcatenation控制寄存器设置

PWMPER3=100;

//Frequency=SB/100=1K周期寄存器设置

PWMDTY3=50;

//Dutycycle=50%占空比寄存器设置

PWME_PWME3=1;

//EnablePWM使能

//-----------------主函数--------------------//

voidmain(void)

/*putyourowncodehere*/

PLL_Init();

PWM_Init();

EnableInterrupts;

for(;

;

){

_FEED_COP();

/*feedsthedog*/

}/*loopforever*/

/*pleasemakesurethatyouneverleavemain*/

二、手把手教你飞思卡尔MC9S12HZ系列MCUPWM模块

作者:

盛多铮

单位:

安徽师范大学电子信息工程系

寒假的时候开始接触9S12XS128这款片子,并在寒假掌握了codewarrior开发环境的基本使用和SCI模块串口收发方面的编程。

新学期一开始由于一直在忙着另外一个采集方面的课题,所以飞思卡尔的学习进展不是很快,今天看了PWM模块和PIT模块的相关资料,并自己写了一些小小的程序,在示波器上看到了理想的波形,所以趁着今晚有空,将这方面的学习感悟总结一下,在自我总结的同时,也希望给你的学习带来一些帮助,所谓赠人玫瑰,手留余香呵呵。

。

废话不多说,进入正题

PWM模块

9S12XS128共有8个独立的可编程的PWM通道,可配置成8个8位或4个16位的PWM通道,共有4个时钟源,可软件设置对齐方式和极性,这里所谓的极性就是说PWM一开始输出的是高电平还是低电平。

下面就我们常用的寄存器作简单介绍(因为别的寄存器我也没用到呵呵。

)

1、PWMEnableRegister(PWME)

PWME[7:

0]分别控制着对应的8个通道的使能,例如:

PWME_PWME0=0:

禁止通道0的PWM输出

PWME_PWME7=1:

使能通道7的PWM输出

2、PWMPolarityRegister(PWMPOL)

ZA

PWMPOL寄存器是用来控制PWM一开始输出时的信号高低情况,假如PPOLX设为1,则与之相应的PWM通道在开始的时候输出为高电平,然后等到计数器的值与你设置的那个PWM信号的值(PWMDTYx)相等的时候就输出低电平。

PPOL的值为0的时候正好与这相反。

3、PWMClockSelectRegister(PWM时钟选择)

PWMCLK寄存器是用来设置每个通道的参考时钟源的,每个通道都有2个时钟源,具体的为CLOCKA,CLOCKSA(0,1,4,5);

CLOCKB,CLOCKSB(2,3,6,7),例如:

PWMCLK_PCLK0=0;

则通道0选择CLOCKA作为时钟源

PWMCLK_PCLK6=1;

则通道6选择CLOCKSB作为参考时钟源

4、PWMPrescaleClockSelectRegisrer(PWMPRCLK)

PWMPRCLK的第3位和第7位没有定义,低三位用来设置CLOCKA的分频,4-6位则设置CLOCKB的分频,以CLOCKA为例,具体值的计算如下表:

假如说,外部晶振为12M,SYNR为1,REFDV的值为0,则总线时钟为24M,然后你将PWMPRCLK设为0x03,那么你这个CLOCKA的频率就为3M

5、PWMCenterAlignEnableRegister(PWMCAE)

PWMCAE寄存器用来设置每个通道的对齐方式,CAEx为0时,设置相应的通道为左对齐,CAEx为1时,设置相应的通道为中心对齐,例如:

PWMCAE_PCAE=0,则通道0设置为左对齐,那么左对齐和中心对齐有什么不同呢,别急,这个等讲到PWMDTYx和PWMPERx这两个寄存器后要好解释一点。

6、PWMControlRegister(PWMCTL)

PWMCTL寄存器可以控制相应通道之间的两两级联情况,以便将PWM口设置成16位的输出,这样有利于提高精度,比如你设置PWMCTL_CON01=1;

那么通道0和通道1就级联成一个16位的PWM输出通道,这个16位的PWM通道的输出端为通道1的输出端口,其配置情况也由通道1的相应寄存器去设置。

除此之外,PWMCTL寄存器还可以设置PWM的运行模式,具体的解释为:

当PSWAI=0的时候,则始终在等待模式下继续运行,当PFRZ=1的时候,则禁止PWM模块在Freeze模式下的运行

7、PWMScaleARerister(PWMSCLA)

PWMSCLA寄存器是用来将CLOCKA寄存器继续压缩分频,以产生CLOCKSA,具体的计算公式如下:

CLOCKSA=CLOCK/2*PWMSCLA

当PWMSCLA为0的时候实际上是满标度值,也就是将COLCKA512分频

寄存器各位如下所示

8、PWMScaleBRegister(PWMSCLB)

该寄存器的使用情况和PWMSCLA一样,这里不累述,具体可参考上面一段

9、PWMChannelPeriodRegisters(PWMPERx)

每个通道都有一个专用的用来设置周期情况的寄存器(PWMPERx),这个寄存器的值就决定了PWM通道输出信号周期的长短,如果我们已经知道的参考时钟源的值,那么就可以计算出PWM输出信号的周期了,计算方法如下:

PWMxPeriod=ChannelClockPeriod*PWMPERx(左对齐情况下)

PWMxPeriod=ChannelClockPeriod*PWMPERx*2(左对齐情况下)

10、PWMChannelDutyRegisters(PWMDTYx)

每个通道都有一个专用的用来设置占空比的寄存器PWMDTYx,PWMDTYx和PWMPERx的值共同决定了占空比的值,就是说当每个通道的count的值计数到与PWMDTYx的值相等时,相应的输出信号就发生一次翻转。

如果你设置PWMPOL寄存器的某位PPOLx的值为1,也就是开始的时候输出为高电平,然后当计数器数到与PWMDTYx的值后就翻转为低电平,那么PWMDTY寄存器的值就包含了高电平的时间,再结合占空比说明一下吧

PPOLx=1:

占空比=(PWMDTYx/PWMPERx)*100%

PPOLx=0:

占空比=(PWMPERx-PWMDTYx)/PWMPERx*100%

这样讲应该就懂了吧…….

好了,要是我自己在做项目的用到这一块的时候当然不会这么繁琐的看一遍了,直接看看着手册,然后把每个寄存器配置的值往记事本里一写,所有的寄存器都配置完后把这些个值往模块初始化函数里一贴,搞定。

所以这里花了这么多的篇幅,充其量也只是希望对正出于飞思门槛上的一些朋友一点帮助罢了。

下面附上一段PWM模块的子函数:

#include<

mc9s12xs128.h>

voidPWMInit()

{

PWME_PWME0=0;

PWMCLK_PCLK0=1;

//选择COLCKSA

PWMPOL_PPOL0=1;

//开始的时候输出高电平

PWMPRCLK=0x03;

//预分频,CLOCK=BUSCLOCK/8;

PWMCAE_CAE0=0;

//左对齐

//不级联,等待模式和冻结模式下允许时钟继续运行

PWMSCLA=245;

PWMDTY0=200;

//根据你的需要在适当的位置改变PWMDTYx的值即可。

PWMPER0=100;

//此处可设计占空比

PWME_PWME0=1;

}

这是产生PWM的一个程序,使用时应加上设置BUSCLOCK的程序(这部分在时钟模块中讲到,此处就不多说了)。

不过直接使用上述函数,不添加BUSCLOCK的程序也是可以的,这时候BUSCLOCK为系统默