数字逻辑电路 答案作业5Word下载.docx

《数字逻辑电路 答案作业5Word下载.docx》由会员分享,可在线阅读,更多相关《数字逻辑电路 答案作业5Word下载.docx(18页珍藏版)》请在冰豆网上搜索。

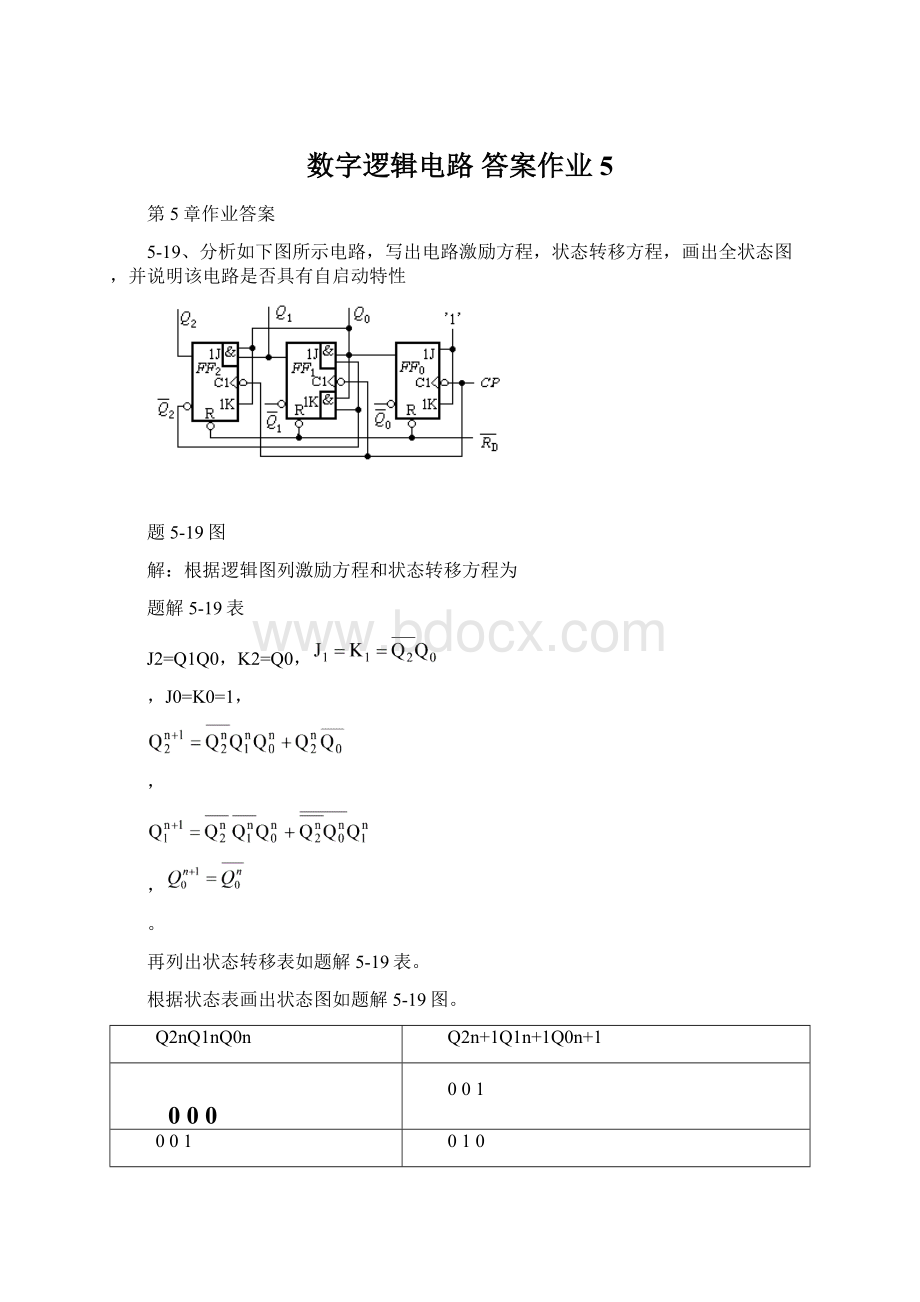

101

110

111

题解5-19图

该电路功能为同步六进制计数器,计数模M=6,从状态图可以看出该电路具有自启动功能。

5-22、图P5-22所示电路为用双向移位寄存器CT74LS194构成的自启动脉冲分配器,试列出QD~QA的状态转移表,并画出其波形图。

图P5-22

序号

S(t)

QAQBQCQD

N(t)

0000

0001

1

0011

2

0111

3

1111

4

1110

5

1100

6

1000

7

8

该电路S1S0=10,是左移工作模式,初始启动信号置QD~QA均为0,则DSL=1,

题解5-22表

状态转移表列于题解5-22表。

波形图如题解5-22图所示。

从解5-19表和图解P5-19可以看到,该电路称为四级扭环形计数器。

题解5-22图

5-26、分析下图所示电路为几进制计数器,并画出初始状态Q2Q1Q0=000的全状态图和波形图。

题5-26图

J2=Q1,K2=1,

,K1=1,

J0=K0=1

CP2=CP1=Q0,CP0=CP

题解5-26表

CP2CP1CP1

↓

↓↓↓

列出状态转移表如题解5-26表。

状态转移图和工作波形如题解5-26图所示。

由题解5-26表和题解5-26图可知,该电路为一个异步六进制计数器,并具有自启动功能。

题解5-26图

5-28、分析题5-28图(a)、(b)所示由中规模同步计数器CT74LS161构成的计数分频器的模值,并画出全状态图。

题5-28图

(a)CT74LS161的复位功能是异步的,则电路采用的是异步复位法,复位状态为1001,该状态不是计数循环中的一个状态,因而计数循环的状态为0000~1000,共9个状态,则M=9,全状态图为题解5-28图(a);

(b)CT74LS161的置数功能是同步的,电路采用的是同步置数法,置数状态为1001,该状态应是计数循环中的一个状态,所置数值为0000,因而计数循环的状态为0000~1001,共10个状态,则M=10,全状态图为题解5-28图(b)。

题解5-28图

5-29、分析题5-29图(a)、(b)所示由中规模同步计数器CT74LS163构成的计数分频器的模值,并画出全状态图。

题5-29图

(a)CT74LS163的复位功能是同步的,电路采用的是同步复位法,复位状态为1001,该状态应是计数循环中的一个状态,因而计数循环的状态为0000~1001,共10个状态,则M=10,全状态图为图解题5-29图(a);

(b)CT74LS163的置数功能是同步的,电路采用的是同步置数法,置数状态为进位信号CO,即状态是1111时置数,它应是计数循环中的一个状态,所置数值为0101,因而计数循环的状态为0101~1111,共11个状态,则M=11,全状态图为题解5-29图(b)。

题解5-29图

5-32、分析题5-32图(a)、(b)所示由两片中规模异步计数器CT74LS290构成的计数分频器的模值。

题5-32图

(a)CT74LS290是异步二-五-十进制计数器,它的置数功能和复位功能也都是异步的,电路的QA接到CPB,组成8421BCD码十进制计数器,并采用的是异步置数法,产生置数的状态为0101,该状态不是计数循环中的一个状态,所置数值为1001,因而计数循环的状态为1001,0000~0100共6个状态,则M=6,全状态图为题解5-32图(a),偏离状态的转移如图所示。

(b)接法不同于(a),电路的QD接到CPA,组成5421BCD码十进制计数器,从高位到低位排列顺序为QAQDQCQB,计数循环状态顺序为0000→0001→0010→0011→0100→1000→1001→1010→1011→1100→0000。

采用的是异步复位法,产生复位的状态是1010,它不是计数循环中的一个状态,因而计数循环的状态为0000~0100,1000→1001,共7个状态,则M=7,全状态图为题解5-32图(b),偏离状态的转移如图所示。

题解5-32图

5-35、分析题5-35图所示由两片中规模同步计数器CT74LS160构成的计数分频器的模值,图中

(1)为低位计数器,

(2)为高位计数器。

题5-35图

电路由两个CT74LS160计数器异步级联组成,计数器

(1)是十进制计数器,M1=10,在状态1001时CO=1,反相后触发计数器

(2)计数,计数器

(2)用同步置数法构成,在状态为0101时产生置数信号,该状态应是计数循环状态,置入数值0000,则计数循环为0000~0101,M2=6。

M=M2×

M1=6×

10=60。

5-38、用同步4位二进制计数集成芯片CT74LS161采用进位反馈同步置数法构成模值M为14的计数器,并画出接线图和全状态图。

采用进位反馈同步置数法构成模值M为14的计数器,在十六个状态循环中截取14个状态形成主计数循环即可,其中必须包含状态1111,以便用该状态产生置数信号,所置数值应是0010,题解5-38图(a)和(b)是其逻辑图和全状态图。

题解5-38图

5-39、用同步4位二进制计数集成芯片CT74LS163采用同步复位法构成模值M为11的计数器,并画出接线图和全状态图。

采用同步复位法组成11进制计数器,计数循环包括状态0000和产生复位信号的状态1010,即计数循环状态为0000~1010,共11个状态。

接线图和全状态图如题解5-39图所示。

题解5-39图

5-41、用同步4位二进制加/减计数集成芯片CT74LS191采用异步置数法构成模值M为12的减法计数器,并画出接线图和全状态图。

CT74LS191用于减法计数,

选择端应接高电平,置数功能是异步的。

置数的状态不是计数循环状态,若以借位输出反馈置数,产生置数信号的状态则为0000,计数循环状态应为1100~0001,逻辑图和全状态图分别如题解5-41图(a)、(b)所示。

题解5-41图

5-42、用异步二-五-十进制计数集成芯片CT74LS290采用异步置数法构成模值M为7的加法计数器,并画出接线图和全状态图。

将QA接CPB构成十进制计数器,CT74LS290的置数功能是异步的,且高电平有效,置入固定数值1001。

置数的状态不是计数循环状态,产生置数信号的状态则应为0110,计数循环状态应为0000~0101,1001,共7个状态。

逻辑图和全状态图分别如题解5-42图(a)、(b)所示。

题解5-42图

5-45、用三片同步十进制计数集成芯片CT74LS160采用异步复位和级间异步联接法构成模值M为512的8421BCD计数器。

将两片CT74LS160用异步级联法接成1000进制计数器,利用进位输出CO作高位计数器的CP触发计数,由于CO为高电平,而CP为上升沿触发,为使CO的下降沿触发高位的CP计数,接入一个反相器。

接入反馈,使其状态为512时复位,计数循环为0~511,逻辑图如题解5-45图所示。

图中

(1)、

(2)、(3)分别为个位、十位、百位计数器。

题解5-45图

5-46、用三片同步4位二进制计数集成芯片CT74LS163采用同步复位和级间同步联接法构成模值M为2000的计数器。

CT74LS163是十六进制计数器,(2000)10=(7D0)16,计数器的计数范围应为

(0~7CF)16,用同步复位法,产生复位的状态应为计数循环的一个状态,因而用(7CF)16状态产生复位信号,逻辑图如题解5-46图所示,其中计数器

(1)用CO代替四个Q的与。

题解5-46图

5-47、设计一个同步时序电路,输入为串行二进制数码,当输入两个0或两个以上0以后再输入一个1时输出为1,其他情况输出均为0。

用JK触发器CT74LS76和四2输入与非门CT74LS00实现。

根据题意列原始状态图如题解5-47图(a)所示,得原始状态表如题解5-47表(a)所示;

依据状态分配原则,令A=00,B=01,C=11,D=10,得到状态表题解5-47表(b)。

再根据题解5-47表(b)列出状态转移表如题解5-47表(c)。

依据题解5-47表(c)作卡诺图,如题解5-47图(b)所示。

题解5-47图(a)

Yn/Z

Yn+1

X=0

X=1

A/0

B

A

B/0

C

C/0

D

D/1

00/0

01

00

01/0

11

11/0

10

10/1

题解5-47表(b)

题解5-47表(a)

题解5-47表(c)

XQ1nQ0n

(Q1Q0)n+1

J1K1J0K0

Z

01

0×

1×

11

1×

×

×

11×

0×

00

0×

10×

10

得到激励方程和输出方程如下:

最后画出的逻辑图如题解5-47图(c)所示。

题解5-47图(b)

题解5-47图(c)

5-52试用D触发器CC4013及逻辑门设计一个环形四进制计数器,计数循环为0001→0010→0100→1000→0001,要求具有自启动特性。

4级环形计数器的驱动方程应为D3=Q2,D2=Q1,D1=Q0,D0=Q3,全状态图为题解5-52图(a),是一个非自启动的电路。

解决非自启动问题的方法很多,常用方法是将0000状态导入0001状态,将驱动方程D0=Q3改为

,其余驱动方程不变,则全状态图为题解5-52图(b),非自启动得以解决。

逻辑图如题解5-52图(c)所示。

题解5-52图(c)

5-53、分析题5-53图所示电路,画出工作波形图、全状态图,并说明电路功能。

题5-53图

根据电路画波形图,如题解5-53图所示。

从波形图可以看出,该电路是在3级扭环计数器基础上组成的7分频计数器。

题解5-53图

5-57、用异步集成计数器CT74LS290设计一个输出方波的1/9分频器。

将CT74LS290接成5421BCD码计数器,在利用最高有效位通过异或门控制技术脉冲的反相,即可得到输出方波的1/9分频器。

如题解5-57图(a)所示,波形如题解5-57图(b)所示。

题解5-57图(a)

题解5-57图(b)

5-58、设计移存型序列信号发生器产生如下序列信号:

(1)1110010,1110010…

(2)1111001000,1111001000…。

循环码共有十位,先用四个触发器试设计,做题解5-58图(a),列出题解5-58表,再填K图,如题解5-58图(b)所示。

题解5-58图(a)

题解5-58表

(Q4Q3Q2Q1)n

(Q4Q3Q2Q1)n+1

D1

1001

0010

0100

题解5-58图(b)

根据K图写出第

一级激励方程:

逻辑图如题解5-58图(c)所示。

题解5-58图(c)

5-59、用同步集成计数器CT74LS160设计一个能同时产生下列两个序列信号的计数型序列信号发生器:

1111001000和0011010111。

CT74LS160是8421BCD码计数器,序列信号为十位,输出逻辑用K图求:

题解5-59图(a)

逻辑图如题解5-59(b)图所示。

题解5-59图(b)

5-60、用线性反馈移存器设计循环长度为M的序列信号发生器:

(2)M=24。

(本题选做)

根据设计规则,M=24需要5级寄存器,最长循环状态是31个,要跳过7个状态。

寻找起跳点,题解5-60(a)列出了a、b、c序列码,a序列是5级寄存器从11111开始的最长序列码将前7位码移至尾部所得的序列码,b序列是原序列,与a序列按位对齐,c序列是a、b序列按位异或所得序列。

起跳点即为c序列中10000对应的a序列中的5位码11100。

相应的状态图如题解5-60(b)所示。

考虑到00000状态的启动因素,反馈函数为

逻辑图如题解5-60图(c)所示。

题解5-60图(c)