50占空比三分频器的设计方法文档格式.docx

《50占空比三分频器的设计方法文档格式.docx》由会员分享,可在线阅读,更多相关《50占空比三分频器的设计方法文档格式.docx(9页珍藏版)》请在冰豆网上搜索。

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

useieee.std_logic_arith.all;

entityfen3is

port

(clkin

:

in

std_logic;

--时钟输入

qout1

bufferstd_logic;

qout2

qout3

clkout:

out

std_logic

--占空比为1/2的三分频输出

);

endfen3;

architecturebehaveoffen3is

begin

qout3<

=qout1norqout2;

process(clkin)

begin

ifclkin'

eventandclkin='

1'

then

--在上升沿触发

qout1<

=qout3;

endif;

endprocess;

0'

--在下降沿触发

qout2<

process(qout3)

variabletem:

std_logic;

ifqout3'

eventandqout3='

--二分频

tem:

=nottem;

endif;

clkout<

=tem;

endprocess;

endbehave;

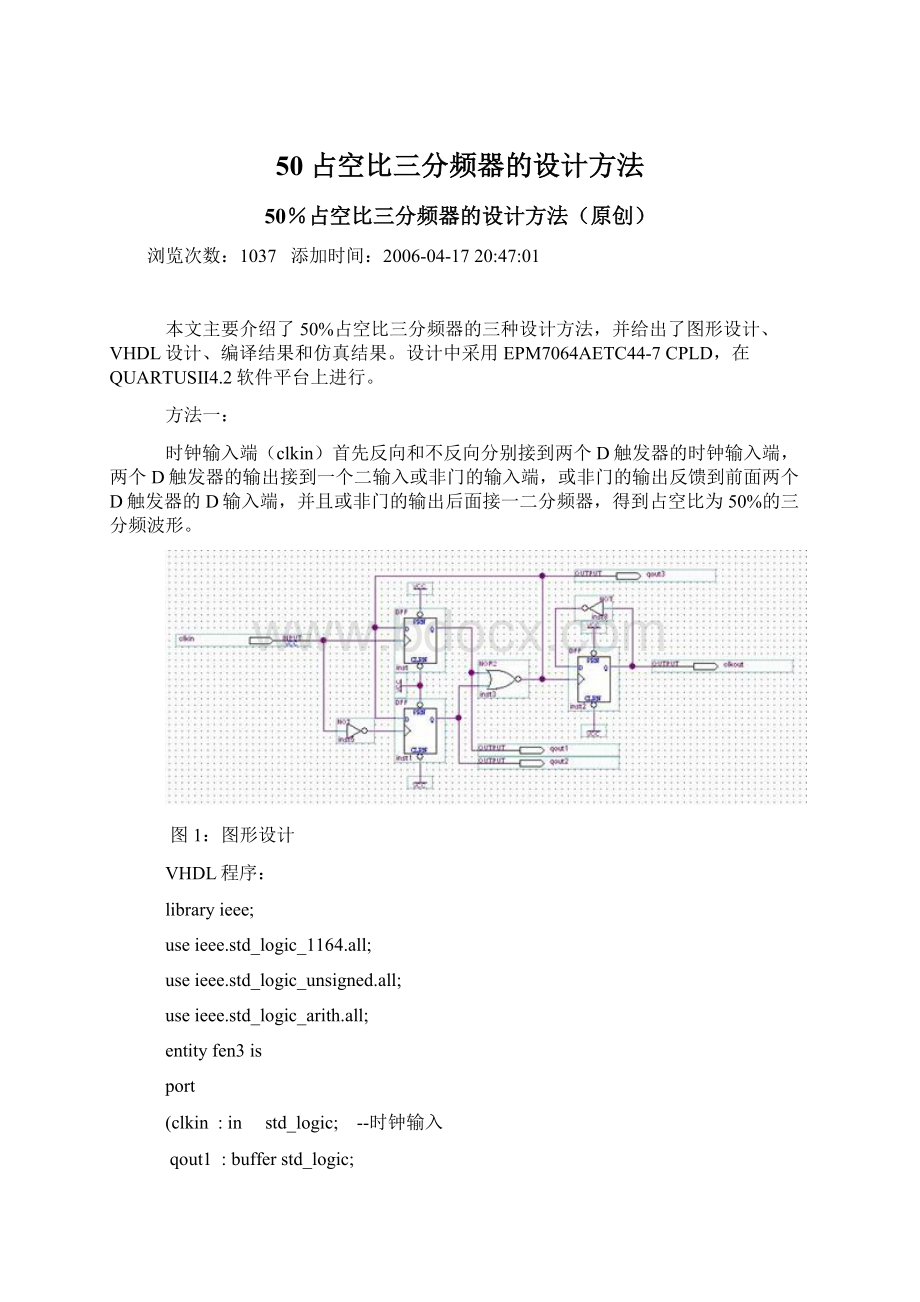

图2:

编译结果

图3:

仿真结果

方法二:

设计两个占空比为1/3的三分频器,分别在时钟输入端的上升沿和下降沿触发,然后两个分频器的输出接一个或门,得到占空比为50%的三分频波形。

图4:

entityfen3is

=qout1orqout2;

--占空比为1/3的三分频

variablecnt:

integerrange0to2;

--在上升沿触发

ifcnt=2then

cnt:

=0;

qout1<

='

;

else

cnt:

=cnt+1;

variablecnt:

begin

图5:

图6:

方法三:

设计一个占空比为50%的四分频器,四分频器的时钟输入端是由四分频器的输出端和时钟输入相异或后驱动的,四分频器的时钟输出端就是占空比为50%的三分频波形输出。

图7:

constantcounter_len:

integer:

=3;

--设置计数器的模

signalclk_tem:

=clkinxorclk_tem;

--反馈

process(qout1)

--四分频

integerrange0tocounter_len;

ifqout1'

eventandqout1='

ifcnt=counter_lenthen

ifcnt<

=1then

clk_tem<

endbehave;

图8:

图9:

以上介绍了三种设计50%占空比三分频器的方法,由以上看出,第三种设计方法,程序最简洁,占用宏单元最少,而且可以举一反三,很容易设计出其他奇数分频占空比为50%的分频器。

(作者:

徐刚)

libraryieee;

useieee.std_logic_1164.all;

useieee.std_logic_unsigned.all;

ENTITYOdd_Frenis

port(Clk:

instd_logic;

O

outstd_logic);

endOdd_Fren;

architecturebevofOdd_Frenis

signalO_r,O_d

std_logic_vector(1downto0):

="

00"

signalO_ro,O_do,O_x:

std_logic:

='

signalO_t

begin

P1:

PROCESS(Clk,O_r)

if(Clk'

eventandClk='

)then

caseO_ris

when"

01"

=>

O_ro<

O_r<

=O_r+1;

10"

whenothers=>

endcase;

endPROCESS;

P2:

PROCESS(Clk,O_d)

caseO_dis

O_do<

O_d<

=O_d+1;

O_x<

=O_roxorO_do;

P3:

PROCESS(O_x)

if(O_x'

eventandO_x='

O_t<

=notO_t;

O<

=O_t;

endbev;

-----------------------------------------------------------------------------------------------

ENTITYtst_Odd_Frenisend;

architecturetestoftst_Odd_Frenis

COMPONENTOdd_Frenis

port(Clk:

endCOMPONENT;

signalClk:

signalO

U0:

Odd_Frenportmap(Clk,O);

PROCESS

Clk<

waitfor50ns;

endtest;