Spartan3E中文用户指南 非常有用Word格式.docx

《Spartan3E中文用户指南 非常有用Word格式.docx》由会员分享,可在线阅读,更多相关《Spartan3E中文用户指南 非常有用Word格式.docx(93页珍藏版)》请在冰豆网上搜索。

XC2C64ACoolRunner-IICPLD

Chapter17:

DS24321-WireSHA-1EEPROM

Chapter1:

IntroductionandOverview

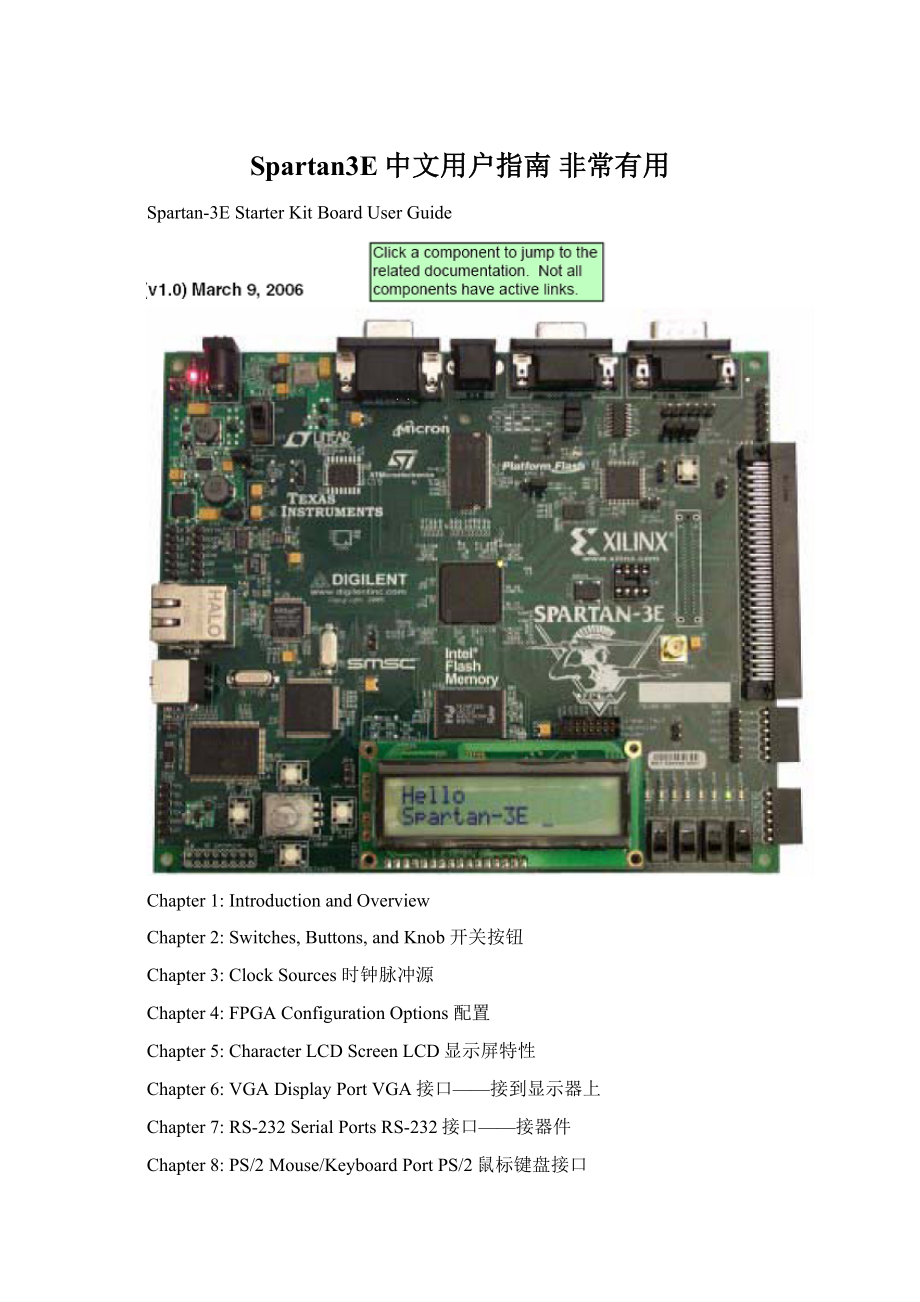

Spartan-3E入门实验板使设计人员能够即时利用Spartan-3E系列的完整平台性能。

设备支持:

Spartan-3E、CoolRunner-II

关键特性:

Xilinx器件:

Spartan-3E(50万门,XC3S500E-4FG320C),CoolRunner™-II(XC2C64A-5VQ44C)与PlatformFlash(XCF04S-VO20C)

时钟:

50MHz晶体时钟振荡器

存储器:

128Mbit并行Flash,16MbitSPIFlash,64MByteDDRSDRAM

连接器与接口:

以太网10/100Phy,JTAGUSB下载,两个9管脚RS-232串行端口,PS/2类型鼠标/键盘端口,带按钮的旋转编码器,四个滑动开关,八个单独的LED输出,四个瞬时接触按钮,100管脚hirose扩展连接端口与三个6管脚扩展连接器

显示器:

VGA显示端口,16字符-2线式LCD

电源:

LinearTechnologies电源供电,TPS75003三路电源管理IC

市场:

消费类,电信/数据通信,服务器,存储器

应用:

可支持32位的RISC处理器,可以采用Xilinx的MicroBlaze以及PicoBlaze嵌入式开发系统;

支持DDR接口的应用;

支持基于Ethernet网络的应用;

支持大容量I/O扩展的应用。

ChoosetheStarterKitBoardforYourNeeds

Spartan-3EFPGAFeaturesandEmbeddedProcessingFunctions

Spartan3-EFPGA入门实验板具有Spartan3-EFPGA系列突出独特的特点和为嵌入式处理发展与应用提供了很大的方便。

该板的特点如下:

Spartan3-E特有的特征:

并行NORFlash配置;

通过并行NORFlashPROM实现FPGA的多种配置方式

嵌入式系统:

MicroBlaze™32-bit嵌入RISC处理器;

PicoBlaze™8-bit嵌入控制器;

DDR存储器接口

LearningXilinxFPGA,CPLD,andISEDevelopmentSoftwareBasics

Spartan3-EFPGA入门实验板比其他的入门实验板先进、复杂。

它是学习FPGA或CPLD设计和怎样运用ISE软件的基础。

AdvancedSpartan-3GenerationDevelopmentBoards

入门实验板示范了MicroBlaze™32-bit嵌入式处理器和EDK的基本运用。

其更先进的地方在于配了额外的外设和FPGA逻辑,包括SP-305入门实验板。

KeyComponentsandFeatures

主要特征:

1)XC3S500E(Spartan-3e):

多达232个用户I/O口;

320个FPGA封装管脚;

超过10000个逻辑单元。

2)4Mbit的Flash配置PROM;

3)64个宏单元的XC2C64ACoolRunnerCPLD;

4)64MByte(512Mbit)ofDDRSDRAM,×

16数据接口,100+MHz;

5)16MByte(128Mbit)of并行NORFlash(IntelStrataFlash):

FPGA配置存储;

MicroBlaze代码存储/映射;

6)16MbitsofSPIserialFlash(STMicro):

7)16字符-2线式LCD显示屏;

8)PS/2鼠标或键盘接口;

9)VGA显示接口;

10)10/100以太PHY(要求FPGA内部具有以太MAC);

11)2个9-管脚的RS-232端口(DTE和DCE两种类型);

12)FPGA/CPLD下载/调试USB接口;

13)50Hz时钟晶振;

14)1线式的SHA-1位流复制保护串行EEPROM;

15)HiroseFX2扩展连接口;

16)3个管脚扩展连接器;

17)4个SPI-DAC转换器输出管脚;

18)2个SPI带可编程增益ADC输入管脚;

19)ChipScope™软件调试接口;

20)带按钮的旋转编码器;

21)8个单独的LED输出;

22)4个滑动开关;

23)4个按钮开关;

24)SMA时钟输入;

25)8管脚插槽辅助晶振

DesignTrade-Offs

ConfigurationMethodsGalore!

FPGA的一个典型应用就是使用单永久性存储器来存储配置信息。

为了说明新的Spartan-3E的性能,入门实验板有3个不同的配置存储源,这需要一起正确使用。

额外的配置功能使入门实验板比典型的Spartan-3E应用更复杂。

入门实验板包括JTAG可编程USB接口。

片上的线路简化了器件的编程过程。

在典型的应用中,JTAG编程硬件在片外或在一个单独的编程模块上,如XILINXUSB电缆平台。

VoltagesforallApplications

入门实验板利用TI公司的TPS75003芯片(专门为Spartan-3E的FPGA提供电源)作为三态输出调整仪。

该调整仪适用多种FPGA的应用。

但是,入门实验板包括DDRSDRAM,这需要它自身快速的电流来供给。

简单地说,带USB接口的JTAG下载方式解决了需要单独配备1.8V电源的问题。

Chapter2:

Switches,Buttons,andKnob

SlideSwitches

LocationsandLabels

入门实验板具有4个滑动开关,如图2.1所示。

Operation

当开关关上或上拉时,FPGA的管脚连接3.3V电源,即逻辑高电平。

断开或下拉时,FPGA管脚接地,逻辑低电平。

一般开关的机械闭合时间为2ms,这里没有使用活动的回弹线路,尽管这种线路可以很容易地加到FPGA上。

UCFLocationConstraints

图2.2为4个滑动开关提供了UCF约束、I/O口分配和I/O口标准。

这里没有用到上拉电阻。

但是,当开关处于中间转换位置时,它被定义为输入。

Push-ButtonSwitches

入门实验板有4个瞬时按钮开关,如图2.3所示。

BTN_NORTH、BTN_EAST、BTN_SOUTH、andBTN_WEST。

注:

a所有的BTN_*按钮输入需要内部的下拉电阻;

b在一些FPGA应用中BTN_SOUTH作为软复位使用。

Operation

按下按钮,FPGA接到3.3v电源,如图2.4。

没有按下时,鉴于内部下拉电阻的原因,FPGA管脚产生一个逻辑低电平。

图2.5说明了怎样去定义下拉电阻的UCF。

这里按钮上没有活动的回弹线路。

在一些应用中,BTN_SOUTH按钮开关充FPGA选择复位功能的软复位。

图2.5为4个按钮开关提供了UCF约束、I/O口分配和I/O口标准。

并为每个输入管脚定义下拉电阻。

RotaryPush-ButtonSwitch

如图2.3所示,旋转按钮处4个分开的按钮的中间。

该开发产生3个输出:

2个轴状编码输出ROT_A和ROT_B。

中心的按钮是ROT_CENTER。

旋转按钮有2个不同的功能。

只要轴柄一转,按钮就旋转并输出值。

该轴也可以按下,和按钮开关一样。

Push-ButtonSwitch

按下握柄或按钮,则FPGA接通3.3V,如图2.6所示。

使用内部的下拉电阻产生低电平。

图2.9说明了怎样去定义UCF的下拉电阻。

RotaryShaftEncoder

首先,旋转编码更像是个连接到中心的凸轮。

旋转轴柄可操作两个按钮开关,如图2.7所示。

选择一个开关连接地,产生低电平。

当开关开时,FGPA内部的上拉电阻将该信号拉为高电平。

图2.9是对其UCF约束的描述,怎样去定义上拉电阻。

FPGA电路很方便地译码A和B的输入信号,但考虑到开关的机械特性,转换时会产生输入噪音。

如图2.8所示,噪音错误地报告额外的旋转事件或甚至报告旋转相反的方向。

DiscreteLEDs

入门实验板在滑动开关的上面有8个独立的贴片LED。

LED一端接地,另一端通过390欧的限流电阻接到Spartan-3E上。

要点亮一个LED,向相应的控制位置高。

ClockSources

Overview

图3.1所示,入门实验板支持3个主时钟输入源。

1)包括一个50MHz的时钟晶振

2)通过SMA连接器,时钟可以板外供应。

反之,FPGA也可以提供时钟信号或其它高速信号给SMA连接器

3)分列式8-DIP时钟晶振插槽

ClockConnections

每个时钟的输入直接连到Bank0的输入全局缓冲I/O。

表3.1所示,每个时钟输入也可以连接到相应的DCM。

VoltageControl

FPGA的I/OBank0的供给电压由跳线JP9控制。

因此,这些时钟源也是由JP9控制的。

默认情况下,JP9置为3.3v。

板上的晶振是3.3V的,如果JP9为2.5V,晶振的工作有可能达不到预期的效果。

50MHzOn-BoardOscillator

50MHz的晶振占空比为40%~50%之间。

其精度为±

2500Hz或±

50ppm。

AuxiliaryClockOscillatorSocket

如果FPGA需要除了50MHz外的频率,可以使用该8管脚的插槽。

另外,也可以使用FPGA的DCM来产生,或者从板上的50MHz晶振结合其它频率来获得。

SMAClockInputorOutputConnector

连接输入时钟信号到SMA连接器可以从外部提供一个时钟。

FGPA也可以在SMA上产生一个单端的时钟输出信号或高速信号给外部器件。

UCFConstraints

Location

ClockPeriodConstraints

Chapter4:

FPGAConfigurationOptions

入门实验板支持多种FPGA的配置方法:

通过JTAG、USB接口直接将设计下载到FPGA。

板上的USB-JTAG逻辑也提供对PlatformFlashPROM和XilinxXC2C64ACPLD的在线编程。

对板上的4MbitXilinxXCF04SserialPlatformFlashPROM进行编程,然后采用主串行模式对PlatformFlashPROM上的存储信息配置到FPGA。

对板上的16MbitSTMicroelectronicsSPIserialFlashPROM进行编程,然后采用SPI模式对SPIserialFlashPROM上的存储信息配置到FPGA。

对板上的128MbitIntelStrataFlashparallelNORFlashPROM进行编程,然后采用BPIUp或BPIDown对StrataFlashparallelNORFlashPROM上的存储信息配置到FPGA。

接着,可以采用Spartan-3EFPGA’sMultiBoot模式以两种不同的配置方式对一个FPGA进行轮流下载。

图4.1给出了USB下载/编程接口和永久存储器的位置。

图4.2是多种配置方式的一些细节内容。

当上电或PROG按钮被按下时,跳线的配置方式决定了FPGA采用哪种配置方式。

当FPGA成功配置时,DONE管脚的LED亮。

4MbitXilinxPlatformFlashPROM为FPGA的JTAG提供了一个简单的可编程配置存储单元。

来自PlatformFlashPROM的FPGA配置采用主串行模式。

采用BPIUp、BPIDown或MultiBoot配置方式以及StrataFlashparallelFlashPROM对FPGA进行下载时,64-macrocellXC2C64ACoolRunnerIICPLD为其提供了额外的存储空间。

CPLD由用户自己编程。

ConfigurationModeJumpers

如表4.1所示,由J30的设置方式来控制FPGA的配置方式。

PROGPushButton

PROG按钮,迫使FPGA进行重新配置。

只要按下该按钮,FPGA就重新进行配置。

DONEPinLED

当FPGA成功配置时,DONE管脚的LED亮,如果不亮说明配置失败。

ProgrammingtheFPGA,CPLD,orPlatformFlashPROMviaUSB

正如图4.1所示,入门实验板包含了内嵌式USB可编程逻辑和B型连接器的USB接口。

通过USB电缆可将其连到主机的iMPACT可编程软件对FPGA、PlatformFlashPROM或CPLD进行直接编程。

对于并行或串行的FlashPROM并暂时不支持直接编程。

ConnectingtheUSBCable

实验板包含一个标准的USBA/B型的电缆,如图4.3所示。

其中,A型的连接口接到PC上,B型接口接到板上。

上电时,Windows操作系统通过安装相应的驱动软件即可识别。

绿色的LED亮表示USB连接正常。

ProgrammingviaiMPACT

通过iMPACT和USB电缆将编译成功的FPGA设计下载到FPGA上。

将USB电缆连到板子并给其上电,然后双击ProjectNavigator的ConfigureDevice(iMPACT),如图4.5所示。

只要板连接正确,iMPACT就会自动识别JTAG编程文件,如图4.6所示。

如果没有即使识别出来,可以点击连接链的第一个芯片,然后右击FPGA,选择AssignNewConfigurationFile,如图4.6所示。

如果FPGA的源配置文件采用默认的启动时钟——CCLK,iMPACT会给出警告提示,如图4.7。

该警告可以忽略。

采用JTAG下载时,iMPACT必须的启动时钟必须改为TCKJTAG时钟源。

开始编程FPGA,右击FGPA,选择Program。

IMPACT在编程时会自动报告进程状态。

编程时间的长短取决于USB的接口和IMPACT的设置。

当FPGA编程成功时,IMPACT会显示成功,如图4.9所示。

此时,可以在板上执行FPGA了,还有DONE管脚点亮。

ProgrammingPlatformFlashPROMviaUSB

板上的USB-JTAG同样可以对XilinxXCF04SserialPlatformFlashPROM进行编程。

以下是如何产生PROM文件和如何下载到FPGA上的步骤。

GeneratingtheFPGAConfigurationBitstreamFile

在产生PROM文件之前,要先生成FPGA位流文件。

从外部的PROM下载到它自身时,FPGA提供了一个输出时钟—CCLK。

FPGA内部的晶振CCLK的振动频率较慢,大约1.5MHz。

大多数的外部PROM支持高频率时钟。

增加CCLK的频率等同于减少FPGA的配置时间。

XilinxXCF04SPlatformFlash支持25MHz的CCLK频率。

如图4.10所示。

接着如图4.11所示进行相应的操作。

接下来如图4.12所示。

GeneratingthePROMFile

产生程序文件之后,进行如图4.13所示的操作。

启动IMPACT之后,双机PROMFileFormatter,如图4.14所示。

接下来如图4.15、4.16、4.17、4.18进行相应的操作。

PROM成功配置后,IMPACT显示位流文件占用PROM的存储空间,如图4.19所示。

要生成可执行PROM文件,点击Operation/GenerateFile,如图4.20所示。

IMPACT将指出PROM文件成功产生,如图4.21所示。

ProgrammingthePlatformFlashPROM

下面是通过USB-JTAG连接电路将PROM文件编程到PlatformFlashPROM的简要步骤。

具体如图4.22~4.25所示。

在编程之前,如图4.26选择编程选项。

检查EraseBeforePrograming选项,在编程之前完全擦除PlatformFlashPROM,确保没有残余数据。

Verify选项用来检查PROM正确编程和匹配下载配置位流文件。

一般推荐这两个选项,即使是增加编程时间。

LoadFPGA选项在PlatformFlashPROM编程后立即强制重新配置FPGA。

FPGA的配置模式必须选主串行模式(见表4.1),点击OK完成。

IMPACT会指出编程成功与否。

如果编程成功而LoadFPGA选项没有检查,按下PROG_B按钮空开关强制FPGA从PlatformFlashPROM重新进行配置。

如果FPGA成功配置,DONELED点亮。

Chapter5

CharacterLCDScreen

入门实验板显著的特征是2线16字符液晶显示器LCD。

尽管LCD支持8位的数据接口,为了与其它的XILINX的开发板保持兼容并且尽可能减少针脚数,FPGA仅通过4位的数据接口线控制LCD,如图5.1所示。

LCD通过使用ASCII标准和自定义字符可以有效地显示多种信息。

但是,这些显示速度并不是很快。

每半秒扫描一次以测试实际清晰度的界限。

与50MHz时钟频率相比,这样的显示速度是慢的。

PicoBlaze处理器可以有效地控制显示时间和显示内容。

CharacterLCDInterfaceSignals

表5.1给出了字符LCD接口的接口信号。

VoltageCompatibility

字符LCD的供电电压是+5V。

FPGA的I/O口信号的电压是3.3V。

但是,FPGA的输出电平是通过LCD来识别是有效的低电平还是高电平。

LCD控制器接收5VTTL信号电平,FPGA输出3.3V的LCMOS以满足5VTTL电压要求。

数据线上的390欧串联电阻,当LCD驱动一个逻辑高电平时,其用来防止了FPGA和SrtataFlsahI/O管脚的超负载。

当LCD_RW为高时,LCD驱动数据线。

在绝大多数应用中,LCD作为只读外围设备,几乎没有从显示器读数据。

InteractionwithIntelStrataFlash

如图5.1所示,4根LCD数据线与StrataFlash数据线SF_D<

11:

8>

复用。

正如表5.2所示,LCD/StrataFlash存储器依赖于设计而交互使用。

当存储器失能时(SF_CE0=1),FPGA用作全读/写通道给LCD。

相反,当LCD读失能时(LCD_RW=0),FPGA用作全读/写通道给存储器。

要是StrataFlash存储器为字节宽度×

8模式(SF_BYTE=0),FPGA作为全同步读/写通道给LCD和存储器。

在字节模式下,存储器没有用到SF_D<

15:

数据线。

LCDController

该2×

16字符LCD内嵌一个SitronixST7066U图形控制器。

其功能与下面几个一样:

SamsungS6A0069XorKS0066U、HitachiHD44780和SMOSSED1278。

MemoryMap

该控制器有三个内部存储空间,每个都有专门用途。

送数据给这些空间之前必须初始化。

1)DDRAM

显示数据RAM(DDRAM)存储字符编码。

绝大多数应用中,都是与DDRAM相结合的。

存储在DDRAM中的字符编码所涉及的特定的字符位图要么存在CGROM字符设置中,要么存在用户自定义的CGRAM的字符设置中。

图5.3给出了显示器32位字符位置的默认地址。

字符的最上行存储在地址0X00与0X0F之间。

第二行的字符存储在地址0X40与0X4F之间。

从物理上讲,DDRAM一共有80个字符位置,每行有40个字符。

位置0X10到0X27和0X50到0X67之间的地址用来存储其它非显示数据。

此外,这些位置也可以存储只有使用控制器的显示移位功能才能显示的字符。

往DDRAM读或写之前,DDRAM地址命令得初始化地址计数器。

写DDRAM数据使用写数据到CGRAM或DDRAM命令,读DDRAM使用从CGRAM或DDRAM命令读数据。

DDRAM地址计数器要么在读或写之后保持常数,要么自动增加1或自动减1。

2)CGROM

字符产生器ROM(CGROM)包括每个事先定好的字符的字体位图,这样LCD屏才能显示,如图5.4。

字符编码存储在DDRAM中,每个字符的位置与CGROM的位置按顺序对应。

例如,0X53的一个16进制的字符编码存储在DDRAM中的位置显示字符是“S”。

0X53最上面的